Fターム[5J081CC46]の内容

LC分布定数、CR発振器 (9,854) | 目的、効果 (1,425) | 生産性向上(バラツキ低減等を含む) (35)

Fターム[5J081CC46]に分類される特許

1 - 20 / 35

発振回路及び電子機器

【課題】発振周波数が安定するまでに要する時間の短い発振回路及び電子機器を提供する。

【解決手段】周波数補正回路を有する共振回路と、前記共振回路の両端の間に接続された増幅回路とを備えた発振回路が提供される。前記周波数補正回路は、第1のコンデンサと、両端の電位が変動可能に前記第1のコンデンサと直列的に接続された第1のトランジスタと、を有することを特徴とする。

(もっと読む)

半導体集積回路装置および発振周波数較正方法

【課題】発振器の発振周波数の較正作業を短縮することができる半導体集積回路装置および発振周波数較正方法を提供する。

【解決手段】DCO50と、温度に対して単調な特性を持って変化する電圧源20から得られる電位に応じたDCO50に設定すべき発振周波数の温度係数および発振周波数の絶対値を記憶する記憶部42と、を備えたことを特徴とする半導体集積回路装置。

(もっと読む)

プリントインダクタおよびその製造方法ならびに電圧制御発振器

【課題】プリントインダクタのQ値を高く設定してもその形成面積を小さくすることができるなどの新規のプリントインダクタおよびその製造方法ならびに電圧制御発振器を提供する。

【解決手段】本実施形態のプリントインダクタ1は、第1のインダクタパターン10、第2のインダクタパターン20および接続部材30(例えば、第3のインダクタパターン30A)を備えている。第2のインダクタパターン20(または第1のインダクタパターン10)における遠方部分20a(または10a)の幅寸法は、その近接部分20b(または10b)の幅寸法よりも小さくなるように形成されている。

(もっと読む)

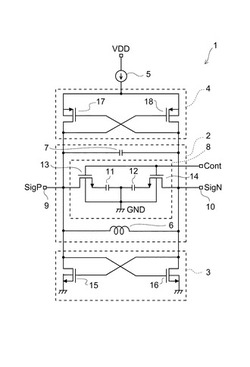

電圧制御発振器

【課題】電界効果トランジスタのドレイン−ソース間容量のばらつきによる位相誤差を低減しつつ、位相が互いに90°ずつ異なる発振信号を生成する。

【解決手段】電界効果トランジスタM1のドレインと電界効果トランジスタM2のドレインとの間にインダクタL1を接続し、電界効果トランジスタM3のドレインと電界効果トランジスタM4のドレインとの間にインダクタL2を接続し、インダクタL1にインダクタL3を磁気的に結合し、インダクタL2にインダクタL4を磁気的に結合し、インダクタL3の一端とインダクタL4の一端とをコンデンサC1を介して容量結合し、インダクタL3の他端とインダクタL4の他端とをコンデンサC2を介して容量結合する。

(もっと読む)

高周波帯電圧制御発振器

【課題】共振回路における発振周波数の公差を低減し、PLL回路に用いられる論理回路の低電圧化傾向の下でも、発振周波数の高周波化を図る。

【解決手段】発振周波数を可変制御するLC同調型の電圧制御発振器において、発振用トランジスタ1のエミッタ側で、接地電位となる一対のスルーホールH1 ,H2 の間に、同一線路長のマイクロストリップ線路からなる2つのショートスタブP1 ,P2 を形成し、これらショートスタブP1 とP2 との間に上記トランジスタ1のエミッタを接続する。即ち、ショートスタブP1 とP2 は、エミッタ接続点を中心に対称となる位置で並列に接続される。また、コンデンサC1 ,C2 でDCカットされたバラクタCvのカソードに、0〜5Vの制御用電圧Vtを印加すると共に、アノードに、基準電圧源6から例えば−5Vの基準電圧を印加する。

(もっと読む)

インダクタを備えた半導体集積回路

【課題】半導体集積回路をパッケージに実装した後に、インダクタンスを増加および減少させる調整が可能な半導体集積回路を提供する。

【解決手段】LSIの内部回路106が形成された同一の半導体基板に磁気検出素子100が形成されており、ボンディングパッド114とLSIの内部回路106の間に接続された第1インダクタ101のインダクタンスを磁気検出素子100と磁気検出回路105の出力電圧でモニタし、第1インダクタ101の片方の端子と第2インダクタ102の一端と第3インダクタ103の一端が第1接続部107を介して接続される第1スイッチ108、第2インダクタ102の片方の端子が第2接続部109を介して接続される第2スイッチ110、および、第3インダクタ103の片方の端子が第3接続部111を介して接続される第3スイッチ112を接続または切断状態に切り替えることにより、第一のインダクタ101をトリミングする。

(もっと読む)

電圧制御発振器

【課題】電源電圧に重畳されたノイズにより発生する発振器の位相雑音を低減することができ、しかも簡単な回路構成で実現でき、発振器の小型化を図ることのできる電圧制御発振器を提供すること。

【解決手段】この電圧制御発振器1は、直流電源端子16にコレクタが接続された発振用トランジスタ11と、発振用トランジスタ11のエミッタ・接地間に接続された第1の抵抗21と、発振用トランジスタ11のベース・接地間に接続された共振回路27と、発振用トランジスタ11のエミッタと第1の抵抗21との接続点と直流電源端子16とを接続する結合ラインL1上に設けられた第1のキャパシタ22とを具備することを特徴とする。

(もっと読む)

マイクロ波発振素子及びマイクロ波発振装置

【課題】マイクロ波発振素子及びマイクロ波発振装置に関し、複雑な成膜工程や微細加工の必要がない簡単な素子構造によりマイクロ波発振を可能にする。

【解決手段】強磁性体層11とスピン軌道相互作用を有する金属層12との積層構造からなり、金属層両端の端子131、132との間に電源14から電圧を印加して、金属層12に電流を流す事で、スピンホール効果により金属層12から強磁性体層11へ純スピン流が注入され、マイクロ波発振を励起する。

(もっと読む)

基準周波数制御回路

【課題】 基準周波数を生成する発振回路の発振周波数の変化を抑制可能な基準周波数制御回路を提供する。

【解決手段】 入力信号のレベルに応じた周波数で発振する発振回路からの発振信号が入力され、前記発振信号の周波数に応じた出力電圧を出力する周波数電圧変換回路と、前記出力電圧が所定レベルとなるよう前記入力信号のレベルを制御する制御回路と、を備えることを特徴とする基準周波数制御回路。

(もっと読む)

半導体発振回路および携帯電話

【課題】基準周波数生成回路は、ロジック回路の電源ノイズの影響を受けて、周波数偏差やピリオドジッターの悪化を引き起こしていた。

【解決手段】CPUや周辺回路などのロジック回路12の電源はレギュレータ13より供給し、基準周波数生成回路11の電源には電源の高周波ノイズを10dB以上の減衰量を持つローパスフィルター10を介してから供給する。これによりロジック回路12で発生する高周波ノイズ起因での周波数偏差やジッターの悪化を抑えることができ、この基準周波数をUARTシリアル回路に接続して通信ができる。

(もっと読む)

発振器

【課題】周波数を高くしても分布定数線路の線路長を長くできてQ値を向上できるとともに、製造誤差を小さく抑えることができる発振器を提供する。

【解決手段】1波長の線路長であって、両端をグランドに接地した分布定数線路16を有し、この分布定数線路16の一端から1/4波長の位置に設けた第1の中間タップに発振トランジスタ27のべースを接続するようにした。これにより、分布定数線路16の線路長が従来の1/4波長の線路長の分布定数線路より長くなり、その分Q値の向上が図れるとともに、製造誤差を小さく抑えることが可能となる。分布定数線路16の長さを1/2波長としても従来の1/4波長の長さの分布定数線路に比べて2倍長くできる。このようにしてもQ値の向上が図れ、また製造誤差を小さく抑えることが可能となる。

(もっと読む)

誘電体共振器型発振器及びそれを用いたレーダシステム

【課題】誘電体共振器型発振器(DRO)の量産においては、誘電体共振器を設置する位置を高い精度で調節する必要があり、組立作業に要する時間が増大してしまう。また、誘電体共振器と電磁的に結合させ、共振器を構成する伝送線路の先端の終端抵抗および接地手段を誘電体基板上に形成すると製造コストが高くなる。

【解決手段】DROの構成部品のうち、伝送線路のみを誘電体基板上に形成し、MMICチップ上の発振用能動素子、終端抵抗および接地手段を伝送線路と金属ワイヤ、金属リボン等で接続する。また、誘電体共振器から見て発振用能動素子側の伝送線路の中途に、オープンスタブを形成する。

(もっと読む)

発振器の製造方法、及び発振器

【課題】共振状態における電磁波損失が低減され、出力を向上させることが可能な発振器の製造方法、及びその発振器を提供することである。

【解決手段】発振器の製造方法により、発振電磁波に対して利得を有する利得媒質202と電磁波を共振させるための共振器構造を備え、共振器構造が電磁波の伝播方向と垂直な方向を閉じ込めるための導波管構造を有する発振器が製造される。第1の基板200に、利得媒質202を含む半導体多層膜をエピタキシャル成長する。第1の基板200、または第1の基板とは別の第2の基板209に、当該溝205の断面形状で規定されるカットオフ周波数が電磁波の周波数より小さくなる様な形状の溝205を形成する。第1の基板200と第2の基板209によって溝205が挟まれて導波管構造を構成する様に第1の基板と第2の基板を貼り合わせる。

(もっと読む)

温度安定化発振器及び同発振器を含む近接スイッチ

【課題】発振器の温度依存性を簡単に安定化すると共に、大きな切換え距離を有して広い温度範囲に渡って安全に機能する近接スイッチの簡単で低コストの製造を可能にする。

【解決手段】共振回路L,C,RCUと仮想負性抵抗として接続される増幅器回路V,R1,R2,R3を含む発振器において、直流電流源I1は、共振回路L,C,RCUと直列に接続されている。こうして、発振器回路コイルLの抵抗の尺度である電流UCUがもたらされる。この信号UCUを使用することによって、制御回路V1,Mは、発振器回路コイルLの抵抗RCUに逆比例する仮想負性抵抗を制御する。

(もっと読む)

高周波装置の製造方法

【課題】基板に紙系の基材を用いても発振器の発振周波数の変動が少ない高周波装置を提供する。

【解決手段】紙基材の基板22上にはチップコンデンサ23と空芯コイル24とが搭載され、チップコンデンサ23は鉛フリー半田25で接続され、空芯コイル24は鉛フリー半田27で接続される。基板22上の空芯コイル24によって発信器7が形成され、この発信器7は空芯コイル24によって発振周波数が調整される。そして、鉛フリー半田25を溶かすための1回目のリフロー工程53における基板22のピーク温度と、鉛フリー半田27を溶かすための2回目のリフロー工程57における基板22のピーク温度との和の温度を475℃以下とする。これにより、チューナ1の吸湿による発信器7の周波数変動が小さくできる。

(もっと読む)

インダクタと、このインダクタを用いた高周波装置、およびこの高周波装置の製造方法

【課題】インダクタコイルの高さが高く、高周波装置の薄型化が困難である。

【解決手段】基板21と、この基板21に設けられた接続端子25aと接続端子25bと、この接続端子25aと接続端子25bとの間を連結するように基板21上に装着されたインダクタ導体22とを設け、インダクタ導体22と接続端子25aとの間およびインダクタ導体22と接続端子25bとの間は共にはんだ32によって接続されたものである。これにより、インダクタは基板上にインダクタ導体が装着されることによって形成されるので、薄い高周波装置を実現できる。

(もっと読む)

高周波モジュール

【課題】基板の誘電体層と電極層の僅かな焼成縮率の差により基板焼成後、基板に反りが発生する。この反りが大きくなると、印刷性が悪くなり、かつ印刷するパターンかすれや、にじみが発生し、場合によっては印刷時にスクリーンが破れたりする。

【解決手段】少なくとも、ストリップライン導体7と、複数のGND電極と、複数のコンデンサを内蔵すると共に、前記ストリップライン導体7に対し、積層方向の両側に、GND電極3、4を配置してトリプレート型ストリップライン導体共振器を構成した高周波モジュールにおいて、前記トリプレート型ストリップライン導体共振器に対し、積層方向の上側(部品搭載面側)と下側(底面側)の双方に、それぞれGND電極3、4からなるコンデンサを配置した。

(もっと読む)

発振器用基板

【課題】VCXOとPXOとに共有可能な印刷抵抗を使用した発振器用基板を提供する。

【解決手段】水晶振動子Y1と水晶発振回路11とから構成されるPXO、または圧電発

振回路と周波数電圧制御回路12とから構成されるVCXOに使用可能な発振器用基板で

あって、VCXOを構成する抵抗部品のうち、短絡部品に交換することによりVCXOを

PXOに変更できる抵抗R2以外を印刷抵抗により形成した。これにより1つの発振器用

基板21をVCXOとPXOにおいて共有して使用することができるため、発振器の低コ

スト化を実現することができる。また、VCXOをPXOに変更するための抵抗R2以外

を印刷抵抗により形成しているため圧電発振器を小型化することが可能になる。

(もっと読む)

誘電体共振器,発振器,フィルタ,高周波モジュール及び誘電体共振器の共振周波数調整方法

【課題】共振周波数調整用部材を形成するための専用の工程を必要とせず、しかも、共振周波数を微調整することができるだけでなく、短時間で大きく変化させることができ、さらに、共振周波数を下げる方向と上げる方向との両方向に調整可能な誘電体共振器,発振器,フィルタ,高周波モジュール及び誘電体共振器の共振周波数調整方法を提供する。

【解決手段】誘電体共振器1は、誘電体基板2と、開口部30A,30Bを有した電極板3A,3Bと、開口部30A(30B)内に配された第1電極4及び第2電極5とを備える。第1電極4は、電界の強さが最大となる個所にその電気力線に沿って配設され、第2電極5は、磁界の強さが最大となる個所にその磁力線を遮るように配設される。レーザ光で第1電極4を除去することで、共振周波数を上昇させ、第2電極5を削ることで、共振周波数を下降させることができる。

(もっと読む)

誘電体共振器、発振器、及び、誘電体共振器の製造方法

【課題】特性の安定した誘電体共振器、及び、発振器を提供する。

【解決手段】 平板状セラミック誘電体からなる誘電体共振器であって、

4角形以上の多角形の平面形状を有しており、その角部が丸められている。

(もっと読む)

1 - 20 / 35

[ Back to top ]