Fターム[5J081EE03]の内容

LC分布定数、CR発振器 (9,854) | 周波数決定素子 (1,325) | 集中定数 (802) | C (374)

Fターム[5J081EE03]に分類される特許

361 - 374 / 374

電圧制御発振器、及び無線通信機器

【課題】 電界効果トランジスタを用いる電圧制御発振器において、電源電圧変動に伴う発振周波数の揺れを小さくするためにバックゲート端子をソースに接続すると、基板ロスが大きくなり位相雑音特性が劣化する。

【解決手段】 発振トランジスタ115のバックゲート端子を、高インピーダンス素子119を介してソース端子に接続し、発振トランジスタ116のバックゲート端子を、高インピーダンス素子120を介してソース端子に接続する。

(もっと読む)

Qエンハンスメント回路および方法

Qエンハンスメント回路および方法である。ほとんどの一般的な実施形態において、本発明の回路は寄生抵抗Rを有するコンポーネントにより使用されるように構成され、第1の抵抗R1がこのコンポーネントと直列に配置され、この構成により抵抗R1は負性抵抗になる。示されている実施形態において、第1および第2のインダクタは、Qエンハンスメントが行われるコンポーネントを構成する。抵抗R1は第1のインダクタと直列に配置され、その寄生抵抗RL1と等しい。同様に、第2の抵抗R2は第2のインダクタと直列に配置され、その寄生抵抗RL2と等しい。Qエンハンスメント回路はさらに第1のトランジスタQ1および第2のトランジスタQ2を備えている。 (もっと読む)

LC発振器

LC発振器(1)は、一対のコンデンサ(Cva,Cvb)及び一対のインダクタンス(La,Lb)が結合される交差結合されたPMOSトランジスタ対(Ma,Mb)を有する。発振器の信号増幅を向上させるために、各々のPMOSトランジスタのドレインと、好ましくはソースとの間に結合される一対の補助トランジスタ回路(Qa,Qb;Na,Nb)が設けられる。同調範囲を拡大することを可能にするためにコンデンサ(Cva,Cvb)は好ましくは可変コンデンサであり、インダクタンス(La,Lb)は好ましくはグランドに接続される。  (もっと読む)

(もっと読む)

高周波発振器

【課題】 簡素な構造で、優れたQ値、およびC/N特性を有し、負荷特性に優れる高周波発振器を構成する。

【解決手段】 高周波発振器は、共振回路10と、該共振回路10に接続するとともに出力端子OUTに接続する帰還増幅回路1とを備える。帰還増幅回路1は、ベースが共振回路10に接続し、コレクタがインダクタL11を介して駆動電源端子Vbに接続するとともにコンデンサC2を介してグランドに接続することにより高周波的に接地し、エミッタがエミッタ抵抗R1、インダクタL1の直列回路とコンデンサC1とを介してグランドに接続し、ベース−エミッタ間に帰還用コンデンサC3が接続した発振用トランジスタTr1を備える。この発振用トランジスタTr1のベースがバイアス抵抗R12を介して出力端子OUTに接続する。

(もっと読む)

温度安定化された電圧制御発振器

セルラー電話のような電池から電力を得る装置中の集積回路電圧制御発振器(VCO)は、比較的狭い制御電圧範囲を使用して非常に広い周波数範囲にわたって同調するように構成されることができる。VCOの周波数応答は、VCO共振回路の一部を形成するバラクタ310a-310bに温度可変電圧ソースを与えることにより温度補償されることができる。バラクタのレファレンス端部は、バラクタ温度依存性を実質的に補償する温度依存性を有する温度依存電圧ソース370、380により供給されることができる。温度依存電圧ソース370,380は、絶対温度比例(PTAT)装置であることができる。VCOは、基板上に製造されたCMOS発振器、基板上のLC共振タンク、および共通の陽極接続を有する少なくとも一対のバラクタ310a、310b;320a、320bを含んでいる。 (もっと読む)

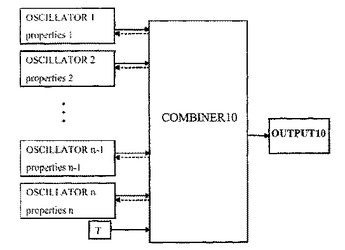

モノリシックなクロック・ジェネレータおよびタイミング/周波数リファレンス

電力節約モード、クロック・モード、リファレンス・モード、およびパルス化モードなどの複数の動作モードと共に、クロック・ジェネレータおよび/またはタイミングおよび周波数のリファレンスを提供する。共振周波数を有する第1の信号を供給するようになっている共振器と、増幅器と、温度に応じてこの共振周波数を修正するようになっている温度補償器と、製造プロセス変動に応じてこの共振周波数を修正するようになっているプロセス変動補償器とを含んでいる。さらに、実質的にこの共振周波数以下の対応する複数の周波数を有する複数の第2の信号に、この共振周波数を有する第1の信号を分周するようになっている周波数分割器と、これらの複数の第2の信号から1つの出力信号を供給するようになっている周波数セレクタとを含むことができる。  (もっと読む)

(もっと読む)

LC発振器を備えたPLLの粗チューニング時間の改良

LC発振器のチューニング方法と装置が開示されている。本発明の実施形態は、ビット比較時間を適応的に制御し、最少の粗チューニング時間が得られるようにすることを含んでいる。ビット比較時間は、LC発振器のキャパシタアレイ内の対応する加重キャパシタの冗長量に逆比例してスケーリングされる。 (もっと読む)

プログラム可能なトランシーバ

周波数およびプロトコルにとらわれない、デジタル入力および出力を有する無線周波数集積回路(RFIC)から構成される、完全統合型の、プログラム可能な混合信号トランシーバで、トランシーバは、複数の無線周波数帯域および規格にプログラム可能かつ構成可能で、多くのネットワークおよびサービスプロバイダに接続可能である。RFICは、インダクタンスと、第1の制御信号に応じて同調可能な共振回路にスイッチを入れられ切られるように構成される複数の切り替え可能なキャパシタと、第2の制御信号に応じて変更されることができる少なくとも1つの可変キャパシタとを有する伝送回線を含む同調可能な共振回路を含み、共振回路の共振中心周波数は、複数の切り替え可能なキャパシタの第1のキャパシタンス値と、少なくとも1つの可変キャパシタの第2のキャパシタンス値とを制御する第1および第2の制御信号に応じて電気的に同調可能である。  (もっと読む)

(もっと読む)

基準発振器の周波数安定化

従来技術の不利な点を取り除き、特性(1)高い長期安定性、(2)低位相雑音、(3)高耐熱性、(4)その基準発振器の周波数についての正確な値、を改善したMEMS基準発振器を提供することが、本発明の目的である。  (もっと読む)

(もっと読む)

電圧制御デジタルアナログ発振器およびこれを用いた周波数シンセサイザ

本発明は、発振器および周波数シンセサイザに関する。特に、電圧制御デジタルアナログ発振器およびこれを用いた周波数シンセサイザに関する。

本発明は、アナログ入力端に入力される電圧およびデジタル入力端に入力されるデジタル値によって出力信号の周波数が決定される発振器と、間欠的に前記アナログ入力端に入力される電圧を第1の閾値電圧および第2の閾値電圧と大小を比較し、その結果に応じて前記デジタル入力端に入力されるデジタル値を変化させるデジタル同調器と、を備える電圧制御デジタルアナログ発振器を提供する。また、これを用いた周波数シンセサイザを提供する。本発明に係る発振器および周波数シンセサイザは、雑音が少ないながらも、広帯域の周波数出力を得ることができる長所がある。

(もっと読む)

(もっと読む)

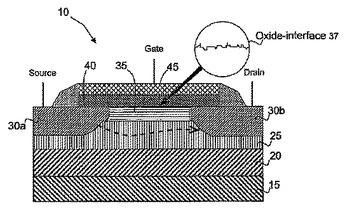

ストレインド・シリコン電圧制御発振器(VCO)

ストレインド・シリコン電圧制御発振器(VCO)は、ストレインド・シリコン層を有する第1Pチャネル金属酸化膜半導体(PMOS)装置を含み、ストレインド・シリコン層を有する第2PMOS装置に結合される。  (もっと読む)

(もっと読む)

マルチループ構成から形成されたインダクタンスループを有する集積回路パッケージ

集積回路パッケージが、リードワイアと1つまたは複数の入出力(I/O)パッケージピンとの接続から形成されるインダクタループを含む。一実施形態では、インダクタループは、集積回路チップ上の第1のボンディングパッドをパッケージの第1のI/Oピンに接続する第1および第2のワイアと、チップ上の第2のボンディングパッドをパッケージの第2のI/Oピンに接続する第3および第4のワイアとから形成される。インダクタループを完成するために、第1のI/Oピンと第2のI/Oピンは、ピン間の第3の導体によって接続される。第3の導体は、1つまたは複数のボンディングワイアを含むことができ、I/Oピンは、互いに隣接するものであることが好ましい。しかし、ループは、例えばループ長要件、空間の考慮すべき点、および/または他の設計要因もしくは機能要因に基づいて、I/Oピンの非隣接接続から形成することができる。他の実施形態では、第1のI/Oピンと第2のI/Oピンの間の接続が、I/Oピンに単一構造を持たせることによって確立される。他の実施形態では、第1のI/Oピンと第2のI/Oピンの間の接続が、パッケージ基板の表面上に、またはこの基板内に位置するメタライゼーション層によって確立される。集積回路パッケージの境界線内でインダクタループを形成することにより、空間要件における実質的な削減が実現され、これは小型化を促進する。また、集積回路は、その少なくとも1つのパラメータがパッケージのインダクタループの長さによって制御される様々なシステムのいずれか1つで実装することができる。

(もっと読む)

(もっと読む)

発振回路

【課題】 VCO発振周波数の調整を容易にする。

【解決手段】 VCO用共振回路が接続されるボンディングパッド5下のエピタキシャル層2Aの電位を、従来のフローティング状態から抵抗6を介して所定(Vcc)電位に固定することで、エピタキシャル層2Aの電位変化を速くして、寄生容量値が速やかに安定することから、電源ON時のドリフトが改善する。

(もっと読む)

発振回路

【課題】出力高調波が少なく安定性が高いフィルタ帰還型の特性を有し、発振周波数を広い範囲で制御することができる発振回路を提供する。

【解決手段】増幅回路10の出力は、周波数特性の異なる2つのバンドパスフィルタ13、14に分配回路11により所定の比率に分配されて供給される。バンドパスフィルタ13、14の出力は加算回路15により加算される。さらに、この加算後の出力は増幅回路10の入力に帰還され、この増幅回路10により増幅される。このような処理により、増幅回路10の出力の一部が入力側に正帰還され、所定周波数の信号の増幅が繰り返されて、所定周波数にて発振する出力信号Voutが生成される。このとき、制御回路12により、前記分配回路11によって分配される前記所定の比率を変更することにより、出力信号Voutの発振周波数が制御される。

(もっと読む)

361 - 374 / 374

[ Back to top ]