Fターム[5J081EE14]の内容

LC分布定数、CR発振器 (9,854) | 周波数決定素子 (1,325) | 複数の共振器・回路 (35)

Fターム[5J081EE14]に分類される特許

1 - 20 / 35

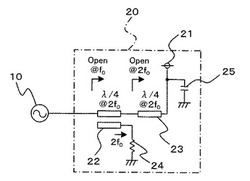

高周波発振器

【課題】小型に構成され、高調波と基本波との電力比を増加可能な高周波発振器を得る。

【解決手段】印加された電源電圧に基づいて、発振周波数の基本波で発振動作を行い、発振周波数の2倍波を出力する2倍波取り出し型発振器10と、2倍波取り出し型発振器10の出力端子に接続され、発振周波数の2倍波を通過帯域とする出力回路20とを備え、出力回路20は、2倍波取り出し型発振器10に電源電圧を供給する電源端子21と、2倍波取り出し型発振器10と電源端子21との間に直列に接続され、発振周波数の2倍波に対してほぼ1/4波長の長さを有する結合線路22と、2倍波取り出し型発振器10と電源端子21との間に直列に接続され、発振周波数の2倍波に対してほぼ1/4波長の長さを有する伝送線路23と、結合線路22の結合量に応じた出力電力を得る第1負荷抵抗24と、電源端子21に対して並列に接続されたキャパシタ25とを有する。

(もっと読む)

発振器

【課題】少ない電流で必要な負性抵抗が得られることにより、安定に動作することのできる発振器を提供する。

【解決手段】互いに並列に配設された容量素子134,234およびインダクタ133,233を有する共振回路13,23と、共振回路13,23の損失を打ち消す負性抵抗が生じるように配設された複数のトランジスタを有する負性抵抗発生器14,24と、第1バイアス端子15,25と、第2バイアス端子16,26と、を備えた複数の発振部10,20と、各共振回路13,23が互いに等価的に並列に接続されるように、複数の発振部10,20を電気的に結合する結合部30Aと、を備え、複数の発振部10,20は、それぞれの第1バイアス端子25および第2バイアス端子16において互いに直列に接続され、複数の発振部10,20における複数のトランジスタ143,144,243,244は、互いに同じ導電型で構成されている。

(もっと読む)

プッシュプッシュ発振器及び位相ずれ監視方法

【課題】位相ずれを確認する技術を提供する。

【解決手段】プッシュ・プッシュ発振回路100は、相互に逆位相で動作する、2つの発振器1、2と、2つの発振器1、2から出力された第1出力信号を合成する合成器101と、合成器101から出力された第2出力信号に含まれる第1出力信号の基本波を監視するための基本波監視回路102と、を備えている。即ち、基本波監視回路102を用いることで、合成器101から出力された第2出力信号に含まれる第1出力信号の基本波を確認することができる。第1出力信号の基本波を確認することで、合成器101に入力された2つの第1出力信号が逆位相であったか確認することができる。

(もっと読む)

弾性表面波発振器

【課題】設計段階で所望の微小な差周波を得られるようにすることと、2つの弾性表面波素子の共振周波数を同程度に近づけることとの両立を図る。

【解決手段】第1、第2SAW共振子2、4の両者における櫛歯電極12、13および反射器14、15を構成する各電極のピッチp1、p2を同一としつつ、両者における各電極の交差指幅L1、L2を異ならせる。第1、第2SAW共振子2、4をこのような構造とすることで、第1SAW共振子2を有する第1発振回路の発振周波数と、第2SAW共振子4を有する第2発振回路の発振周波数とを異ならせることができ、両方の発振周波数の差である差周波を微小な周波数に設定することが可能となる。

(もっと読む)

周波数可変共振器

【課題】小型でしかもQ値を向上させることが可能な周波数可変共振器を提供すること。

【解決手段】本発明一例の周波数可変共振器は、交流電源に一端を接続された第1のインダクタと、前記交流電源の他端にカソード端子を接続され、所定の直流電圧を印加される可変容量ダイオードと、この可変容量ダイオードのアノード端子に一端を接続され、他端を前記第1のインダクタの他端に接続され前記可変容量ダイオードに印加される逆バイアス電圧をカットする第1のコンデンサとからなる直列共振回路と、並列接続された第2のインダクタ及び第2のコンデンサからなり、前記第1のインダクタと第1のコンデンサとの接続点に一端を接続され、他端を前記可変容量ダイオードのカソード端子に接続され、前記直列共振回路の共振周波数とほぼ同じ共振周波数を有する並列共振回路と、を有する。

(もっと読む)

通信ネットワークにおける使用のための発振器、周波数シンセサイザ及びネットワークノード

本開示は、周波数シンセサイザ内での周波数の生成における使用のための発振器であって、少なくとも1つの巻きを伴って金属線ループを形成する第1の誘導素子と、前記第1の誘導素子との間で第1の共振回路を形成するように構成され、少なくとも1つの第1の接続端子を通じて前記第1の誘導素子と接続される第1の容量回路と、を備え、前記第1の容量回路は、少なくとも1つの容量素子、並びに、発振を確立し及び維持するように構成される電子コンポーネント配置を含む、発振器に関する。当該発振器は、少なくとも1つの容量素子と電子コンポーネントの配置とを含む第2の容量回路が、前記第1の誘導素子との間で第2の共振回路を形成するように構成され、前記第1の容量回路の前記第1の接続端子に対して前記第1の誘導素子の反対側に位置する少なくとも1つの第2の接続端子を通じて前記第1の誘導素子と接続されることと、前記第1及び第2の共振回路が実質的に同等の周波数にチューニングされることと、を特徴とする。本発明は、周波数シンセサイザ及び通信ネットワーク内での使用のためのネットワークノードにも関する。 (もっと読む)

半導体集積回路

【課題】良好な高周波特性を維持しつつ、増幅器の使用周波数帯域切換えが可能な半導体集積回路を提供する。

【解決手段】結合係数k1を有し、互いに並列に接続されるコイルL11及びコイルL12と、コイルL11及びコイルL12に直列に接続されるコイルL13と、コイルL11に並列に接続されるコンデンサC11と、コイルL12に並列に接続されるコンデンサC12と、コイルL11の一端と、コンデンサC11の一端とに接続される入力端子p1と、コイルL12の一端と、コンデンサC12の一端とに接続される入力端子n1と、入力端子p1と、入力端子n1とにそれぞれ逆位相の入力信号を供給する入力信号供給部200とから構成されることを特徴とする半導体集積回路。

(もっと読む)

電圧制御発振器

【課題】電界効果トランジスタのドレイン−ソース間容量のばらつきによる位相誤差を低減しつつ、位相が互いに90°ずつ異なる発振信号を生成する。

【解決手段】電界効果トランジスタM1のドレインと電界効果トランジスタM2のドレインとの間にインダクタL1を接続し、電界効果トランジスタM3のドレインと電界効果トランジスタM4のドレインとの間にインダクタL2を接続し、インダクタL1にインダクタL3を磁気的に結合し、インダクタL2にインダクタL4を磁気的に結合し、インダクタL3の一端とインダクタL4の一端とをコンデンサC1を介して容量結合し、インダクタL3の他端とインダクタL4の他端とをコンデンサC2を介して容量結合する。

(もっと読む)

クロック信号分配装置

【課題】高品質のクロック信号を分配することができるクロック信号分配装置を提供することを課題とする。

【解決手段】第1のインダクタ及び第1の容量に応じた周波数で共振して信号を発振する複数のLC共振発振器(302,303)と、第2のインダクタ及び第2の容量に応じた周波数で共振し、入力クロック信号に同期した信号を発振する注入同期型LC共振発振器(301)と、前記複数のLC共振発振器及び前記注入同期型LC共振発振器の発振ノードを接続する伝送線路(311,312)とを有することを特徴とするクロック信号分配装置が提供される。

(もっと読む)

周波数発生のための装置及び方法

広帯域周波数発生器は、フリップチップパッケージ内の同一のダイに配置された異なる周波数帯域のための2つ以上の発振器を有する。2つの発振器の誘導子間の結合は、一方の誘導子がダイに配置され、他方の誘導子がパッケージに配置され、これら誘導子がハンダバンプの直径によって離されることで、減少させられる。弱結合されたこれら誘導子では、一方の発振器の帯域を増加させるために他方の発振器のLCタンク回路の操作をしたり、その逆を行ったりできる。一方の発振器の振動の好ましくないモードを防ぐことは、他方の発振器の粗同調バンクの全容量といった大容量を他方の発振器のLCタンク回路に与えることによって達成され得る。好ましくないモードを防ぐことは、他方の発振器のLCタンクのQファクタを減少させ、タンク回路内の損失を増加させることによっても達成され得る。 (もっと読む)

電子回路

【課題】電子回路(例えば、マイクロコンピュータ)の動作モードに応じて、低周波数の発振器について適切な電源インピーダンスを設定することにより、前記発振器の誤動作を防止しながら、消費電力を適切に低減することができる。

【解決手段】システムクロックのクロック源として、高速発振器11、中速発振器12、低速発振器13が設けられる。また、時計用クロックを発生する水晶発振器30が設けられる。そして、高速発振器11が動作している時は、水晶発振器30の電源インピーダンスを低くして、耐ノイズ性を高める。一方、高速発振器11、中速発振器12、低速発振器13がすべて停止している待機時には、水晶発振器30の電源インピーダンスを高くして消費電力を抑える。

(もっと読む)

電圧制御発振器を用いた方法及び配置

【解決手段】自己注入同期電圧制御発振器の配置(1)では、一組の結合する第1及び第2電圧制御発振器(21,22)がチップ(2)上に配置され、増幅器(23)が同一の反射型チップ(2)上に配置され、オフチップ遅延線路(10)が、前記結合された第1及び第2電圧制御発振器(21,22)の外部端子に接続される一端子であって前記外部端子からの信号を反射するように適合された一端子で配列され、低位相雑音及び小型化を示すVCOの配置(1)を提供するために、増幅器(23)は、前記外部端子からの注入信号を増幅するため及び増幅された注入信号を前記第1及び第2電圧制御発振器(21,22)の一つに供給するために配置される。 (もっと読む)

位相同期発振器アレイ及びアレイアンテナ装置

【課題】分配器を用いることなく、位相同期した多数の発振信号を供給すること。

【解決手段】発振信号の位相差が90度である4位相の同一周波数の発振信号を出力する位相同期発振器アレイである。複数の閉線路21〜23から成る複数のリング共振器と、閉線路の全長を1/4分割した位置に設けられた4つのポート21a〜21dのうち隣接する2つのポート21b、21cと、この閉線路21に隣接する閉線路22の隣接する2つのポート22a、22d間を、それぞれ、負性抵抗として、接続する差動発振器31a、31bと、少なくとも何れか1方の端部に配置される閉線路21において、その閉線路の4つのポートのうち、差動発振器が接続されていない2つのポート21a、21dに対して、90度の位相差を有した信号を励振する励振装置30とを有する。

(もっと読む)

マイクロ波発振器

【課題】90度ハイブリッド回路を用いて、低周波の基本周波数から位相雑音特性に優れた高周波出力信号を効率よく取り出すことができるマイクロ波発振器を提供する。

【解決手段】第1の発振器1から基本周波数の第1の発振信号を出力し、第2の発振器2から第1の発振信号に対して逆位相となる基本周波数の第2の発振信号を出力する。90度ハイブリット回路HYB1が、第1の発振器1から出力された第1の発振信号と第2の発振器2から出力された第2の発振信号とを同位相で合成し、出力ポートP5から基本周波数f1の4倍周波数の高周波信号を出力する。このとき、基本周波数f1、2倍の周波数f2、及び3倍の周波数f3の振幅はゼロとなって出力されない。よって、基本周波数f1の4倍周波数の高周波信号は低位相雑音となって出力される。

(もっと読む)

LC発振器

【課題】発振信号の対称性などの制約が要求される場合においても、その制約を制御する自由度を向上させることができるLC発振器を提供する。

【解決手段】LC発振器は、並列に接続された第1のインダクタおよびキャパシタからなるLCタンク、ならびに、寄生抵抗の影響を打ち消す第1の負性抵抗回路を含む1次側のLC発振器と、相互インダクタンスを発生する相互誘導作用によって第1のインダクタと結合された第2のインダクタおよび第2の負性抵抗回路を含む2次側のLC発振器とを備える。ここで、第1および第2の負性抵抗回路の抵抗値の合計は、寄生抵抗の抵抗値以上であり、逆極性である。

(もっと読む)

発振器配置

本発明は、発振器出力、ならびに上記発振器出力の位相雑音の検出および/または制御を提供するために配置された発振器配置に関し、上記配置はローパスフィルタ(2)に接続された混合器(1)を含む。上記発振器配置は、第1の発振器(7)および第2の発振器(8)を含み、上記発振器(7,8)は、上記発振器出力が自動的に直交して得られるような方法で、少なくとも1つの結合要素(Q)によって相互にインターインジェクションロックされる。本発明は、対応する方法にも関する。 (もっと読む)

周波数合成回路、通信装置、周波数制御方法、周波数制御回路、周波数制御システム、およびコンピュータ読取可能な記録媒体

【課題】周波数合成器(200)の可変発振器(202)の出力信号の周波数を制御するシステムを提供する。

【解決手段】可変発振器(202)と周波数制御回路(208)を有する。可変発振器(202)は予め定められた周波数を有する出力信号を生成するために構成される。また可変発振器(202)は周波数制御回路(208)によって制御される複数の動作状態によって構成される。可変発振器(202)の動作状態のそれぞれは、可変発振器(202)の出力信号のための別個の周波数を決定する。周波数制御回路(208)は、可変発振器(202)の出力信号を受信し、予め定められた周波数に最も近い出力信号のための別個の周波数を決定する。また、周波数制御回路(208)は、可変発振器(202)へ、予め定められた周波数に最も近い別個の周波数に対応する動作状態へ、可変発振器(202)を移行するために構成される制御信号を供給する。

(もっと読む)

発振器

【課題】複数の異なる発振周波数を選択して出力する発振器において、C/N比を高くしかつ回路を小型化する。

【解決手段】それぞれ異なる発振周波数の発振信号をコレクタに出力する複数の第1トランジスタと、それぞれのエミッタの出力が結合し入力される共通ノードと、共通ノードの出力をそれぞれのベースに帰還する帰還回路と、複数の第1トランジスタのそれぞれのエミッタと共通ノードとの間に設けられ、共通ノードからの高周波成分を遮断する複数のアイソレーション回路とを有する。第1トランジスタのエミッタの出力をベースにフィードバックする帰還回路により、C/N比を高くすることができる。又、複数の第1トランジスタのエミッタがそれぞれのアイソレーション回路を介し共通ノードに結合されていることにより小型化が可能となる。さらに、アイソレーション回路により、エミッタへの信号の逆流を抑制することができる。

(もっと読む)

発振器

【課題】消費電力が小さく、C/N特性を向上させた電圧制御発振器を提供する。

【解決手段】発振器は、制御端子Taにチョーク用インダクタL1を介しカソードが結合した第1可変容量ダイオードD11と、第1可変容量ダイオードのアノードとグランドとの間に接続された第1キャパシタC31および線路S4(第1インダクタ)を有する第1共振回路10と、制御端子にチョーク用インダクタL1を介しカソードが結合した第2可変容量ダイオードD12と、第2可変容量ダイオードのアノードとグランドとの間に接続された第2キャパシタC42および第2インダクタL42と、を有する第2共振回路20と、第1共振回路および第2共振回路に結合され、発振信号を出力する発振回路30と、を具備し、第1共振回路により共振周波数をほぼ決定し、第2共振回路で、C/N特性が向上するように調整する。

(もっと読む)

2バンド発振器

【課題】簡単な構成で二つの発振周波数帯に切り替えることのできる2バンド発振器を提供すること。

【解決手段】第一の発振トランジスタを有して第一の周波数帯で発振する第一の発振回路1と、第二の発振トランジスタを有して前記第一の周波数帯と異なる第二の周波数帯で発振する第二の発振回路2と、エミッタが電源端子に接続され、コレクタから前記第一の発振トランジスタにバイアス電圧を印加する第一のスイッチトランジスタ6と、エミッタが前記電源端子に接続され、コレクタから前記第二の発振トランジスタにバイアス電圧を印加する第二のスイッチトランジスタ9とを設け、前記第一のスイッチトランジスタ9のベースに切替端子8が接続され、前記第二のスイッチトランジスタ9のベースが前記第一のスイッチトランジスタ6のコレクタと接続されており、前記第一のスイッチトランジスタ6と前記第二のスイッチトランジスタ9とをオンとオフとが互いに逆となるように切り替えられる。

(もっと読む)

1 - 20 / 35

[ Back to top ]