Fターム[5J081FF02]の内容

LC分布定数、CR発振器 (9,854) | 構成要素(発振用能動素子、周波数決定素子以外) (1,204) | 回路構成 (543) | フィルタ (84)

Fターム[5J081FF02]に分類される特許

61 - 80 / 84

PLL制御発振器

【課題】小型化を促進して生産性を良好にし、電気的性能を向したPLL制御発振器を提供する。

【解決手段】水晶振動子3Aと発振回路と温度補償回路とからなる温度補償水晶発振器と、前記温度補償水晶発振器を基準信号源としてPLL制御されたLC発振回路を備えたPLL制御発振器において、前記温度補償水晶発振器の水晶振動子を除く発振回路と、前記温度補償発振器の温度補償回路と、前記PLL制御されたLC発振回路とを1チップIC20に集積化して、前記ICチップと前記水晶振動子とを一体化してなり、前記水晶振動子はH状とした容器本体36の一方の凹部の内壁段部に水晶片の一端部が固着され、前記ICチップは前記一方の凹部底面に固着されてなり、前記容器本体の他方の凹部底面には前記LC発振回路のインダクタ28a28bを形成するとともに、前記インダクタは前記LC発振回路の発振周波数を調整するプリントによるインダクタである。

(もっと読む)

電圧制御発振器

【課題】 高速起動性、低位相雑音性および低消費電力特性のすべてを充足できる電圧制御発振器を提供する。

【解決手段】 バイアス部は、電流源と、電流源に直列形態に接続される第1トランジスタと、第1トランジスタにカレントミラー接続され、制御電圧に応じて所望の周波数の発振信号を生成する本体部にバイアス電流を供給する第2トランジスタと、第1および第2トランジスタの制御端子間に接続され、抵抗素子として機能するスイッチ回路と、第2トランジスタの制御端子に接続される容量素子とを備えて構成される。電流源は、電圧制御発振器の起動状態時に第1トランジスタに対する電流供給動作を実施し、電圧制御発振器の定常状態時に第1トランジスタに対する電流供給動作を停止する。スイッチ回路は、電圧制御発振器の起動状態時にオンし、電圧制御発振器の定常状態時にオフする。

(もっと読む)

ユーザ指定可能、低コスト、低位相跳躍、かつスペクトル純度の高いチューナブル発振器

【課題】動作の同調レンジにわたって位相跳躍を吸収する機能を含み、マルチモードで、低コストかつ確実に動作するVCOを実現する。

【解決手段】第1のトランジスタと、第1のトランジスタと並列に接続された第2のトランジスタと、第1および第2のトランジスタに結合したノイズフィードバック・バイアス回路網と、第1および第2のトランジスタに結合した平面結合共振器回路網と、平面結合共振器回路網の共振周波数と第1および第2のトランジスタの接合静電容量を動的に調整するための手段とを備える。動的調整手段は第1及び第2のトランジスタの各接合部を跨ぐように結合した複数の容量性素子を備える。容量性素子は第1のコンデンサと直列に結合した可変容量ダイオード、及び可変容量ダイオードと直列に結合した第2のコンデンサを備える。

(もっと読む)

高周波発振装置

【課題】発振周波数の微調整が可能な高周波発振装置を提供する。

【解決手段】外部から印加される電圧によって容量値が調整可能な可変容量素子となるトランジスタTr2を含む共振回路を備え、共振回路から出力された高周波信号を受けて正帰還により発振信号を出力する高周波発振装置によって上記課題を解決することができる。

(もっと読む)

間欠動作回路及び変調装置

【課題】小回路規模、低消費電力で、立ち上がりと立ち下がりの速い出力波形を得ることができる間欠動作回路を提供すること。

【解決手段】能動回路106と、能動回路106の動作開始と動作停止を制御する第1の制御信号S1を生成する第1の制御信号生成回路101と、能動回路106にリンギング振動を起こさせ、かつ、そのリンギング振動の周波数と振幅値を制御することができる第2の制御信号S2を生成する第2の制御信号生成回路102と、能動回路106からリンギング振動と安定振動が継続して出力されるように、第1及び第2の制御信号S1、S2の能動回路106への入力タイミングを調整するタイミング調整回路103とを設けるようにする。

(もっと読む)

自動振幅制御機能を有する電圧制御発振機

【課題】電流源の代わりにアクティブ負荷を採用して利得の調整により電流源による位相雑音を除去し位相雑音特性を有する自動振幅制御機能を有する電圧制御発振機を提供する。

【解決手段】自動振幅制御機能を有する電圧制御発振機は共振信号を生成する共振回路と、共振信号をフィードバックして相互180°の位相差を有する2つの発振信号を生成する差動増幅回路と、差動増幅回路から生成される発振信号の利得を制御するアクティブ負荷を含む電圧制御発振部、及び2つの発振信号を変換して直流電圧を生成した後直流電圧と事前に設定された基準電圧を比較して上記アクティブ負荷の抵抗値を決定する制御電圧を出力する自動振幅制御部を含む。出力される発振信号の振幅を効果的に制御することが可能で、差動増幅回路のスイッチング時電流源により流入されるノイズ成分による位相雑音を減少させることが可能である。

(もっと読む)

ウィーンブリッジ発振回路

【課題】 制御を容易にでき、信号の安定性を向上させることができるウィーンブリッジ発振回路を提供すること。

【解決手段】 負帰還回路のゲインは一定にし、正帰還回路にゲイン可変素子であるVCA119を備え、VCA119の制御電圧の出力振幅を整流した信号について高圧トランス17の二次巻線171より高電圧を発生させて両波整流し、ローパスフィルタ(コンデンサ134,136、インダクタンス135)を通してリプルを減少させ、抵抗131,132による分圧により作成した信号レベルが大きい場合はゲインを小さくし、信号レベルが小さい場合は、ゲインを大きくすることにより出力振幅が一定になるように制御した。

(もっと読む)

発振器

【課題】 発振動作を行う能動素子で生じたノイズを外部に逃がすことにより、ノイズや寄生発振を低減することができる発振器を提供する。

【解決手段】 所定の周波数で発振動作を行うことにより発振周波数fの発振信号Soutを出力するトランジスタQ1と、発振周波数fにおけるインピーダンスよりも、発振周波数fより低い周波数においてインピーダンスが低下するインピーダンス素子Z1,Z2,Z3と、コンデンサC6,C7,C8とを備え、トランジスタQ1のコレクタ端子、ベース端子、及びエミッタ端子は、インピーダンス素子Z1とコンデンサC6との直列回路、インピーダンス素子Z2とコンデンサC7との直列回路、及びインピーダンス素子Z3とコンデンサC8との直列回路をそれぞれ介してグラウンドに接続されるようにした。

(もっと読む)

誘電体共振器装置、発振器および送受信装置

製造コストを低減できると共に、特性が安定した誘電体共振器装置、発振器および送受信装置を提供する。 回路基板1の表面1Aには伝送線路2を形成すると共に、裏面1Bにはグランド電極3を形成する。また、誘電体基板5の両面5A,5Bに円形の開口部7をもった電極6を形成することによって、TE010モード共振器4を構成する。そして、回路基板1のグランド電極3とTE010モード共振器4の電極6との間には絶縁層8を設けると共に、絶縁性接着剤9を用いてTE010モード共振器4を回路基板1に取付ける。これにより、回路基板1とTE010モード共振器4との間に部分的な剥離が生じたときでも、電流経路の変化がなく、特性を安定化することができる。  (もっと読む)

(もっと読む)

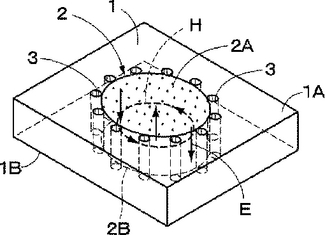

TMO10モード共振器装置、発振器装置および送受信装置

電磁界の放射を抑圧し、高いQをもったTMO10モード共振器装置、発振器装置および送受信装置を提供する。 誘電体基板1の表面1Aと裏面1Bにそれぞれ円形状の共振器電極2A,2Bを互いに対向して設け、TMO10モード共振器2を形成する。また、誘電体基板1には、円形状の共振器電極2A,2Bに沿って内壁面3Aの電極が省かれた複数のスルーホール3を設け、これらのスルーホール3によって開放端を形成する。これにより、誘電体基板1内に形成される電磁界をスルーホール3と空気との境界で全反射させることができ、電磁界の放射を抑圧することができる。  (もっと読む)

(もっと読む)

可変容量回路および可変容量回路の制御方法

【課題】 低電源電圧においても、可変容量素子の素子面積を増大させることや、制御電圧のレベル変換を行うことなく、可変容量素子の可変容量幅を最大限に広げることが可能な可変容量回路および可変容量の制御方法を提供すること。

【解決手段】 可変容量回路2は、容量値制御回路11、バラクタVA1およびVA2、抵抗素子R1およびR2を備える。容量値制御回路11は、入力される制御電圧VTに応じて、可変な出力電圧CNTOUTを出力することで、バラクタの両端の電位を同時に制御する。出力電圧CNTOUTは、制御電圧VTに対して、負の相関を有するように可変に調整される。端子間電圧VDの変動幅を、変動幅SA1から変動幅SA1a(レンジは±(Vcc1))へ拡大することができる。すると図5(B)に示すように、バラクタ容量値CVの可変領域を、可変領域CA1から可変領域CA1aへ広げることができる。

(もっと読む)

発振回路

【課題】 発振信号を取り出す段階で高調波、特にレベルの大きい2倍高調波を効果的に抑制できる発振回路を提供する。

【解決手段】 コレクタ又はベースが高周波的に接地された発振トランジスタ21と、発振トランジスタ21のエミッタを直流的にグランドに接続するバイアス抵抗27とを備え、発振周波数でインピーダンスが最大となる共振手段28を前イアス抵抗27とグランドとの間に介挿し、バイアス抵抗27と共振手段28との接続点から発振信号を取り出した。

(もっと読む)

電圧制御発振器

【課題】 消費電力が少なく、回路面積が小さい電圧制御発振器において、位相雑音特性を向上させる。

【解決手段】 本発明による電圧制御発振器は、相互に並列接続されたインダクタンスL11と可変容量C11及び12とを備えたLC共振回路1と、LC共振回路1に接続され、LC共振回路1による発振を持続させるための負性コンダクタンスを有する発振トランジスタ対2及び3と、電流源4とを備え、電流源4と発振トランジスタ対2とは抵抗8を介して接続され、LC共振回路1の発振動作に伴う偶数次高調波が電流源4に入力されるのが抑制される。

(もっと読む)

発振制御装置

【課題】 VCOのf/v感度のばらつきを補正することで、VCOの安定動作とC/N劣化などの特性の劣化防止を図ることができる発振制御装置を提供する。

【解決手段】 可変共振器2を備えるVCO1と分周器6と位相比較器7とLPF8とによって構成されるPLLにおいて、可変共振器制御信号生成部10が、LPF8の出力電圧を入力してVCO1のf/v感度を検出して可変共振器制御信号を生成し、可変共振器制御信号によって可変共振器2の容量を制御する。具体的には、電圧検知回路5がLPF8の出力電圧を入力して所定の電圧を検知すると、データラッチ回路4が電圧検知回路5の検知した電圧に基づいた可変共振器制御信号を可変共振器2へ送信して可変容量の制御を行う。その結果、PLLの構成素子のばらつきや温度変化があってもVCO1のf/v感度を最適値に制御することができる。

(もっと読む)

電圧制御発振回路

【課題】出力インピーダンスの調整が容易に行なうことができ、高調波成分の抑制も容易に実現することが可能とした電圧制御発振回路を提供する。

【解決手段】共振周波数帯域を異なる2つの帯域に切り換えるためのシフト回路を含む共振回路部Xと負性抵抗回路部Yと増幅回路部Zとから構成される電圧制御発振回路において、前記増幅回路部Zの増幅用トランジスタのコレクタ端子と接地電位との間に、ストリップ線路L2と第1のコンデンサC9とが並列に接続された並列回路部Hを配置するとともに、前記増幅用トランジスタのコレクタ端子C9と前記出力端子OUTPUTとの間に、第2のコンデンサC10とインダクタ素子L3とが直列に接続された直列回路部Tを配置した。

(もっと読む)

電圧制御発振器及び発振周波数調整方法

【課題】周波数曲線の切り換え機能と、素子バラツキによる周波数曲線の変動を補償する機能を両立させる点にある。

【解決手段】負性抵抗素子19bとインダクタ素子19あと外部から与えられる第一電圧17により容量が変化する第一のキャパシタ18と制御電圧により容量が変化する複数のキャパシタからから成る第二のキャパシタ11を備える共振回路と、周波数情報13と自動校正値14に基づいて出力が確定する論理合成手段12とを備え、前記第二のキャパシタの容量値を前記論理合成手段の出力に基づく制御電圧により可変とした。

(もっと読む)

周波数シンセサイザとその制御

【課題】電源ノイズや温度特性により周波数シンセサイザの位相雑音の劣化や、電圧制御発振器の周波数温度変動が大きくなるという課題があった。

【解決手段】構成要素の電圧制御発振器1の共振部がインダクタ122a、122bと周波数制御用のMOSバリキャップ123a、123bと、周波数帯域切り替え用のMOSバリキャップ127a、127b、128a、128bから構成され、ゲート端子に固定電圧を入力することで周波数帯域を切り替えることにより行い、電圧制御発振器が非動作状態でゲート電位をバックゲート電位よりも高くする制御を行う。

(もっと読む)

二重周波数発振器及び合成器を有する変調器

基本周波数で発振し高調波も発生する発振器(10)。基本周波数又は低い高調波がフィードバックの目的で用いられ、基本周波数又は当該低い高調波よりも高い高調波が出力のために用いられる。結果的に、発振器(10)は、出力周波数よりも低い周波数で動作し低コストとなる。発振器(10)に結合された合成器(20)も、この低周波数で動作し、このような発振器(10)及び合成器(20)を有する変調器(5)は、低コストとなる。低い電力消費及び妨害電界に対しての低い感応性がさらなる利点である。フィルタ処理は、複雑さが軽減され、少数の構成要素が小さな構成を導く。発振器(10)は、同調回路(11)と増幅器(12)を有し、増幅器(12)は、フィードバック回路(13)によって帰還される。このような増幅器(12)は、ただの単一のトランジスタ(40)を有するものとすることができる。  (もっと読む)

(もっと読む)

電圧制御発振器、及び無線通信機器

【課題】 電界効果トランジスタを用いる電圧制御発振器において、電源電圧変動に伴う発振周波数の揺れを小さくするためにバックゲート端子をソースに接続すると、基板ロスが大きくなり位相雑音特性が劣化する。

【解決手段】 発振トランジスタ115のバックゲート端子を、高インピーダンス素子119を介してソース端子に接続し、発振トランジスタ116のバックゲート端子を、高インピーダンス素子120を介してソース端子に接続する。

(もっと読む)

電圧制御発振器

【課題】各発振周波数において出力信号の品質を劣化させずにすむような2周波数選択電圧制御発振器を提供することにある。

【解決手段】発振周波数を決定する帯域通過フィルタと、これの前段および後段に設けられた整合回路と、フィードバックループの損失を補完するための増幅回路と、発振条件および発振周波数を決定する固定移相器と、発振周波数を外部からの電圧信号によってコントロールするための電圧制御可変移相器と、外部出力とループ内出力への分配を決める分配器とをシリーズに配置して構成される電圧制御発振器を2回路有し、更に各該電圧制御発振器の電源切り替え回路と各該電圧制御発振器の出力信号を束ねる結合回路を有する2周波数電圧制御発振器において、前記結合回路として、キャパシタ、インダクタ、抵抗から成る2入力低域通過フィルタの回路構成を持たせる。

(もっと読む)

61 - 80 / 84

[ Back to top ]