Fターム[5J081FF02]の内容

LC分布定数、CR発振器 (9,854) | 構成要素(発振用能動素子、周波数決定素子以外) (1,204) | 回路構成 (543) | フィルタ (84)

Fターム[5J081FF02]に分類される特許

21 - 40 / 84

デジタルPLL回路及び半導体集積回路

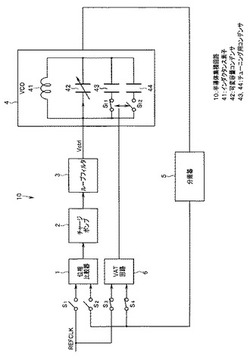

【課題】粗調整用と微調整用のコンデンサを切り替えて発振回路の発振周波数を調整する際に、粗調整区間に生じるサイクルスリップに起因して発振周波数可変範囲が狭くなるのを回避可能なデジタルPLL回路及び半導体集積回路を提供することである。

【解決手段】インダクタンス素子に並列接続される容量素子の数を変えて発振周波数が制御される発振回路4と、基準クロック及びその遅延クロックと発振回路出力とをデジタル位相比較し、その比較結果に基づいて容量素子の並列接続数を制御し、発振回路出力の位相を基準クロック位相に近づける制御をする位相比較部6とを具備し、容量素子は、インダクタンス素子に並列接続可能な所定容量の粗調整用コンデンサ43と、これに並列接続可能で粗調整用コンデンサの1/n容量を有し、粗調整時に所定数の微調整用コンデンサが1つの粗調整用として制御される複数の微調整用コンデンサ44を備える。

(もっと読む)

発振器及びそれを用いた周波数生成回路並びに無線通信システム

【課題】LC型発振器において、高調波歪みによる位相雑音の劣化が小さく、かつ発振振幅の増大化を図り、これにより良好な低位相雑音特性を有する発振器及びそれを用いた通信システムを提供する。

【解決手段】トランジスタからなる少なくとも1つ以上の電圧-電流変換部と、1対の容量性素子と誘導性素子からなるLCタンクを2つ有している共振器とを具備して成り、前記の電圧-電流変換部の出力端子は、前記の共振器に接続され電流-電圧変換されたのちに、前記電圧-電流変換部の入力端子に接続されることにより、帰還ループが構成されて成り、前記共振器を構成している2つのLCタンクを構成する誘導性素子が相互誘導結合されており、前記相互結合係数がおおよそ-0.6であることを特徴とする。

(もっと読む)

半導体発振回路および携帯電話

【課題】基準周波数生成回路は、ロジック回路の電源ノイズの影響を受けて、周波数偏差やピリオドジッターの悪化を引き起こしていた。

【解決手段】CPUや周辺回路などのロジック回路12の電源はレギュレータ13より供給し、基準周波数生成回路11の電源には電源の高周波ノイズを10dB以上の減衰量を持つローパスフィルター10を介してから供給する。これによりロジック回路12で発生する高周波ノイズ起因での周波数偏差やジッターの悪化を抑えることができ、この基準周波数をUARTシリアル回路に接続して通信ができる。

(もっと読む)

差動出力発振器

【課題】位相雑音を良好にする。

【解決手段】共振回路11として、第1のトランジスタ2aのコレクタにそれぞれ一端が接続された共振周波数f1の第1の直列共振器5aおよび共振周波数f2(f2≠f1)の第2の直列共振器8aと、第2のトランジスタ2bのコレクタにそれぞれ一端が接続された共振周波数f1の第3の直列共振器5bおよび共振周波数f2の第4の直列共振器8bを用い、第1の直列共振器5aの他端と第3の直列共振器5bの他端を互いに接続するか接地し、また第2の直列共振器8aの他端と第4の直列共振器8bの他端を互いに接続するか接地したものである。

(もっと読む)

良好な雑音耐性を有する広帯域電圧制御発振器

【課題】広いレンジに対してその動作周波数を同調させる能力を有し、雑音特性に優れた電圧制御発振器を実現する。

【解決手段】第1及び第2のコイル422、424と第1及び第2の結合コンデンサ402、404は共振回路入力端子から見た時に2極ハイパスフィルタを構成し、共振回路の入力端子上に誘導される低周波数雑音はこの2極ハイパスフィルタにより減衰される。第1の同調ダイオード432は第1の可変容量ダイオード442と同じ可変容量ダイオードを使用し、第1の同調コンデンサ432と第1の可変容量ダイオード442のカソードを接続する。AC雑音は第1の可変容量ダイオード442に渡って現れるのと逆の極性で第1の同調コンデンサ432に渡って現れるので、AC雑音が第1の同調コンデンサ432上の逆バイアス電圧を増加させると、第1の可変容量ダイオード442上の逆バイアス電圧はそれに対応して減少する。

(もっと読む)

PLL回路

【課題】PLL回路において、アナログ回路のデジタル化によって生じる量子化雑音を抑制することができる技術を提供する。

【解決手段】基準信号REFと分周後の信号DIVとの位相及び周波数を比較してデジタル値に変換するデジタル位相周波数比較器(DPFD)101と、デジタル位相周波数比較器101の出力から高周波雑音成分を除去するデジタルループフィルタ(DLF)102と、デジタルループフィルタ102の出力のデジタル値をアナログ値に変換するデジタルアナログ変換器(DAC)105と、デジタルアナログ変換器105の出力から高周波雑音成分を除去するアナログフィルタ(AnF)106と、アナログフィルタ106の出力に基づいて周波数が制御される電圧制御発振器(VCO)103と、電圧制御発振器103の出力を分周し、分周後の信号DIVを出力する分周器(DIV)104とを備える。

(もっと読む)

電圧制御発振回路

【課題】発振周波数を制御するPLL回路で生成可能な制御電圧の最大値を低電圧化しても、可変容量ダイオードに印加される電圧の可変範囲を広げることができ、しかも簡単な回路構成で実現でき、発振器の小型化を図ること。

【解決手段】この電圧制御発振回路1は、発振用トランジスタ2と、可変容量ダイオード16を有し発振用トランジスタ2に接続された共振回路13と、電源電圧が印加される電源端子T2とグラウンドとの間に介挿されると共に可変容量ダイオード16に対して並列に接続されたコレクタ抵抗RCと、コレクタ抵抗RCのグラウンド側の端部とグラウンドとの間に介挿され発振周波数を制御する制御電圧が印加される制御用トランジスタ21とを具備する。

(もっと読む)

フィルタ回路及び電圧制御発振回路

【課題】双方の信号線路の遅延を容易に一致させることができると共に、不要信号を相殺することができる。

【解決手段】この電圧制御発振回路は、発振回路部1と、発振信号を分岐すると共に互いに位相の反転した第1及び第2の信号を別々に出力する出力分波回路2と、出力分波回路2の出力段に並列に接続され同一構成を有し、トラップ周波数が異なるトラップ回路3、4と、トラップ回路の出力を合成する出力再合成回路とを備える。発振回路部1の電圧制御信号をトラップ回路3、4のバラクタダイオード32,34に印加してトラップ回路3、4のトラップ周波数を発振周波数に連動させる。

(もっと読む)

高周波発振器

【課題】周囲の環境温度による光ファイバの熱伸縮に対してもPLL制御を正常に行うことができる高周波発振器を得る。

【解決手段】レーザ光源が発生したレーザ光を光変調器により変調し、光ファイバを介して伝送した変調後のレーザ光を光電変換器により高周波信号に変換し、変換後の高周波信号からバンドパスフィルタにより所定の通過帯域成分を取り出し、当該所定の通過帯域成分の高周波信号の周波数を変調信号として前記光変調器に帰還すると共に発振信号として出力する高周波発振器において、高周波信号の周波数が一定になるように制御するPLL制御手段と、当該高周波発振器の発振周波数の変動をPLL制御手段の予め設定した周波数引き込み範囲内に納めるように高周波信号の位相を調整する位相調整手段を備えた。

(もっと読む)

プッシュ・プッシュ形式電圧制御発振回路、並びにそれを用いた無線通信機器およびRFモジュール

【課題】周波数可変範囲を狭くすることなく大きな逓倍出力を得られるプッシュ・プッシュ発振回路を提供すること、またその上で2系統の源発振周波数信号を供給可能なプッシュ・プッシュ発振回路を提供すること、或いはそれを用いた無線通信機器を提供する。

【解決手段】差動トランジスタ対と差動トランジスタ対の間に接続されたLC共振回路10と周波数選択回路30を備えたプッシュ・プッシュ電圧制御発振回路であって、前記周波数選択回路30は伝送線路300を備え、源発振周波数に対する2倍高調波信号を前記伝送線路300のグランドライン32から出力する。2倍高調波信号を伝送線路300のグランドライン32から出力することで、伝送線路300の線路を信号が伝播するときに発生する伝播損失を低減でき、大きな出力電力が得られる。

(もっと読む)

集積回路

【課題】CR発振回路を構成するコンデンサの充放電切換りタイミングと、論理回路を構成するCMOSインバータに貫通電流が流れるタイミングとをずらすことで、周波数が安定した発振信号を発生する集積回路を提供する。

【解決手段】複数のCMOS素子によって構成された論理回路と、論理回路に、容量素子と抵抗素子の時定数に依存する周波数の発振信号を出力するCR発振回路と、論理回路に入力される発振信号を遅延する遅延回路と、を備え、CR発振回路と電源とを接続する電源配線が、論理回路と電源とを接続する電源配線と接続されている。

(もっと読む)

誘電体発振器、低雑音ダウンコンバータおよびアンテナ装置

【課題】発振周波数の調整および制御を容易に行ない、かつ生産コストの増大を防ぐことが可能な誘電体発振器、低雑音ダウンコンバータおよびアンテナ装置を提供する。

【解決手段】誘電体発振器101は、第1のマイクロストリップライン61に接続された制御電極と、第2のマイクロストリップライン62に接続された導通電極とを有するトランジスタTRと、第1および第2のマイクロストリップライン61,62を磁気的に結合する誘電体共振器DRと、第1のマイクロストリップライン61に結合され、発振周波数を制御するための制御電圧が供給される第1の可変容量素子D1と、少なくとも第1のマイクロストリップライン61によって形成され、第1の可変容量素子D1と第1のマイクロストリップライン61との間の直流電圧の伝達を遮断する直流遮断部とを備える。

(もっと読む)

正確で安定したLC型基準発振器のための方法、システム、および装置

【課題】周波数の安定性およびジッタの要件を満たしつつ、CMOS技術における既存の最適化プロセスの手順に依拠した集積化の解決手法を利用した、温度に対して非依存型のLC型発振器を提供する。

【解決手段】実質的に温度に非依存のLC型発振器は、温度ヌル位相に実質的に等しい位相でタンク発振を生成するLC発振器タンク10を用いて達成される。該温度ヌル位相は、LC型発振器の出力発振の周波数の温度変化に伴う変動が最小化されるときの、LC発振器タンク10の位相である。該LC型発振器はさらに、該LC発振器タンク10に接続されて、該温度ヌル位相に実質的に等しい位相で該LC発振器タンク10を発振させる周波数安定化回路を含む。

(もっと読む)

PLL周波数シンセサイザ回路及びその制御方法

【課題】信号に対するノイズの増加がなく安定したPLL周波数シンセサイザ回路及びその制御方法を提供する。

【解決手段】電圧制御発振器の制御電圧をモニタし、制御電圧に応じて前記電圧制御発振器の変調感度との間で安定に動作するように設定されたループフィルタを切り替えるようにした。

(もっと読む)

発振回路

【課題】特にLC発振回路において、インダクタをトランス構造とし、1次側の発振による交流信号を2次側より効率的に取り出し、整流した後に、発振回路の電源に帰還させ、省電力化及び電源を供給しない発振継続を可能とする発振回路を提供する。

【解決手段】所定の飽和時の共振条件を満たし、逆流防止回路を通して直流電源に接続され、第一のインダクタL1とトランス構造を構成する第二のインダクタL2と、第一のインダクタL1と直列に接続された第一のコンデンサC1と、第二のインダクタL2と直列に接続された第二のコンデンサC2と、を備え、第二のインダクタL2から出力された交流電流を整流し発振回路の電源に帰還させ省電力化及び発振継続を可能とする発振増幅器を提供する。これにより、LC発振回路において、電源を切断した後の発振回路の発振継続、あるいは発振回路の低消費電力化、あるいは外部への電力供給が可能となる。

(もっと読む)

PLL回路

【課題】回路や制御を複雑にすることなく、電圧制御発振回路の発振周波数レンジを広く保持しつつ出力クロックのジッターを低減可能なPLL回路を提供すること。

【解決手段】前段のLPF3から入力される制御電圧信号VCTRLの電位に応じた周波数を有する出力クロックを、制御端子に入力される制御電圧に応じて遅延時間が変化する遅延回路のM個を環状に接続したリングオシレータを用いて発生するVCO回路4aを備えるPLL回路において、VCO回路4aは、制御電圧信号VCTRLから低周波帯域の制御電圧信号VCTRLを抽出する低域通過フィルタを備え、前記リングオシレータは、前記M個の遅延回路のうち、m個(m<M)の各遅延回路の制御端子に制御電圧信号VCTRLが入力され、(M−m)個の各遅延回路の制御端子に制御電圧信号VCTRL2が入力される。

(もっと読む)

発振回路、及びこれを用いた無線受信回路、スイッチ装置

【課題】消費電力の増大と発振周波数調整に要する時間の増大とを低減しつつ、従来よりも発振周波数の調整精度を向上させることが容易な発振回路、及びこれを用いた無線受信回路、スイッチ装置を提供する。

【解決手段】パルス信号PWM1を出力すると共にパルス幅の設定を受け付けるパルス生成部PWMG1と、パルス信号PWM1を平滑して得られた直流電圧Vdc1を出力するローパスフィルタLPF1と、Vdc1を接続点P1に印加する配線25と、パルス信号PWM2を出力すると共にパルス幅の設定を受け付けるパルス生成部PWMG2と、PWM2を平滑して得られた電圧VLP2を出力するローパスフィルタLPF2と、VLP2を所定の比率に変換して直流電圧Vdc2として接続点P2に印加する電圧変換部CNV2と、接続点P1,P2間の電圧に応じた周波数の発振信号を生成する並列共振回路23を備えた。

(もっと読む)

電圧制御発振器、並びにそれを用いたPLL回路及び無線通信機器

【課題】C結型の可変容量回路と直結型の可変容量回路とを上手く混在させて構成し、発振周波数の線形性及び可変範囲のバランスがとれた電圧制御発振器を提供する。

【解決手段】本発明の電圧制御発振器は、並列接続されたインダクタ回路110、C結型可変容量回路120及び140、直結型可変容量回路130、及び負性抵抗回路160と、基準電位Vref1及びVref2を生成する基準電位発生部180とを備える。各可変容量回路120、130、及び140の可変容量素子121、122、131、132、141、及び142のバックゲート端子には、発振周波数をフィードバック制御するための制御電位Vtが印加される。C結型可変容量回路120及び140の可変容量素子121、122、141及び142のゲート端子には、基準電位Vref1及びVref2がそれぞれ印加される。

(もっと読む)

電圧制御発振装置

【課題】高いC/N及び周波数安定度を確保できると共に、周波数可変幅を広くしても帯域外の不要信号の漏れ出しを抑制でき、かつ同時にインピーダンスマッチングもとることができるようにすること。

【解決手段】この電圧制御発振装置は、制御電圧信号に応じて発振周波数が制御される電圧制御発振回路1と、電圧制御発振回路に供給する制御電圧信号を生成するPLL回路2と、電圧制御発振回路1の出力する発振信号を逓倍する逓倍回路3と、逓倍回路3の出力する逓倍信号のうち所定逓倍数の信号を通過させる通過帯域と逓倍回路3に入力した発振信号と同一周波数をトラップするトラップ周波数とが設定された帯域通過フィルタ兼トラップ回路4とを備える。制御電圧信号を分岐して段間結合兼トラップ回路15へ入力し、発振周波数に同期させて段間結合兼トラップ回路15の通過帯域及びトラップ周波数を可変させると共に段間結合量を調整する。

(もっと読む)

温度補償のための補助バラクタ

電圧制御発振器(VCO)周波数に対する温度変化の影響を補償するための技法が、開示される。一実施形態においては、補助バラクタが、VCOのLCタンクに結合される。補助バラクタは、温度に伴ってVCO周波数の全体の変化を最小にする、温度依存制御電圧(Vaux)によって制御されるキャパシタンスを有する。デジタル手段とアナログ手段とを使用して制御電圧を生成するための技法が、さらに開示される。補助バラクタ(Caux)は、LCタンクの電圧制御キャパシタ(C)と直列に、または並列にのいずれかで結合されることができる。一実施形態においては、制御電圧は、絶対温度に比例した第1の電流と、温度にわたって一定の第2の電流、例えば、バンドギャップ電流、との間の差を得ることによって生成される。  (もっと読む)

(もっと読む)

21 - 40 / 84

[ Back to top ]