Fターム[5J081FF19]の内容

LC分布定数、CR発振器 (9,854) | 構成要素(発振用能動素子、周波数決定素子以外) (1,204) | 回路素子 (660) | 半導体 (256) | ダイオード (29)

Fターム[5J081FF19]に分類される特許

1 - 20 / 29

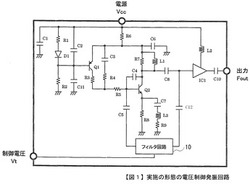

低雑音電圧制御発振回路

【課題】 電源雑音を除去し、低周波雑音の特性を良好にできる低雑音電圧制御発振回路を提供する。

【解決手段】 駆動用トランジスタQ1 のベースとGNDの間にコンデンサC11を設けることで、そのベースに入力される低周波ノイズを除去でき、駆動用トランジスタQ1 をhFEの低いトランジスタとすることで、電源から入力される低周波ノイズを除去することができ、発振用トランジスタQ2 のエミッタ側に、コイルL3 を設けることで、周波数特性を広域化して位相雑音の周波数特性を良好にでき、発振用トランジスタQ2 のエミッタ側に、コンデンサC7 とコイルL3 で構成される共振回路における共振周波数をVCOの発振周波数帯域の中心辺りに設定することで、ノイズの影響を受けにくい発振周波数にすることができる低雑音電圧制御発振回路である。

(もっと読む)

発振回路

【課題】半導体集積回路の電源電圧や温度の変動がある場合においても、発振波形の周波数変動を低減させる。

【解決手段】リミッタLm1は、出力端子T1の発振信号Vo1の電圧と、基準電圧Vconstに電圧降下Vth分を加算した値とを比較し、出力端子T1の発振信号Vo1の電圧が、基準電圧Vconstに電圧降下Vth分を加算した値を超えた場合、出力端子T1の発振信号Vo1の振幅を、基準電圧Vconstに電圧降下Vth分を加算した値に制限する。

(もっと読む)

発振器

【課題】高い発振周波数で動作する場合であっても、十分なストリップライン長を確保することができ、製造誤差によるバラつきを防止すると共に、Qの低下を防止すること。

【解決手段】発振器10は、発振トランジスタ2と、前記発振トランジスタ2のベース−エミッタ間に設けられる第1の帰還コンデンサ4と、前記発振トランジスタ2のコレクタ−エミッタ間に設けられる第2の帰還コンデンサ5と、前記発振トランジスタ2のベースに一端が接続される共振用ストリップライン13と、前記発振トランジスタ2のエミッタ−グラウンド間に設けられるトラップ回路20と、を備え、前記共振用ストリップライン13は、発振周波数において高次共振モードとなる長さを有し、前記トラップ回路20は、前記高次共振モードより低次側の低次共振モードに相当する周波数の信号を減衰させるものである。

(もっと読む)

PLL回路

【課題】PLL回路において、アナログ回路のデジタル化によって生じる量子化雑音を抑制することができる技術を提供する。

【解決手段】基準信号REFと分周後の信号DIVとの位相及び周波数を比較してデジタル値に変換するデジタル位相周波数比較器(DPFD)101と、デジタル位相周波数比較器101の出力から高周波雑音成分を除去するデジタルループフィルタ(DLF)102と、デジタルループフィルタ102の出力のデジタル値をアナログ値に変換するデジタルアナログ変換器(DAC)105と、デジタルアナログ変換器105の出力から高周波雑音成分を除去するアナログフィルタ(AnF)106と、アナログフィルタ106の出力に基づいて周波数が制御される電圧制御発振器(VCO)103と、電圧制御発振器103の出力を分周し、分周後の信号DIVを出力する分周器(DIV)104とを備える。

(もっと読む)

フィルタ回路及び電圧制御発振回路

【課題】双方の信号線路の遅延を容易に一致させることができると共に、不要信号を相殺することができる。

【解決手段】この電圧制御発振回路は、発振回路部1と、発振信号を分岐すると共に互いに位相の反転した第1及び第2の信号を別々に出力する出力分波回路2と、出力分波回路2の出力段に並列に接続され同一構成を有し、トラップ周波数が異なるトラップ回路3、4と、トラップ回路の出力を合成する出力再合成回路とを備える。発振回路部1の電圧制御信号をトラップ回路3、4のバラクタダイオード32,34に印加してトラップ回路3、4のトラップ周波数を発振周波数に連動させる。

(もっと読む)

誘電体発振器、低雑音ダウンコンバータおよびアンテナ装置

【課題】発振周波数の調整および制御を容易に行ない、かつ生産コストの増大を防ぐことが可能な誘電体発振器、低雑音ダウンコンバータおよびアンテナ装置を提供する。

【解決手段】誘電体発振器101は、第1のマイクロストリップライン61に接続された制御電極と、第2のマイクロストリップライン62に接続された導通電極とを有するトランジスタTRと、第1および第2のマイクロストリップライン61,62を磁気的に結合する誘電体共振器DRと、第1のマイクロストリップライン61に結合され、発振周波数を制御するための制御電圧が供給される第1の可変容量素子D1と、少なくとも第1のマイクロストリップライン61によって形成され、第1の可変容量素子D1と第1のマイクロストリップライン61との間の直流電圧の伝達を遮断する直流遮断部とを備える。

(もっと読む)

発振回路

【課題】特にLC発振回路において、インダクタをトランス構造とし、1次側の発振による交流信号を2次側より効率的に取り出し、整流した後に、発振回路の電源に帰還させ、省電力化及び電源を供給しない発振継続を可能とする発振回路を提供する。

【解決手段】所定の飽和時の共振条件を満たし、逆流防止回路を通して直流電源に接続され、第一のインダクタL1とトランス構造を構成する第二のインダクタL2と、第一のインダクタL1と直列に接続された第一のコンデンサC1と、第二のインダクタL2と直列に接続された第二のコンデンサC2と、を備え、第二のインダクタL2から出力された交流電流を整流し発振回路の電源に帰還させ省電力化及び発振継続を可能とする発振増幅器を提供する。これにより、LC発振回路において、電源を切断した後の発振回路の発振継続、あるいは発振回路の低消費電力化、あるいは外部への電力供給が可能となる。

(もっと読む)

電圧制御発振装置

【課題】高いC/N及び周波数安定度を確保できると共に、周波数可変幅を広くしても帯域外の不要信号の漏れ出しを抑制でき、かつ同時にインピーダンスマッチングもとることができるようにすること。

【解決手段】この電圧制御発振装置は、制御電圧信号に応じて発振周波数が制御される電圧制御発振回路1と、電圧制御発振回路に供給する制御電圧信号を生成するPLL回路2と、電圧制御発振回路1の出力する発振信号を逓倍する逓倍回路3と、逓倍回路3の出力する逓倍信号のうち所定逓倍数の信号を通過させる通過帯域と逓倍回路3に入力した発振信号と同一周波数をトラップするトラップ周波数とが設定された帯域通過フィルタ兼トラップ回路4とを備える。制御電圧信号を分岐して段間結合兼トラップ回路15へ入力し、発振周波数に同期させて段間結合兼トラップ回路15の通過帯域及びトラップ周波数を可変させると共に段間結合量を調整する。

(もっと読む)

高周波用電圧制御発振回路

【課題】 異常発振を抑制し、位相雑音を改善すると共に回路を小型化できる高周波用電圧制御発振回路を提供する。

【解決手段】 発振用増幅回路の帰還ループに移相回路として、容量性可変リアクタンス素子Dと誘導性リアクタンス素子Lの並列共振回路を複数有する複同調回路と、その入出力に直列に接続された容量性可変リアクタンス素子D1 ,D2 とで構成し、複同調回路は複同調回路が複数の並列共振回路を容量性可変リアクタンス素子D3 で接続し、容量性可変リアクタンス素子の調整によりバンドパスフィルタの特性を実現した高周波用電圧制御発振回路である。

(もっと読む)

電圧制御発振器および電圧制御発振器の発振周波数制御方法

【課題】電圧制御発振器で使用される可変容量において、回路のグラウンド電位から電源電位以上に広い可変容量の線形領域を使用することが可能な電圧制御発振器を提供する。

【解決手段】共振回路を構成するインダクタ2a、2bと可変容量10a、10b、11a、11b、12a、12bと、共振回路の共振周波数を制御するための周波数制御端子5とを備えた発振部200に加え、共振回路にバイアス電圧を与えるバイアス回路201と、周波数制御電圧に応じてバイアス回路201のバイアス電圧を切り替え制御するバイアス制御回路202を設ける。バイアス制御回路202は周波数制御電圧が変化してしきい値を超えたときに、周波数制御電圧を目的の制御電圧に近づける方向にバイアス電圧を切り替える。

(もっと読む)

水晶発振回路

【課題】CMOSインバータで構成される発振回路の閾値電圧VTの温度変動に起因する消費電流や、負性抵抗などのさまざまな特性変動を大幅に改善することができる水晶発振回路を提供する。

【解決手段】水晶振動子を備えたCMOSインバータ型発振回路4の電源電圧に温特付き電源回路31の出力部を接続し、前記温特付き電源回路31はアンプ2とダイオード20と抵抗11で構成され、前記アンプ2の出力端V2はダイオード20のアノードに接続され、前記ダイオード20のカソード側は前記アンプ2の負入力端V3と抵抗11の一端に接続され、前記抵抗11の他端は接地され、アンプ2の正入力端V1にはVCC変動の少ない電圧源1に接続される。

(もっと読む)

集積回路技術を用いたマイクロ波発振器

本発明は集積回路技術を用いるミリメートル周波数発振器に関する。この発振器は制御信号Vtに応じた発振周波数Foutを提供する、マイクロ波出力(Sf)を備える。発振周波数Foutは、発振器の2つの制御入力を介して中心周波数Fcの周りで変調されることができ、第1の制御入力Ec1は発振器の中心周波数Fcを固定する第1の制御信号Vt1により駆動され、第2の制御入力Ec2は、この中心周波数Fcの直線変調を可能にする第2の制御信号Vt2により駆動される。発振器の制御信号Vtは2つの制御信号Vt1及びVt2の関数である。用途:電気通信、レーダー、自動車用レーダー。 (もっと読む)

雑音除去を有するループフィルタ

【解決手段】 ループフィルタは、第1及び第2の信号経路720,730、演算増幅器(オペアンプ)736及び雑音除去経路740を含む。第1の信号経路720は、第1の信号に第1の伝達関数を供給する。第2の信号経路730は、第2の信号に第2の伝達関数を供給する。第2の信号は、第1の信号のスケール化バージョンである。キャパシタ734は、因子アルファだけ小さくスケールされる。オペアンプは、第1及び第2の信号経路に結合され、オペアンプ雑音を有する制御信号VCTRLを生成するために第1及び第2の信号経路からの信号を合計することを容易にするように形成される。雑音除去経路740は、オペアンプに結合され、制御信号中のオペアンプ雑音を相殺するのに使用される雑音除去信号VCTRLを生成する。制御信号VCTRL及び雑音消去信号VNは、電圧制御発振器(VCO)内に含まれるバリキャップ750の各ノードに適用される。 (もっと読む)

バースト発振器

【課題】従来のバースト発振器の構成では、発振周波数を開閉するスイッチにおけるリークにより、オフ状態の休止期間であっても高周波の発振信号が出力にリークして出てしまうという課題があった。

【解決手段】本発明のバースト発振器は、発振信号を断続的に出力端から出力するバースト発振器であって、発振信号を発生する発振器と、発振器の電源供給ラインと出力端との間に接続され発振信号の出力端からの出力を断続させるスイッチと、出力端から高周波アースラインに順方向に接続されたダイオードと、発振器の出力と出力端の間に接続され発振信号の波長λの1/4ライン長をもつ伝送ラインとを備える。

(もっと読む)

発振装置

【課題】小型化及び低コスト化を実現すると共に発振周波数可変比が小さい側の信号帯域選択時に同調電圧範囲を十分に利用でき、しかも局部発振周波数とのトラッキングをとることができるようにすること。

【解決手段】この発振装置は、一端に同調電圧Vtが印加されるバラクタダイオード21、容量結合コンデンサ11、VHF発振回路10と、1/2分周器30とを備える。1/2分周器30はVHFハイバンド選択時はスルー動作とし、VHFローバンド選択時は1/2分周動作とする。また、VHFハイバンド選択時はバラクタダイオード21の電圧−容量変化カーブのうち容量変化範囲の大きい領域を使用して共振信号を生成し、VHFローバンド選択時はバラクタダイオード21の電圧−容量変化カーブのうち容量変化範囲の小さい領域を使用して共振信号を生成する。

(もっと読む)

電圧制御発振回路、及び、その調整方法

【課題】電圧制御発振回路、及び、その調整方法に関し、制御電圧に対する周波数の変化量を精度よく調整できる電圧制御発振回路を提供することを目的とする。

【解決手段】本発明は、制御電圧に応じて容量成分が制御される可変容量素子と、可変容量素子に直列に接続された直列容量素子と、可変容量素子と直列容量素子とから構成される直列回路に並列に接続された並列容量素子と、可変容量素子と直列容量素子とから構成される直列回路に並列に接続され、誘導成分を構成する誘導素子とを有する電圧制御発振回路において、直列容量素子及び並列容量素子は、各々その容量成分を切り換え可能な構成されており、直列容量素子の容量成分及び並列容量素子の容量成分を切り換えることにより、制御電圧に対する発振周波数の変化量が調整されていることを特徴とする。

(もっと読む)

電圧制御発振器

【課題】温度による発振周波数の変動を容易に補正することができ、かつ可変容量素子の両端に印加できる電圧範囲を高電圧側へシフトさせることができる電圧制御発振器を得る。

【解決手段】本発明に係る電圧制御発振器は、電圧制御発振部と、周波数制御バイアス回路と、温度補償バイアス回路と、温度補償バイアス発生回路とを備え、温度補償バイアス発生回路は、温度補償バイアス回路にコレクタ又はドレインが接続されたトランジスタと、トランジスタのコレクタ又はドレインに一端が接続され他端が接地された第1抵抗と、トランジスタのベース又はゲートに一端が接続された第2抵抗と、第2抵抗の他端に接続されたベース又はゲートバイアス印加用端子と、トランジスタのエミッタ又はソースに一端が接続された第3抵抗と、第3抵抗の他端に接続されたエミッタ又はソースバイアス印加用端子とを有する。

(もっと読む)

高周波発振装置

【課題】発振周波数の微調整が可能な高周波発振装置を提供する。

【解決手段】外部から印加される電圧によって容量値が調整可能な可変容量素子となるトランジスタTr2を含む共振回路を備え、共振回路から出力された高周波信号を受けて正帰還により発振信号を出力する高周波発振装置によって上記課題を解決することができる。

(もっと読む)

半導体集積回路装置

【課題】制御電圧の狭い変化範囲で安定に動作する電圧制御発振器を提供する。

【解決手段】電圧制御可能な可変容量回路12と、インダクタを有するインダクタ回路11と、負性抵抗回路13と、補正電圧を出力する容量制御回路14と、を備える。可変容量回路12とインダクタ回路11と負性抵抗回路13とを並列接続して発振回路を構成する。容量制御回路14は、発振回路における温度変動および/または電源電圧変動に対応して出力される補正電圧によって可変容量回路12におけるキャパシタンスを補正するように制御する。

(もっと読む)

間欠動作回路及び変調装置

【課題】小回路規模、低消費電力で、立ち上がりと立ち下がりの速い出力波形を得ることができる間欠動作回路を提供すること。

【解決手段】能動回路106と、能動回路106の動作開始と動作停止を制御する第1の制御信号S1を生成する第1の制御信号生成回路101と、能動回路106にリンギング振動を起こさせ、かつ、そのリンギング振動の周波数と振幅値を制御することができる第2の制御信号S2を生成する第2の制御信号生成回路102と、能動回路106からリンギング振動と安定振動が継続して出力されるように、第1及び第2の制御信号S1、S2の能動回路106への入力タイミングを調整するタイミング調整回路103とを設けるようにする。

(もっと読む)

1 - 20 / 29

[ Back to top ]