Fターム[5J098AA12]の内容

能動素子を用いた回路網 (5,588) | 回路素子 (1,159) | 抵抗 (319) | 可変抵抗 (46)

Fターム[5J098AA12]に分類される特許

1 - 20 / 46

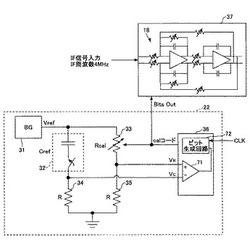

半導体集積回路、受信モジュール及び受信装置、並びに半導体集積回路の調整方法

【課題】CR積で変化する回路ブロック(例えば、IFローパスフィルタ)の特性を調整する工程を製品検査から削減できる、半導体集積回路、受信モジュール及び受信装置、並びに半導体集積回路の調整方法の提供。

【解決手段】可変抵抗33と、スイッチトキャパシタ32と、可変抵抗33とスイッチトキャパシタ32とのCR積の偏差を検出するRCキャリブレーション回路22と、可変抵抗33及びスイッチトキャパシタ32と同一チップに設けられた可変抵抗33と同じ構成の可変抵抗を持つIFローパスフィルタ18とを備える、半導体集積回路。

(もっと読む)

受信装置及び多重フィルタの制御方法

【目的】受信強度に拘わらず高精度な復調を行うことが可能な受信装置及び多重フィルタの制御方法を提供することを目的とする。

【構成】送信信号を受信して得られた周波数信号に対して、夫々が異なる周波数特性を有する複数のフィルタが直列に接続されてなる多重フィルタによって周波数選択処理を施すにあたり、受信強度が所定の閾値受信強度よりも高い場合には、複数のフィルタの内の少なくとも1つのフィルタの中心周波数を偏倚させる。

(もっと読む)

オーディオ機器

【課題】入力端子に接続されたソース機器に合わせて入力インピーダンスやゲインを設定可能なオーディオ機器を提供する。

【解決手段】ホット端子およびコールド端子を有しソース機器が接続される入力端子と、インピーダンス素子と、キャパシタと、テスト信号発生部と、リターン信号解析部と、通常動作時にインピーダンス素子を入力端子に並列に接続し、ソース機器のインピーダンス検出時にコールド端子にテスト信号発生部を接続するとともにホット端子にキャパシタおよびリターン信号解説部を接続する切替スイッチとを備え、ソース機器のインピーダンス検出時に、テスト信号発生部はテスト信号を発生し、リターン信号解析部はホット端子に戻ってきたテスト信号であるリターン信号に基づいてソース機器のインピーダンスを検出する。

(もっと読む)

時定数調整回路

【課題】参照用の時定数発生回路を集積回路の外部に用意すると、集積回路の端子数の増加および半導体チップ面積の増大を招き、その結果、製造コストが増大してしまう。また、集積回路単体では時定数の調整を行えない。

【解決手段】スイッチトキャパシタを用いることで、時定数発生回路を集積回路に内蔵しても十分な精度が保たれる。さらに、時定数の補正結果を記憶する記憶部を設けることで、時定数調整用回路と、時定数調整後の通常動作用回路を、一部兼用することが可能となる。集積回路の端子数と、半導体チップ面積を節約でき、その結果、製造コストを抑えられる。さらに、外部から電源さえ供給されれば、自動的かつ自律的に時定数の調整を行える。

(もっと読む)

受信装置及びイメージ除去方法

【課題】ウィーバー方式又はハートレー方式等のイメージ除去構成と複素フィルタを組み合わせて用いる場合に、希望信号及びイメージ信号の直交性を共に維持する。

【解決手段】直交ミキサ(ミキサ101及び102)は、RF信号をダウンコンバートし、I信号及びQ信号を生成する。複素フィルタ103は、正の周波数領域と負の周波数領域との間で非対称な周波数利得特性を有し、I信号及びQ信号に含まれるイメージ信号を希望信号に比べて抑圧する。直交補償回路106は、複素フィルタ103の後段に配置され、複素フィルタ103によってイメージ抑圧されたI信号及びQ信号の間における希望信号の位相差誤差及び振幅誤差を打ち消すように、I信号及びQ信号を補正する。また、制御回路117は、複素フィルタの後段にてI信号及びQ信号に現れるイメージ信号の位相差誤差及び振幅誤差を打ち消すように、複素フィルタ103の素子特性を調整する。

(もっと読む)

遅延回路及び電圧制御発振回路

【課題】電源ノイズにより遅延時間が影響を受けにくい遅延回路及び遅延回路を用いた電圧制御発振回路を提供する。

【解決手段】第1及び第2の電源端子と一対の差動信号入力端子と一対の差動信号出力端子とを備え、一対の差動信号入力端子から入力した信号を遅延させて一対の差動信号出力端子から出力する遅延部と、電流制御端子により制御された電源電流を遅延部の第1の電源端子と第2の電源端子との間に流すように制御する電流制御部と、第1及び第2の電源端子の電圧が一定の電圧になるように制御する電圧制御部と、を備える。

(もっと読む)

半導体装置

【課題】高い精度のインピーダンス調整回路を有する半導体装置を提供する。

【解決手段】可変抵抗回路と外部抵抗素子との分圧電圧と、基準電圧とを比較する差動増幅回路にオフセット調整回路を設ける。オフセット調整回路は、第1と第2オセット調整信号によりそれぞれオン/オフ制御されて上記差動増幅回路の第1と第2負荷抵抗に流れる電流を形成し、それぞれ並列形態にされた複数からなる第2と第3MOSFET群を有する。上記差動増幅回路の両入力に基準電圧を供給した状態にし、上記第2と第3MOSFET群に供給される第1オフセット調整信号による電流を変化させて上記差動増幅回路及びデジタル変換段を通した出力信号が変化した時点での第1オフセット調整信号又は上記第2オフセット調整信号をオフセット調整設定信号とする。

(もっと読む)

シュミットトリガ型インバータ

【課題】さらに入力ノイズ耐性を有するシュミットトリガ型インバータを提供すること。

【解決手段】入力側ノードへの供給電圧が増加して第1の基準電圧に達するに従い出力側ノードから出る電圧が比較高電圧レベルから比較低電圧レベルに遷移し、入力側ノードへの供給電圧が減少して第1の基準電圧より低い第2の基準電圧まで減少するに従い出力側ノードから出る電圧が比較低電圧レベルから比較高電圧レベルに遷移するインバータと、インバータの入力側ノードに一方端が接続された第1の抵抗素子と、インバータの入力側ノードに一方端が接続された、該一方端の電圧が上昇するほどに抵抗値が減じる可変抵抗素子と、可変抵抗素子の他方端に一方端が接続された第2の抵抗素子と、ドレインが第2の抵抗素子の他方端に接続され、ゲートがインバータの出力側ノードに接続され、ソースが接地電位に接続されたnチャネルMOSトランジスタとを具備する。

(もっと読む)

フィルタ回路

【課題】 可変する回路定数を減らし、かつ、回路定数の可変範囲を同じにしても、Qの変動が大きくならないようにする。

【解決手段】 VCVS型の2次HPF20B、30Bを縦続接続し、HPF20Bの内、抵抗値を大から小へ可変したときカットオフ周波数が低から高へ変化し、Qが大から小へ変化する抵抗R22と、HPF30Bの内、抵抗値を大から小へ可変したときカットオフ周波数が低から高へ変化し、Qが小から大へ変化する抵抗R32を互いに連動して抵抗値が可変するようにする。可変抵抗R22とR32を連動して可変したとき、各HPF20B、30BのQが相補的に変動するようにしたので、Qの変動を小さく抑えることができる。各HPF20B、30Bはカットオフ周波数の可変範囲、Qに対する設計自由度が高く、R22とR32の可変範囲を同じにしながらQがほぼ一定にすることができる。

(もっと読む)

フィルタ回路および無線機器

【課題】中心周波数を調整する周波数チューニングが容易に行えるフィルタ回路を提供する。

【解決手段】

本発明に係るフィルタ回路10は、チューニング時、スイッチ回路4を導通状態として、トランスコンダクタンス回路6を含むフィードバックループを有する発振回路8を構成する。発振回路8は、スイッチ回路4によりLCRタンク回路2をバイパスして、LCRタンク回路1とインダクタ3とを負荷回路としている。上記フィードバックループは、発振回路8の出力をトランスコンダクタンス回路6に入力する。スイッチ回路4を用いて以上のように発振回路8を構成することで、フィルタ回路10の中心周波数と発振回路8の発振周波数とが同一となる。それゆえ、特許文献1に開示されている自動チューニング技術を用いて容易に周波数チューニングを行うことができる。

(もっと読む)

インピーダンス調整回路

【課題】回路規模を縮減するインピーダンス調整回路の提供。

【解決手段】外付抵抗3と、被調整抵抗5のレプリカをなすレプリカ抵抗4の抵抗値の大小を比較するコンパレータ2と、抵抗制御回路10と、を備え、抵抗制御回路10は、コンパレータ2での比較結果に基づきカウント値をアップ・ダウンしレプリカ抵抗への制御信号を出力するレプリカ抵抗制御カウンタ11と、被調整抵抗5へ与える制御信号を保持する被調整抵抗制御信号保持回路12と、前記カウンタの状態と、前記保持回路の出力を入力し、レプリカ抵抗制御カウンタ11のカウント状態と被調整抵抗制御信号保持回路12の出力(Y)との値の差(|X−Y|)が予め定められた所定範囲内にあるときは、被調整抵抗制御信号保持回路12の出力(Y)を被調整抵抗制御信号保持回路(12)への入力(Z)として供給する監視回路13を備えている。

(もっと読む)

インピーダンス調整回路およびインピーダンス調整方法

【課題】インピーダンスを十分な精度で調整する。

【解決手段】一端を電源Vddに接続する抵抗11、12のそれぞれの他端をそれぞれ接続する端子13、14と、一端をスイッチ素子17を介して端子13に接続し他端を接地する可変抵抗素子19と、一端をスイッチ素子18を介して端子14に接続し他端を可変抵抗素子19の一端に接続する可変抵抗素子20とを備える。スイッチ素子17をオンとし、スイッチ素子18をオフとし、可変抵抗素子19の一端の電位が基準電圧となるように可変抵抗素子19の抵抗値を調整し、調整された可変抵抗素子19の抵抗値を維持して、スイッチ素子17をオフとし、スイッチ素子18をオンとし、可変抵抗素子20の一端の電位が基準電圧となるように可変抵抗素子20の抵抗値を調整する。

(もっと読む)

フィルタの調整回路

【課題】フィルタの特性を自動的に調整することが可能なフィルタの調整回路を提供する。

【解決手段】フィルタの調整回路は、積分器をn(n≧1)個含んだフィルタ回路と、予め設定された基準周波数を有する第1、第2の信号を出力する信号生成回路と、第1の信号をフィルタ回路が処理して出力した第3の信号の位相と第2の信号の位相とを比較し、これらの信号の位相のずれを判定する位相比較器と、フィルタ回路を制御する制御回路と、を備える。制御回路は、調整モードにおいて、フィルタ回路を積分器と等価な回路として動作させるとともに、位相比較器の判定結果に基づいて、第1の信号の位相回転が積分器1つあたり90°になるように、積分器を調整する。制御回路は、通常モードにおいて、第1の信号の位相回転が積分器1つあたり90°に調整された状態で、フィルタとして動作するように、フィルタ回路を制御する。

(もっと読む)

精密集積位相ロック回路用ループ・フィルタ

【課題】基準精密抵抗器と、第1のFETのゲートが第2のFETのゲートに結合されている第1のFETおよび第2のFETと、第1のFETに接続されコンデンサ電圧を発生させるフィルタ・コンデンサとを含む位相ロック・ループ回路内のループ・フィルタが提供される。

【解決手段】コンデンサ電圧は、第1のFETのソース、第2のFETのソース、および仮想グラウンドとして機能する基準精密抵抗器の底部に印加される。フィルタ・コンデンサによって生成されるコンデンサ電圧は、第2のFETが集積精密抵抗器の特性を含むように、第2のFETのバイアス点を設定する。第2のFETによって生成される所定の電圧は、第1のFETのゲートに印加されて、第1のFETが集積精密抵抗器の特性を含むように、第1のFETのバイアス点を設定する。

(もっと読む)

広帯域バンドパスフィルタ

【課題】 複数の狭帯域バンドパスフィルタを並列接続しても平坦で広い通過域を実現できなかった。

【解決手段】 中心周波数または遮断周波数をチャンネルの中心周波数から上下両側に所定の比率で離隔した周波数に設定した少なくとも一対のフィルタ10a〜10nを含む狭帯域バンドパスフィルタ11a〜11gを、共通信号入力端8と共通信号出力端9の間で並列的に接続する。

(もっと読む)

受信回路及び電子機器

【課題】PLLの低消費電力化、回路規模の低減、設計の困難性の低減。

【解決手段】所定の局部発振周波数IPA,QPAを出力する局部発振回路110を含み、受信信号RFと局部発振周波数IPA,QPAとを乗算した中間周波信号Iin,Qinを出力するアナログ直交復調回路100と、中間周波信号Iin,Qinを入力しフィルタ信号Iout,Qoutを出力する中心周波数と通過帯域とのどちらか少なくとも一方を可変にできる可変バンドパスフィルタ200と、フィルタ信号Iout,Qoutをデジタル信号Idi,Qdiに変換するアナログ−デジタル変換回路310,320と、所定の数値制御発振周波数IPB,QPBを出力する数値制御発振回路410を含み、デジタル信号Idi,Qdiと数値制御発振周波数IPB,QPBとを乗算した復調信号Idm,Qdmを出力するデジタル直交復調回路400と、を含む受信回路。

(もっと読む)

可変抵抗器及びこれを用いたフィルタ、可変利得増幅器及び集積回路

【課題】チューニング回路を必要とせずに位相遅れのばらつきを抑制可能な可変抵抗器を提供する。

【解決手段】シリコン基板上に形成され、入力端子と出力端子との間の抵抗値が変化する可変抵抗器において、前記入力端子にそれぞれの一端が共通に接続される複数の第1の抵抗Rと;前記第1の抵抗よりも小さな抵抗値を持ち、前記第1の抵抗の他端にそれぞれの一端が共通に接続される複数の第2の抵抗rと;前記入力端子と前記出力端子との間に挿入され、前記第1の抵抗から1つの抵抗を選択し、選択した第1の抵抗の他端に接続されている第2の抵抗から少なくとも1つの抵抗を選択するスイッチ部と;を具備する。

(もっと読む)

フィルタ回路

【課題】高精度かつ小面積なフィルタ回路を提供する。

【解決手段】例えば、バンドパスフィルタBPFと、BPFの周波数特性(中心周波数)を設定する制御部とを設ける。制御部は、基準周波数信号Frefと、Frefから2次ローパスフィルタLPFSを介した信号とを位相比較し、その結果をコンデンサC3に蓄え、C3の電圧を電流に変換してLPFSおよびBPFに帰還する。この帰還ループによって、LPFSの遮断周波数はFrefに収束する。ここで、BPF内の可変抵抗回路RVa,RVbおよびLPFS内の可変抵抗回路は、MOSトランジスタからなる差動アンプ回路で構成され、この差動アンプ回路のテール電流に前述した帰還電流が用いられ、相互コンダクタンスに基づいて抵抗値が制御される。そして、このような可変抵抗回路を含むフィルタ回路全体をCMOSプロセスで形成する。

(もっと読む)

受信機入力回路

【課題】周波数選択回路1と高周波入力段3間に2端子型浮動負性抵抗回路2を接続し、その負性抵抗により周波数選択回路1に形成される抵抗成分を打ち消すことにより受信機入力回路における雑音指数を大幅に低減できる受信機入力回路を提供する。

【解決手段】受信した高周波信号を選択する周波数選択回路1と、周波数選択回路1で選択した高周波信号を供給する高周波入力段3とを備える受信機入力回路において、周波数選択回路1と高周波入力段3間に2端子型浮動負性抵抗回路2を接続し、2端子型浮動負性抵抗回路2の負性抵抗により周波数選択回路1に形成される抵抗成分を打ち消すようにした。

(もっと読む)

インピーダンス調整回路およびインピーダンス調整方法

【課題】半導体装置と外部抵抗の間の線路に存在する寄生抵抗分を特別の回路を設けることなく補正することのできるインピーダンス調整回路およびインピーダンス調整方法を得ること。

【解決手段】LSIケース201の外部には、ケースピンを介してインピーダンス設定用のクランプ抵抗208と、これと電位を比較するための第1および第2の参照電圧生成抵抗221、222が接続されている。第1および第2の参照電圧生成抵抗221、222の間には、LSI202内の折り返し線225を経由する形で他の線路と同一幅の2本ずつの線路の寄生抵抗分からなる抵抗回路224が設けられており、調整に悪影響となる他の線路の寄生抵抗分をキャンセルする。このため、コンパレータ211の比較結果を使用して制御回路205はインピーダンス調整用出力バッファ203を高精度に調整可能である。

(もっと読む)

1 - 20 / 46

[ Back to top ]