Fターム[5J098AC10]の内容

能動素子を用いた回路網 (5,588) | 回路特性を可変するための構成 (1,170) | 可変方式 (226) | 離散的に可変 (96)

Fターム[5J098AC10]に分類される特許

21 - 40 / 96

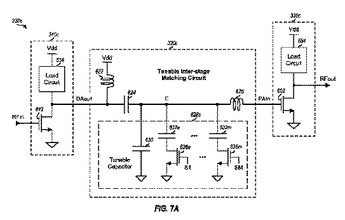

デジタルのチューナブル段間整合回路

性能を改善できるチューナブル段間整合回路について説明する。例示的な設計では、装置は、第1の能動回路(たとえば、ドライバ増幅器)と、第2の能動回路(たとえば、電力増幅器)と、第1の能動回路と第2の能動回路の間に接続されたチューナブル段間整合回路とを含む。このチューナブル段間整合回路は、第1の能動回路と第2の能動回路の間のインピーダンス整合を調整するために個別のステップで変化できるチューナブルキャパシタを含む。例示的な設計では、このチューナブルキャパシタは、(i)並列に接続された複数のキャパシタと、(ii)この複数のキャパシタに対してキャパシタごとに1つ接続された複数のスイッチとを含む。各スイッチは、関連するキャパシタを選択するためにオンにされるか、または関連するキャパシタの選択を解除するためにオフにされることができる。チューナブルキャパシタは、複数のキャパシタと並列に接続された固定キャパシタをさらに含むことができる。  (もっと読む)

(もっと読む)

半導体集積回路

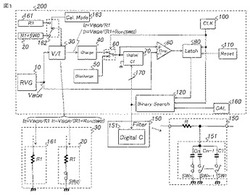

【課題】受信系チャンネル選択フィルタの高次フィルタおよび送信系ローパスフィルタの低次フィルタの周波数特性の不所望な変動を軽減する。

【解決手段】送受信機能をサポートする半導体集積回路は、所定の次数の受信系チャンネル選択フィルタと小さな次数の送信ローパスフィルタとキャリブレーション回路200を具備する。チャンネル選択フィルタの第1キャリブレーション動作の間に、抵抗スイッチ回路20が使用され電圧・電流変換器30は基準電圧を第1変換電流に変換して、時間積分器40、50は内蔵容量70の時間積分を実行して、電圧比較の結果がラッチ90に格納され、チャンネル選択フィルタの特性が決定される。ローパスフィルタの第2キャリブレーション動作の間に抵抗回路161が使用されて電圧・電流変換器30は基準電圧を第2変換電流に変換して、電圧比較の結果がラッチ90に格納され、ローパスフィルタの特性が決定される。

(もっと読む)

寄生容量により誘導される誤差が減少されたセンサデバイス

デバイス110は、駆動ノード34,36および感知ノード42,44を有する感知素子26を備えている。駆動ノード34および感知ノード42との間には寄生容量22が存在する。同様に、駆動ノード36と感知ノード44との間には寄生容量24が存在する。駆動信号56が駆動ノード34、36との間に印加されると、駆動ノード34と感知ノード42との間の寄生電流70および駆動ノード36と感知ノード44との間の寄生電流72が寄生容量22,24のおかげで生成される。容量性ネットワーク112を介して寄生電流70を打ち消す補正電流134を生成するために、駆動ノード36と感知ノード42との間に容量ネットワーク112が接続される。同様に、容量性ネットワーク112を介して寄生電流72を打ち消す補正電流138を生成するために、駆動ノード34と感知ノード44との間に容量性ネットワーク114が接続される。  (もっと読む)

(もっと読む)

抵抗値補正回路

【課題】外付けの基準抵抗と半導体集積回路に形成した抵抗の遅延量を比較して、半導体集積回路に形成した抵抗の抵抗値を補正する抵抗値補正回路を提供する。

【解決手段】半導体集積回路に形成した抵抗29と半導体集積回路の外部に設けられた基準抵抗33に予め設定された周期のクロック信号を入力し、抵抗29から出力された第1の信号A1と基準抵抗33から出力された第2の信号A2との遅延差を検出する遅延判定回路3と、直列接続される複数のフリップフロップにより構成されるフリップフロップ部に、遅延判定回路3で遅延差を計測開始と同時にクロック信号を入力し、フリップフロップごとに順次クロック信号を遅延させ、フリップフロップごとに遅延信号を出力し、遅延差が発生している期間に出力された遅延信号を選択して出力するばらつき検出回路と、を備える抵抗値補正回路1である。

(もっと読む)

インピーダンス調整回路及びこれを備える半導体装置

【課題】インピーダンス調整回路における調整誤差を低減する。

【解決手段】レプリカ回路1441,1443のインピーダンスをそれぞれ変化させるカウンタ回路1421,1422と、これらカウンタ回路のカウント値を更新するインピーダンス調整制御回路141とを備える。制御回路141は、レプリカ回路1441のインピーダンスが外部抵抗REのインピーダンスよりも低い状態から高い状態に変化したことに応答してカウンタ回路1421のカウント値更新を終了し、レプリカ回路1443のインピーダンスがレプリカ回路1441のインピーダンスよりも高い状態から低い状態に変化したことに応答してカウンタ回路1422のカウント値更新を終了する。これにより、レプリカ回路1441,1443にて生じる調整誤差が相殺される。

(もっと読む)

半導体装置

【課題】高い精度のインピーダンス調整回路を有する半導体装置を提供する。

【解決手段】可変抵抗回路と外部抵抗素子との分圧電圧と、基準電圧とを比較する差動増幅回路にオフセット調整回路を設ける。オフセット調整回路は、第1と第2オセット調整信号によりそれぞれオン/オフ制御されて上記差動増幅回路の第1と第2負荷抵抗に流れる電流を形成し、それぞれ並列形態にされた複数からなる第2と第3MOSFET群を有する。上記差動増幅回路の両入力に基準電圧を供給した状態にし、上記第2と第3MOSFET群に供給される第1オフセット調整信号による電流を変化させて上記差動増幅回路及びデジタル変換段を通した出力信号が変化した時点での第1オフセット調整信号又は上記第2オフセット調整信号をオフセット調整設定信号とする。

(もっと読む)

アクティヴインダクタ

【課題】出力電流雑音の変動しない可変型アクティヴインダクタを提供すること。

【解決手段】トランジスタのゲート−ソース間に並列に容量素子とスイッチを直列接続した素子を接続する。すなわち、PMOSトランジスタM2のドレインとキャパシタC1の一方の端子を接続する。また、端子VinとキャパシタC1のもう一方の端子にスイッチS1の一方の端子を直列接続し、スイッチS1のもう1方の端子をPMOSトランジスタM2のゲートと接続する。スイッチS1を開閉する事で見かけ上のトランジスタのゲート−ソース間容量を変化させてインダクタンス値を変動させるが、MOSトランジスタM1・M2の相互コンダクタンスは変化せず、そのため出力電流雑音は変らない。

(もっと読む)

フィルタ回路、連続時間フィルタ及び信号再生装置

【課題】周波数帯域を制限するフィルタ回路に関し、周波数とは、独立に利得を調整する。

【解決手段】第1の電圧/電流変換回路(12)に、係数設定回路(16)からの第1の制御信号と利得調整のための第2の制御信号とから作成した第3の信号を入力し、第2の電圧/電流変換回路(14)に、第1の制御信号を入力する。このため、周波数と、利得を独立に制御したフィルタを実現できる。

(もっと読む)

位相同期回路におけるループフィルタ

【課題】C/Nを改善することができる位相同期回路におけるループフィルタを提供する。

【解決手段】本発明の位相同期回路におけるループフィルタ1は、増幅回路2、第1のローパスフィルタ3、第2のローパスフィルタ4、電圧供給回路17、スイッチング素子5を備える。第2のローパスフィルタ4は、増幅回路2の出力端子2aと第1のローパスフィルタ3との間に接続され、バイアス電圧を供給する電圧供給回路17にも接続される。スイッチング素子5は、第2のローパスフィルタ4の接続状態を制御し、増幅回路2から出力された制御電圧が所定の電圧以下に降下したときに自動的にオンとなるように形成される。

(もっと読む)

フィルタ回路および通信装置

【課題】フライングキャパシタを備えるフィルタ回路において、急峻な減衰特性を備えることが可能なフィルタ回路を提供すること。

【解決手段】フライングキャパシタと、フライングキャパシタの入力端と出力端との間に、フライングキャパシタと並列に設けられるキャパシタと、を備えるフィルタ回路は提供される。フライングキャパシタの入力端と出力端との間に所定の容量を有するキャパシタを設けることで、フライングキャパシタを備えるフィルタ回路において、急峻な減衰特性を備えることが可能となる。

(もっと読む)

半導体集積回路

【課題】電源電圧の変化に依存する内蔵フィルタの周波数特性の不所望な変化を軽減すること。

【解決手段】半導体集積回路は校正回路200を具備し、内蔵容量70:151は容量とスイッチを有する。V・I変換器30、20は基準電圧を電流に変換して、電流に応答する時間積分器40、50は容量70の時間積分を実行して、電圧比較器80は基準電圧と内蔵容量70の端子電圧を比較する。校正動作の間に時間積分と電圧比較が実行され、その結果はラッチ90に格納される。校正動作の完了時のラッチ90の格納結果に従って、内蔵フィルタ150の周波数特性が決定される。V・I変換器30、20のスイッチ素子SW0のNチャンネルMOSトランジスタのゲートに、校正動作の間に安定化電圧VREFが供給される。

(もっと読む)

移相器

【課題】意図せずに信号線に付加される線路によって移相器の特性が劣化してしまうこと。

【解決手段】移相器50は、LPFとHPF間の切替に基づいて入力信号を移相する。移相器50は、入力端子1と出力端子2間に接続されたFET5と、FET5がオン状態のとき共振する共振回路と、FET5がオン状態のとき、入力端子1及び出力端子2間に形成される信号線路に含まれる節点と共振回路との間に接続される付加線路4a(4b)と、FET5がオン状態のとき、信号線路の一部に含まれ、少なくとも付加線路4a(4b)と共にローパスフィルタを形成するインダクタ3a(3b)と、を備える。FET5がオン状態のときに付加線路と共にLPFを形成するインダクタを信号線路に配置する。これによって、意図しない付加線路によって移相器の特性が劣化することを抑制することができる。

(もっと読む)

Gm−Cフィルタ回路及びこれを用いた送受信機

【課題】カットオフ周波数の補正動作中における後段回路の異常動作や電力浪費を解消することが可能なGm−Cフィルタ回路の提供。

【解決手段】Gm−Cフィルタ回路100は、カットオフ周波数の補正動作中に後段回路200への電力供給を停止させる電源遮断部(スイッチ112とこれを制御するフィルタ制御回路110)を有して成る構成とされている。

(もっと読む)

フィルタ回路

【課題】本発明は、フィルタリング特性調整機能を有するアナログフィルタを有するフィルタ回路に関し、アナログフィルタのフィルタリング特性を簡易な補正回路によって補正する機能を備える。

【解決手段】アナログフィルタ50と、レプリカ回路としての発振器61と、周波数比較ロジック62を備え、周波数比較ロジック62で、その発振器61の発振周波数が基準周波数となるように、発振器61とアナログフィルタ50との双方を同時に調整する。

(もっと読む)

周波数特性調整回路、受信インタフェース回路および磁気記憶装置

【課題】伝送路との整合を保持しながら交流結合回路による低域側遮断域を変化させる。

【解決手段】周波数特性調整回路20の遮断域調整部21は、AC結合回路10の周波数特性における低域側遮断域が移動するように、AC結合回路10からの出力信号を通過させる。遮断域調整部21の零点周波数および極周波数は、制御信号に応じて設定される。この制御信号により、遮断域調整部21の伝達関数の分子多項式が、AC結合回路10の伝達関数の分母多項式と等しくされ、遮断域調整部21の零点周波数が、AC結合回路10による低域遮断周波数に合わせられる。このため、AC結合回路10から遮断域調整部21を通過した出力信号は、AC結合回路10により生じた低域遮断域が移動した周波数特性を有するようになる。そして、この周波数特性において、制御信号に応じて設定される遮断域調整部21の極周波数が、移動後の低域側遮断域の遮断周波数となる。

(もっと読む)

無線受信機用半導体装置

【課題】マルチバンド無線受信機のバンドパスフィルタを集積回路で構成する場合に、回路規模が大きくなり、チップ面積が大きくなったり、製造コストが高くなる。

【解決手段】混合回路58は無線受信信号SRFをダウンコンバートして中間信号SIFを生成する。IFBPF60は、抵抗R及びキャパシタCを用いたRCアクティブフィルタで構成され、SIFから目的受信信号を抽出する。抵抗Rは、クロック信号SCLによって駆動されるスイッチトキャパシタからなる等価抵抗により構成される。SCLを生成するフィルタ制御クロック生成回路72は、SCLの周波数fCLを、目的受信信号が属するバンドに応じて切り換えることができる。IFBPF60の通過帯域は、クロック周波数fCLによる抵抗Rの等価抵抗値の切り換えにより、受信バンドに対応して変更できる。

(もっと読む)

フィルタ回路のトリミング方法

【課題】時定数が比較的短い高速なフィルタ回路について、トリミングを容易に行うことができるトリミング方法を提供する。

【解決手段】フィルタ回路4の出力端子に、パルス信号の出力状態が変化したことを検出すると、アクティブとなる検出信号を出力し続けるように構成されるパルス検出回路11を配置する。そして、フィルタ回路4の時定数を一定方向に漸次変化させながら、所定パルス幅のパルス信号を入力した場合、パルス検出回11路が検出信号を出力した時点に、フィルタ回路4に設定した時定数でトリミングを完了する。

(もっと読む)

映像信号多重伝送装置および映像信号多重伝送装置を用いた撮像装置。

【課題】映像信号多重デジタル伝送システムのケーブル長が延びたときの伝送波形を改善する。

【解決手段】一つの伝送路を時分割により、双方向にデジタル化した映像信号を送受する多重伝送装置において、送信側と受信側とにそれぞれ複数の増幅器を有し、受信側に波形等化器を有し、伝送路が長い場合は、送信側では抵抗で帰還回路を構成した電流帰還演算増幅器で高増幅度とし、受信側では、負入力の接地抵抗と、基本波周波数インピーダンスが負入力抵抗の約半分で3次高調波周波数インピーダンスが負入力抵抗の約3倍のフェライトビーズを電流帰還演算増幅器の出力と負入力間に設けた電流帰還演算増幅器とで基本波周波数以下の低周波数成分を減衰させ、3次高調波成分を増強する。伝送路が短い場合は、送信側も受信側も抵抗で帰還回路を構成した電流帰還演算増幅器で0dB(特性整合損失を除けば+6dB)の増幅度とする。

(もっと読む)

半導体集積回路

【課題】 内蔵フィルタの周波数特性の不所望な変化を軽減すること。

【解決手段】 半導体集積回路は校正回路200を具備して、内蔵容量70:151は、複数の容量およびスイッチを有する。V・I変換器20、30は基準電圧を電流に変換して、電流に応答する時間積分器40、50は容量70の充電または放電の時間積分を実行して、電圧比較器80は基準電圧と内蔵容量70の端子電圧とを比較する。校正動作の間に複数回の時間積分と複数回の電圧比較が順次に実行されて、順次に生成される複数回の電圧比較の結果はラッチ90に順次に格納される。校正動作の完了時点のラッチの格納結果に従って、内蔵容量70:151の複数のスイッチの各オン・オフ制御と内蔵フィルタ150の周波数特性とが決定される。V・I変換器は、スイッチ素子SW0を含む。内蔵容量70:151の複数のスイッチとV・I変換器のスイッチ素子は、MOSトランジスタである。

(もっと読む)

移相回路

【課題】低損失化を図ることができるとともに、小形化を図ることができる移相回路を得る。

【解決手段】第1の入出力端子1aと、第2の入出力端子1bと、第1の入出力端子1aと第2の入出力端子1bの間に接続された第1のスイッチング素子2aと、第1の入出力端子1aに一端が接続された第1のキャパシタ3aと、第2の入出力端子1bに一端が接続された第2のキャパシタ3bと、第1及び第2のキャパシタ3a、3bの他端とグランド4の間に接続された第2のスイッチング素子2bとを設けた。

(もっと読む)

21 - 40 / 96

[ Back to top ]