Fターム[5J098AC20]の内容

能動素子を用いた回路網 (5,588) | 回路特性を可変するための構成 (1,170) | 可変要素 (423) | スイッチ (137) | 電子的スイッチ (97)

Fターム[5J098AC20]に分類される特許

81 - 97 / 97

フィルタ回路、及び受信回路

【課題】比較的大きな時定数を持ち、フィルタ特性が可変可能で、且つ、LSI化が可能なフィルタ回路の実現。

【解決手段】フィルタ回路10は、LPFであり、抵抗R1及びコンデンサC1によりRCフィルタ(LPF)が形成されているとともに、抵抗R1の入力側にスイッチSW1が直列接続されている。スイッチSW1は、所定周期のパルス信号である制御電圧によってそのオン/オフが制御される。そして、フィルタ回路10の時定数は制御電圧のデューティによって可変され、この制御電圧のデューティが小さくなるに従ってフィルタ回路10の時定数は小さくなる。

(もっと読む)

出力装置および半導体レーザ変調駆動装置および画像形成装置

【課題】 信号伝送速度が高速化する場合にも、インピーダンス整合を正確にとることができ、その場合に、回路の大規模化等を有効に防止する。

【解決手段】 この出力装置1は、スイッチングによって出力信号を生成して伝送路(出力ノード)に出力するスイッチング部2と、出力装置1の出力インピーダンスを伝送路のインピーダンスに合うように調整するために設けられているインピーダンス整合部3と、出力装置1の出力インピーダンスを伝送路のインピーダンスに合うようにインピーダンス整合部3を設定する制御手段4とを有し、前記インピーダンス整合部3は複数のトランジスタ部により構成されている。

(もっと読む)

フィルタ調整方法及びフィルタ調整装置並びにフィルタ回路

【課題】アナログフィルタの特性を調整するためのフィルタ調整方法及びフィルタ調整装置並びにフィルタ回路に関し、簡単な構成で自動調整が行なえるフィルタ調整方法及びフィルタ調整装置並びにフィルタ回路を提供することを目的とする。

【解決手段】本発明は、アナログフィルタ(111)の特性を調整するフィルタ調整方法において、アナログフィルタ(111)に擬似ランダムビットパターンを供給し、アナログフィルタ(111)の出力と擬似ランダムパターンとの相互相関値を算出し、算出した相互相関値に基づいてアナログフィルタの特性を調整することを特徴とする。

(もっと読む)

イコライザ回路

【課題】構成が簡単で雑音が小さく、かつパラメータの調整が容易なイコライザ回路を提供すること。

【解決手段】イコライザ回路は、入力信号を増幅して出力する第1の増幅回路50、入力信号が印加されるフィルタ回路51、フィルタ回路51の出力信号が入力される第2の増幅回路52、第1の増幅回路50の出力信号と第2の増幅回路52の出力信号とを逆相で加算する加算回路53とを備える。フィルタ回路51と第2の増幅回路52の組を複数個備えていてもよい。更に、増幅回路の利得やフィルタ回路の特性を制御する等化特性設定回路54を備える。高精度あるいは低雑音の部品や素子が必要なく、回路構成が簡単である。また、回路が高域に敏感でなくなるので、低雑音化が図れる。更に、イコライザ回路の特性を連続的に変更可能である。

(もっと読む)

クロック信号発生回路

【課題】スイッチドキャパシタ回路の高速化の際に、スイッチドキャパシタ回路を動作させるために供給するクロックタイミングがばらつきや配線に付く寄生抵抗、容量によってはタイミング破綻を引き起こす。

【解決手段】スイッチドキャパシタ回路を動作させるために供給するクロック信号のボトムプレートサンプリング期間と、ノンオーバーラップ期間を制御手段により、タイミングを調整可能にする事により、タイミング破綻を回避する事が出来、且つ前記それぞれの期間を決定付ける論理素子の面積を増大させる事なく構成できる。

(もっと読む)

遅延回路及びそれを用いた映像信号処理回路

【課題】ドレイン・基板間の寄生容量を軽減させる。

【解決手段】充電用・放電用トランジスタとそれらのソースに接続された容量素子とを有したスイッチド・キャパシタ部を複数有し、入力信号が充電用トランジスタのドレイン各々に対して共通に入力され且つ容量素子を充電させるように接続されるとともに、放電用トランジスタのドレイン各々から容量素子を放電させて出力信号が出力されるように接続されるスイッチド・キャパシタ群と、充電用及び放電用トランジスタのゲート各々のオン・オフを制御して容量素子各々を入力信号に基づいて順次充電させるとともに、当該順次充電の際に前回充電しておいた容量素子を放電させることで出力信号を順次出力させるスイッチング制御部と、を有し、隣接する二つの前記スイッチド・キャパシタ部において、双方の充電用・放電用トランジスタ同士を隣接させ、双方の充電用・放電用トランジスタのドレインを共通させる。

(もっと読む)

フィルタ回路

【課題】 スイッチの切り替え時に出力端子にノイズ電圧が発生しないようにすること。

【解決手段】 演算増幅器1の非反転入力端子+を演算増幅器11を用いたボルテージフォロアDの入力端子+に接続し、このボルテージフォロアDの出力端子を第2のスイッチSW2を介してコンデンサC2と第1のスイッチSW1と間に接続し、更に、VAの電位をボルテージフォロアDでバッファした電位をVA*として、第1のスイッチSW1と第2のスイッチSW2とが逆相の動作を行うように制御するスイッチ制御回路Eを接続して、フィルタ回路を構成する。

(もっと読む)

時間アナログ対デジタル変換器に関するレール対レール遅延線

時間アナログ対デジタル変換器(TAD)はアナログ対デジタル変換のために時間対デジタルの手法を使用する。該TADのダイナミックレンジを増加させるために、例えばCMOSインバーターの連鎖のような2つの電圧対遅延変換器(VDC)を該TADは含む。各VDCは入力電圧の異なる範囲を扱うことが出来る。比較器は、入力電圧の異なる範囲に対応する複数の参照電圧に対し入力信号電圧を比較し、選択器は、入力信号が存在する範囲に基づいて複数のVDC線出力の中の一つを選択する。フィルターは、該選択された出力からの遅延信号から入力信号電圧を推定する。 (もっと読む)

チューニング回路

【課題】本発明はフィルタに関しフィルタ遮断周波数を補正するフィルタチューニング回路を提供する。

【解決手段】第1端子の印加電圧に比例して第2端子から第3端子に流れる電流を変化させる第1トランジスタと第1トランジスタに繋がれRC-是正数の抵抗を可変する可変抵抗部を含み、可変抵抗部により電流を変化させる電流発生部と第1トランジスタとカレントミラー回路を構成して第1端子の印加電圧に比例して第2端子から第3端子にミラー電流が流れる第2トランジスタと第2トランジスタの第3端子に繋がれRC−是正数の容量を可変する可変キャパシタ部を含み、可変キャパシタ部の容量を変化させるキャパシタンス補正部と可変抵抗部の抵抗またはキャパシタンス補正部の容量を可変する制御信号を送るアップダウンカウンタ及び抵抗又は容量を可変させるアップダウンカウンタの制御経路を選択する選択部を含む。

(もっと読む)

遅延回路

【課題】不必要なスイッチ素子の寄生容量を付加することなく容量値の変更を実現することで、広い可変範囲を持ちながら最小遅延が大きくならない遅延回路の提供。

【解決手段】この発明は、差動対となるN型のMOSトランジスタMN1,MN2と、電流源1と、遅延量を設定するための一対の遅延量設定部2、3とを備えている。遅延量設定部2は、キャパシタC0,C1,C2からなるキャパシタ群21と、このキャパシタ群21との間で電荷の充放電を行う抵抗として機能する2つのP型のトランジスタMP0,MP1と、スイッチSW0〜SW2と、スイッチSSW3,SW4とを備えている。スイッチSW0〜SW2は、MOSトランジスタMP0,MP1のうちの1つを選択的に有効化させる。スイッチSW3、SW4は、キャパシタC0に対して、キャパシタC1,C2を選択的に接続可能とするものである。

(もっと読む)

通信用半導体集積回路

【課題】 高利得増幅回路のフィルタ特性が製造プロセスによってばらついてもキャリブレーションにより補正することができる受信回路を内蔵した通信用半導体集積回路(高周波IC)を提供する。

【解決手段】 複数のロウパスフィルタ(LPF)と利得可変な増幅回路(PGA)が直列に多段接続されてなる直列信号処理回路(高利得増幅回路220)を内蔵した通信用半導体集積回路(高周波IC)において、上記直列信号処理回路を構成するロウパスフィルタの容量として、複数の容量素子とこれらの容量素子とそれぞれ直列に接続されたスイッチ素子とからなる可変容量回路を設け、例えば電源投入時に基準となるクロック信号を、上記ロウパスフィルタを含む回路に入れて回路の遅延時間が設計値に対してどの程度ずれているか判定して、遅延時間のずれが最小となるように上記可変容量回路のスイッチ素子のオン、オフ状態を設定するようにした。

(もっと読む)

フィルタ自動調整装置およびフィルタ調整方法ならびに携帯電話システム

【課題】調整機能を有するフィルタにおいて、高い調整精度をもち、かつ低消費電流化が容易なフィルタのバラツキ調整を可能にする。

【解決手段】位相差検出器104により、基準フィルタ103における前後の位相差をカウンタ106にてカウントし、基準フィルタ103のバラツキを検出する。そのバラツキの検出を複数回行い、判定回路110にてカウント数を選択することにより、より精度の高いフィルタ調整を行う。検出結果から得られる主フィルタ109の制御信号116(1)〜116(n)はレジスタ108に保持し、調整後はフィルタ調整に関する部材をすべて動作停止し、低消費電力化を図る。

(もっと読む)

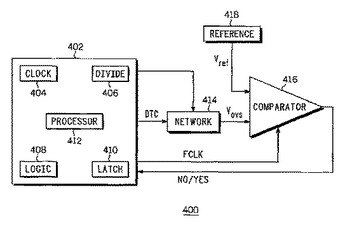

デジタル時定数トラッキング技術及び装置

プロセス、電圧及び温度の変動に起因して回路網(414)の時定数偏差を調整して雑音を無くす方法及び装置を提供する。当該装置(400)は、デジタル時定数が回路網(414)の公称時定数に対して相関されるクロック基準手段(404)を備える。相関されたデジタル時定数は、回路網(414)に印加され、そして出力充電/放電波形スイングが、所定の基準電圧と比較される。当該充電/放電波形スイングが基準電圧と一致しない場合、オフセット信号を発生する。オフセット信号が、制御回路(402)に印加され、当該制御回路(402)は、対応の同調信号を発生する。同調信号は、回路網(414)に印加されて、一致が達成されるまで内部部品を増分的又は減分的に調整する。当該装置(400)は、内蔵型で自己試験型のデジタル時定数トラッキング回路として構成されることでき、且つICチップ上に回路網(414)と一緒に統合化されることができる。  (もっと読む)

(もっと読む)

フィルタ

【課題】SCFを用いて構成されるLPFにおいて、SCFの後段にノイズ除去用のLPFを設けることなく、SCFで発生するノイズを軽減する。

【解決手段】LPF10は、対象信号finから高域成分を除去して出力信号S11を出力するSCF11と、対象信号finから高域成分を除去して出力信号S12を出力するSCF12と、出力信号S11,S12を互いに減算し、得られた信号を出力する減算部13とを備える。出力信号S11,S12は、それぞれ、対象信号finから高域成分が除去された通過信号に、各SCFで発生したノイズSn11,Sn12が重畳されてなる。SCF11,12は、各通過信号が互いに逆相となり、各ノイズSn11,Sn12が互いに同相となるように構成され、減算部13の減算によりノイズSn11,Sn12が互いに打ち消し合う。

(もっと読む)

可変減衰回路及び該可変減衰回路を用いた減衰制御システム

【課題】 減衰量の変化範囲においても歪みの発生が少ない可変減衰回路を提供する。

【解決手段】 入力端子11と出力端子12との間に縦続接続して介挿された二つのスイッチ素子13、14と、スイッチ素子13、14の出力端子12側の一端をグランドにシャントする充電コンデンサ15、16とを備え、スイッチ素子13、14にそれぞれ放電抵抗17、18を並列接続し、スイッチ素子13、14を減衰量に対応した繰り返し周波数でオン/オフすることで信号を断続し、オン時に信号の電圧を充電コンデンサ15、16に充電し、オフ時に放電抵抗17、18で放電した。

(もっと読む)

アクティブフィルタの周波数調整回路及びその半導体集積回路

【課題】回路の消費電力を減らし、かつ回路規模の小さいアクティブフィルタの周波数調整回路を提供する。

【解決手段】積分回路13は、周波数調整回路11の制御対象のgmCフィルタの相互コンダクタンス増幅器21とバイアス回路22及び可変容量回路23と同一の回路で構成されている。デジタル制御回路16は、積分回路13の入力信号と出力信号から得られる直流電圧を比較して、電圧差に応じたデジタルデータを可変容量回路23に出力して容量値Cを変化させる。これにより、積分回路13のカットオフ周波数が基準周波数と一致、もしくは比例するように調整される。

(もっと読む)

半導体装置、無線端末装置及び無線通信機器

第1の性能に合わされた第1のアナログ回路(53)と、上記第1のアナログ回路と協働することで上記第1の性能より高い第2の性能を実現する第2のアナログ回路(55)とを有し、第1の性能が要

求される場合には第1のアナログ回路を動作させるとともに第2のアナログ回路への電源供給を遮断し、第2の性能が要求される場合には第1のアナログ回路及び第2のアナログ回路をともに動作させるようにして、第1のアナログ回路を共有することにより回路規模の増大を抑制しながらも、要求される性能に応じて回路特性を適切に切り替えることができるようにする。

(もっと読む)

81 - 97 / 97

[ Back to top ]