Fターム[5J106CC35]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | 周波数比較(弁別)回路 (250) | 複数の周波数比較(弁別)回路 (13)

Fターム[5J106CC35]に分類される特許

1 - 13 / 13

インテグレーテッドPLLを備えたPWMコントローラ

【課題】PWMコントローラチップのサイズ、コスト及び製造上の複雑を減らす。

【解決手段】位相ロックループ(PLL)を用いた電子部品に電力を供給するためのパルス幅変調(PWM)コントローラが、提供される。PWMコントローラは、基準信号を受信する入力ノードと、位相ロックループ(PLL)とを備えている。このPLLは、位相信号を受信し且つ前記誤り訂正信号に関係する周波数を有する発振器信号を生成する発振器と、前記発振器に結合され、前記基準信号を受信し、且つ前記基準信号と、フィードバック信号との間の位相差に基づいて前記位相信号を生成させる位相周波数検出器(PFD)と、前記PFDに結合され、周期的にPFDが前記位相信号を生成することができるようにする抑制回路と、前記PFDに結合され、前記位相信号が同時に活性である時間の長さを制限するように動作可能なフィードフォワード回路とを備えている。

(もっと読む)

クロック発生装置

【課題】広い温度範囲で高精度なクロック信号を出力可能な、安価でかつコンパクトなサイズのクロック発生装置を提供する。

【解決手段】クロック発生装置は、基準クロック信号を生成する基準クロック生成部11と、第1のクロック信号を生成する第1の発振器12と、前記第1のクロック信号を前記基準クロック信号と同周波数、同位相となるように補正した第2のクロック信号を生成する第1の精度保証部13と、温度検知部15と、第3のクロック信号を生成する第2の発振器17と、前記第3のクロック信号を前記基準クロック信号と同周波数、同位相となるように補正した第4のクロック信号を生成する第2の精度保証部18と、温度が第1の発振器12の保証温度範囲内の場合には前記第2のクロック信号、保証温度範囲外の場合には前記第4のクロック信号を出力するクロック切替部20と備える。

(もっと読む)

半導体集積回路

【課題】チップ面積の更なる縮小化を図ることができる半導体集積回路を提供する。

【解決手段】ディジタル制御発振器50−1〜50−nと、位相データ出力部100−1〜100−nと、積分処理部150と、フィルタ部151と、フィルタ部151からの時分割された出力信号に所定の係数を乗算した値を発振器制御値OTWとして出力する乗算器(第1の乗算器)40と、リファレンス周波数Frefに同期して、発振器制御値OTWを各ディジタル制御発振器50−1〜50−nに振り分ける出力セレクタ(制御値分離部)42と、を備える。

(もっと読む)

量子周波数標準器及び時刻制御システム

【課題】簡素な回路構成で低消費電力の量子周波数標準器。

【解決手段】化学結合している原子核間のスピン−スピン相互作用によって複数に分裂したエネルギー準位を有する物質110を含む容器120と、容器120に磁場を与える磁場発生源MGと、容器120に電磁波を照射する発振器150と、を含む核磁気共鳴部100と、核磁気共鳴部100から出力される共鳴信号RSからエネルギー準位の核磁気共鳴周波数f1を検出し第1検出信号SD1として出力する第1検出部200と、共鳴信号RSから隣り合うエネルギー準位間のエネルギー差であるスピン結合定数Jを検出し第2検出信号SD2として出力する第2検出部300と、第1検出信号SD1と第2検出信号SD2に基づき核磁気共鳴部100を駆動する駆動信号DSを生成する駆動信号生成部400と、を含み、第2検出部300は、第2検出信号SD2に基づき標準周波数信号SOを出力する。

(もっと読む)

周波数シンセサイザ

【課題】広帯域を細かく設定でき、周波数の引き込み範囲が広い周波数シンセサイザを提供する。

【解決手段】電圧制御発振部の出力周波数の正弦波信号を直交検波し、検波に用いた周波数信号の周波数との差分の周波数(速度)で回転するベクトルを利用したPLLにて、周波数引き込み手段は、PLLから電圧制御発振部への制御電圧が予め設定した設定範囲よりも大きい場合には、出力周波数を上昇させるための第1の定数を引き込み用電圧として積分し、また当該制御電圧が前記設定範囲よりも小さい場合には、出力周波数を低下させるための第2の定数を引き込み用電圧として積分する。そして加算手段は、PLLからの制御電圧と周波数引き込み手段からの引き込み用電圧とを加算し、電圧制御発振部へ出力する。

(もっと読む)

PLL発振回路

【課題】分数分周型のPLL発振回路における抵抗やキャパシタの定数を小さくすると共に、雑音を低減する。

【解決手段】入力信号INと帰還信号FBaの周波数の差に応じた電流を共通のノードNcに出力する周波数比較器10aと、入力信号INと帰還信号FBbの周波数の差に応じた電流を共通のノードNcに出力する周波数比較器10bと、このノードNcに出力される信号の高周波成分を除去して制御電圧VCを生成するループフィルタ20と、制御電圧VCに応じた周波数foの出力信号OUTを生成するVCO30と、出力信号OUTの周波数をそれぞれ1/Mと1/Nに分周して帰還信号FBa,FBbを出力する分周器40a,40bを設ける。

(もっと読む)

チップ、マイクロプロセッサーチップ、システム、

【課題】発生器クロックを供給するクロック発生器を提供する。

【解決手段】クロック発生器は、クロック分配網へ、第1のクロックを供給する第1のクロック源、及び少なくとも間接的に電源に従う周波数を有する第2のクロックを供給する第2のクロック源を有する。クロック発生器は、第2のクロックが第1のクロックより進んでいる場合、発生器クロックとして第1のクロックを、第2のクロックが第1のクロックより遅れている場合、第2のクロックを選択的に供給する。

(もっと読む)

自動周波数制御ループ回路

【課題】高い精密度を有しながら周波数を広帯域で発振させることができる自動周波数制御ループ回路を提供すること。

【解決手段】基準周波数を発生させるクロック発振部と、基準周波数を第1分周比で分周する第1分周器、発振周波数を第2分周比で分周する第2分周器、第1分周器によって分周された第1分周周波数と第2分周器によって分周された第2分周周波数との間の位相差を検出する位相検出器、位相差に対応して発振周波数を発生させる電圧制御発振器と、入力周波数と発振周波数に対応して出力周波数を出力する周波数変換器を含む周波数合成部と、出力周波数を設定周波数と比較して誤差を検出する誤差検出器、誤差を積分する積分器と、積分器の積分値に対応する制御信号を計算する演算器を含む復調部とを含み、制御信号に応じて第1分周比及び第2分周比を変更して誤差を補正することを特徴とする。

(もっと読む)

スプレッドスペクトルクロック生成器及びスプレッドスペクトルクロック信号を生成する方法

【課題】スプレッドスペクトルクロック生成器(SSCG)及びスプレッドスペクトルクロック(SSC)信号を生成する方法を提供する。

【解決手段】第1フィードバック信号の平均周波数と受信された比較周波数信号との差に基づくか、第2フィードバック信号と比較周波数信号との総位相変化量に基づいて所定の変調電圧信号を出力する制御部、受信された既存周波数信号及び受信された第2フィードバック信号の機能で第1制御電圧を生成するサブシステムを備えるSSCGである。合算部は、第1制御電圧信号と変調電圧信号とを合算して第2制御電圧信号を生成し、電圧制御オシレータは、第2制御電圧信号に基づいてSSC信号を生成する。

(もっと読む)

タイミング抽出回路

【課題】 メインVCOにおいてデータとの位相同期を瞬時に行なうことができるタイミング抽出回路を提供する。

【解決手段】 バーストデータからタイミングを抽出する回路において、データとの同期をとるメインVCO1の発振周波数とメインVCO1への制御信号を生成するサブVCO2の発振周波数とを周波数比較器4を用いて比較し、周波数差に応じた制御信号12を用いて両発振周波数を自動的に一致させるフィードバックループを設けることで、バーストデータに対して瞬時に応答することを可能とする。

(もっと読む)

広帯域周波数を発振する装置および方法

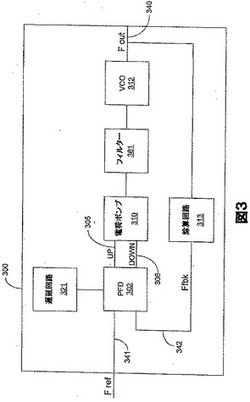

図5に示すような、位相ロックループと可変周波数分割器(560)とを備えた、周波数を発振する装置が示されている。可変周波数分割器(560)は、第1の周波数の信号をある分割比で分割して第2の周波数(Fout)の信号を発生し、この周波数分割は、位相/周波数検出器(510)へ入力される参照周波数クロック入力(Fref)とフィードバック周波数の信号入力との比較に基づいて行われる。チャージポンプ(520)およびループフィルタ(530)が、第2の周波数の信号(355)を分割して正しいフィードバック周波数の実現を可能にする分割器(550)とともに示されている。VCO(540)には、選択されるキャパシタを備える共振回路と、動作周波数を設定する制御電圧と、適当な利得のための能動回路(320)とが内在する。  (もっと読む)

(もっと読む)

平衡型4相相関器を備えたPLL

平衡型4相相関器(2)を含む周波数検出器(10)を具備する位相ロックループ(1)であり、ループ(1)は4相相関器(2)が入力信号(D)と同じビットレートを有する信号によって制御されるマルチプレクサ(31,32,33,34)に接続されたダブルエッジクロック式双安定回路(21,22,23,24,25,26,27,28)を具備することを特徴とする。  (もっと読む)

(もっと読む)

位相検出器

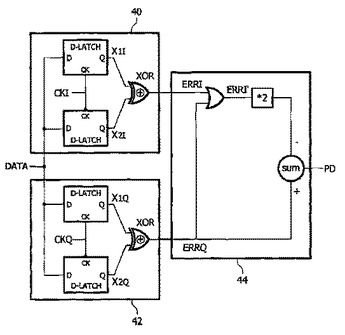

本発明は、データ信号DATAを用いてデータクロックDATA-CLKと参照クロックREF-CLKとの間の位相差を検出する位相検出器に関する。データ信号DATAの遷移は、データクロックDATA-CLKの遷移と同期している。データクロックDATA-CLK及び参照クロックREF-CLKは同じ周波数を持つ。位相検出器は、第1のバイナリ信号ERRQを生成する第1の信号生成器を有する。そのパルス幅は、データ信号DATAの遷移とデータ信号DATAの遷移に隣接する第1の参照クロック信号CKQの遷移との間の第1の時間差ΔT1に等しい。第1の信号生成器は、第1の参照クロック信号CKQを受信する入力と、データ信号DATAを受信する入力とを有する。位相検出器は、第2のバイナリ信号ERRIを生成する第2の信号生成器を有する。第2のバイナリ信号ERRIのパルス幅は、データ信号DATAの遷移とそのデータ信号DATAの遷移に隣接する第2の参照クロック信号CKIの遷移との間の第2の時間差ΔT2に等しい。第2の信号生成器は、第2のバイナリ信号ERRIを受信する入力と、第2の参照信号CKIを受信する入力とを有する。位相検出器は、データクロックDATA-CLKと参照クロックREF-CLKとの間の位相差を表す出力信号を生成する出力信号生成器を有する。出力信号は、ANDが論理AND演算を表すとき、ERRQ-2*(ERRQ AND ERRI)に等しいか、又はXORが論理XOR演算を表すとき、(ERRQ XOR ERRI)-ERRIに等しい。  (もっと読む)

(もっと読む)

1 - 13 / 13

[ Back to top ]