Fターム[5J106CC54]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | 周波数変換回路 (1,116) | 逓倍回路 (59)

Fターム[5J106CC54]に分類される特許

41 - 59 / 59

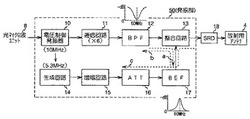

発振器及びルビジウム原子発振器

【課題】逓倍回路側と発振増幅器側にそれぞれフィルタを備えることにより、簡単な回路

構成で両回路のアイソレーションを高く保つことが可能となり、調整時間を短縮して調整

コストの低減を図った発振器及びルビジウム原子発振器を提供する。

【解決手段】発振部50は、電圧に基づいて発振周波数が制御される電圧制御発振器10

と、発振信号の周波数を逓倍する逓倍回路11と、所定の周波数を選択的に通過させる帯

域通過フィルタ12と、前記電圧制御発振器10により発振された発振信号を5.3MH

zに周波数変換する生成回路14と、生成回路14の出力レベルを増幅する増幅回路15

と、所定の減衰値を有する減衰器16と、所定の周波数を選択的に阻止する帯域阻止フィ

ルタ17と、周波数成分をインピーダンス整合して合成する整合回路13と、を備えて構

成されている。

(もっと読む)

原子発振器、受動形原子発振器、原子発振器の温度制御方法及び受動形原子発振器の温度制御方法

【課題】ガスセルの温度を一定に制御するために、CPT共振がないときの共鳴周波数に

おける光検出出力値を記憶しておき、温度補正時に記憶した光検出出力値になるように温

度制御することにより、簡単に且つ正確に量子レベルでの温度制御を可能とした原子発振

器を提供する。

【解決手段】この光学系110は、ガス状の金属原子を封入したガスセル3aと、ガスセ

ル3aを保持するガスセル保持部材3と、ガスセル保持部材3を加熱するヒータ(加熱手

段)7と、ガスセル3a中の金属原子を励起するコヒーレント光源1と、ガスセル3aを

透過した光4を検出する光検出器(光検出手段)5と、光検出器5により検出された光4

の強度に基づいてヒータ7を制御する温度制御部(温度制御手段)8と、を備えて構成さ

れている。

(もっと読む)

高周波信号発生装置

【課題】数MHzから数GHzの周波数領域にわたる高周波信号を、非常に低いSSBノイズで安定して発生することができる高周波信号発生装置を提供する。

【解決手段】搬送波周波数f1の1/nにほぼ相当する第1高周波信号aを発振する高周波発振器11と、搬送波周波数f1にほぼ相当する第2高周波信号eを発振する電圧制御発振器15と、電圧制御発振器15の出力周波数fを1/nに分周する分周回路16と、第1高周波信号aと出力周波数fの1/nの第2高周波信号gの位相差に比例した誤差信号Veを出力する位相比較器12と、誤差信号Veに応じて制御電圧を電圧制御発振器15に入力するVCO制御回路13とを備え、VCO制御回路13は、SSBノイズが第1高周波信号aの方が第2高周波信号eのものより小さい周波数帯域では、誤差信号Veに比例する制御電圧を出力し、大きい周波数帯域では制御電圧を0にする。

(もっと読む)

通信用半導体集積回路

【課題】送受信動作に使用する周波数シンサセイザとしてフラクショナルN PLL回路を含むRF通信用半導体集積回路において、PLL回路のチャージポンプ回路CPCのソース電流注入トランジスタとスィンク電流放出トランジスタとのミスマッチに起因する非線型性の影響を軽減する一方、PLL回路の位相ノイズを低減するための補償回路の回路規模を小さくして補償回路の制御も単純化すること。

【解決手段】受信動作と送信動作とに使用する周波数シンサセイザFrct_SynthとしてフラクショナルN PLL回路のクローズドループ帯域を、数十KHzのオーダーの狭帯域とする。チャージポンプ回路CPCの2つのトランジスタのミスマッチに起因する非線型性の影響の軽減を最も段純な方法であるオフセット回路MN2、MN3によるループフィルタLFCへのdc直流電流Ioffsetの注入もしくはLFCからのIoffsetの放出によって実現する。

(もっと読む)

デジタル放送受信装置およびデジタル放送システム

【課題】本発明は、可変周波数の水晶発器(VCXO)を用いること無く、基地局と受信装置間の時間情報および基準クロックの同期を実現することができる、デジタル放送受信装置等を提供する。

【解決手段】水晶発振子22は、所定の固定周波数のクロックを発振する。可変デジタル分周回路24は、固定周波数を分周比によりデジタル分周し、分周比を変更することができる。システムでコーダ5は、基地局からの基準時間情報を検出する。基準カウンタ18は、受信装置20の時間情報を生成する。位相比較器13は、基準時間情報と時間情報との差分を検出する。分周比制御回路25は、前記差分に基づいて前記分周比の変更を制御する。また、基準カウンタ18は、可変デジタル分周回路24により分周された周波数を有するクロックに基づいて時間情報の生成を行い、時間情報を位相比較器13にフィードバックさせている。

(もっと読む)

通信用半導体集積回路

【課題】基準周波数発振器DCXOの発振出力信号をレベル変換器Lev_Convによりレベル変換する際に発生するDCXOの発振出力信号の高調波成分によるRF送信用電圧制御発振器TXVCOの発振出力信号の近傍への漏れ込みによる影響を低減すること。

【解決手段】レベル変換器Lev_ConvはDCXOの発振出力信号をレベル変換して、レベル変換信号をRF送信用電圧制御発振器TXVCOの発振周波数を制御するPLL・フラクショナルシンセサイザFrct_Synthの位相比較器PDCに供給する。このLev_Convは、基準周波数発振器DCXOの基準周波数信号を増幅する自己バイアス型電圧増幅器Self_Bias_Volt_Ampを含む。自己バイアス型電圧増幅器は、結合容量C1、増幅トランジスタQn5、負荷Qp5、バイアス素子R1を含み、外部電源電圧Vdd_extが変動しても、高調波成分のレベル変動を抑制する。

(もっと読む)

情報記録再生装置、およびその記録クロック生成方法

【課題】ウォブル信号に同期して生成される記録クロックの周波数安定化を簡素な構成で実現することができる情報記録再生装置を提供する。

【解決手段】本発明に係る情報記録再生装置は、光ディスクに記録クロックを用いてデータを記録する情報記録再生装置において、光ディスクの再生信号から抽出されるウォブル信号によるフェーズロック制御に基づいて周波数制御され、記録クロックの発振源となるVCOと、VCOの周波数変動量を検出する周波数変動検出部と、を備え、VCOは、フェーズロック制御に基づく周波数制御に加えて、周波数変動検出部にて検出される周波数変動量に基づいて周波数制御される、ことを特徴とする。

(もっと読む)

PLL回路

【課題】複数の位相誤差出力をもつ特殊なVCOを備えること無しに、間欠的に記録され、データの先頭部に同期引き込みパターン領域を有するデータに対し、高速での引き込みを可能とするPLL回路を提供する。

【解決手段】PLL回路において、ADコンバータ4と、ADコンバータ4の出力信号から位相誤差を算出する位相比較器5と、周波数系フィルタ6と、位相系フィルタ7と、所定のタイミングで位相比較器5で算出された位相誤差の読み取りを行い、その読み取り値に応じた出力を発生する位相誤差読み取り手段8および位相誤差変換手段9と、周波数系フィルタ6の出力、位相系フィルタ7の出力、および位相誤差変換手段9の出力を加算する加算器10と、DAコンバータ11と、DAコンバータ11の出力電圧に基づいてADコンバータ4のサンプリングクロックとして使用される発振出力を出力するVCO12とを備えた。

(もっと読む)

マイクロコンピュータ

【課題】温度が変化する環境下において、CR発振回路を利用して生成されるクロック信号の発振周波数自体が一定となるように補正できるマイクロコンピュータを提供する。

【解決手段】マイクロコンピュータのEEPROMに、温度により変動するCR発振回路の発振周期データを記憶しておき、CPUは、温度検出回路によって検出される温度に応じてEEPROMに記憶されているデータを読み出し(ステップS2,S3)、決定した逓倍値をDPLL回路に設定することで(ステップS4,S5)逓倍クロック信号の発振周波数を補正する。

(もっと読む)

クロック再生装置

【課題】本発明はクロック再生装置に関し、バーストモードに対応でき、また10Gbps以上の高速通信の場合にも安定に発振することができるクロック再生装置を提供することを目的としている。

【解決手段】入力データを受けて該入力データからパルスを作成するパルス作成回路20と、ゲート付きオッシレータ31と、該ゲート付きオッシレータ31の出力と基準クロックとを比較し、その比較結果により前記ゲート付きオッシレータ31に遅延時間を設定するための位相制御信号を与える周波数コントロール回路32から構成されるクロック再生回路30と、によりなり、前記パルス作成回路20の出力で前記ゲート付きオッシレータ31をリセットすると共に、当該ゲート付きオッシレータ31の出力をクロック再生出力とするように構成される。

(もっと読む)

クロック再生装置

【課題】本発明はクロック再生装置に関し、バーストモードに対応でき、また20Gbps以上の高速通信の場合にも安定に発振することができるクロック再生装置を提供することを目的としている。

【解決手段】ゲート付きオッシレータ25と、該ゲート付きオッシレータ25の出力と基準クロックの位相とを比較し、その比較結果により前記ゲート付きオッシレータ25に遅延時間を設定するための位相制御信号を与える周波数コントロール回路26から構成されるクロック再生回路10と、によりなり、前記ゲート付きオッシレータ25は内部に2系統の発振回路を有しており、該ゲート付きオッシレータ25のリセット入力端子に入力データを入力し、該入力データが“H”の時と“L”の時とで異なるルートの発信回路を動作させるように構成される。

(もっと読む)

クロック生成回路

【課題】逓倍回路から正確な逓倍クロックが出力されず、温度等の変動に対する補正能力が低下し、ロックが困難になるという課題があった。

【解決手段】互いに直列に接続された複数個の遅延素子から構成されるデジタルディレイライン56,69,71を有し、デジタルディレイライン56,69,71に対応したカウンタ52,65から出力されるカウント値に応じて複数の遅延素子のいずれかの遅延を選択し、選択した遅延素子およびこれに隣接する1つの遅延素子によって遅延時間を設定制御する。

(もっと読む)

半導体集積回路装置

【課題】

ジッタが少なく安定に動作する高い逓倍比を持つ回路を提供する。

【解決手段】

逓倍回路10は、入力クロック信号CLKと入力クロック信号CLKをm逓倍したクロック信号とを選択して出力するセレクタ回路15を備える。PLL回路20は、セレクタ回路15が出力するクロック信号と帰還クロック信号とを位相比較する位相差検出回路21と、位相差検出回路21が出力する位相差信号を入力するチャージポンプ回路22と、チャージポンプ回路22が出力する信号の低域成分を取り出して出力するローパスフィルタ23と、ローパスフィルタ23の出力レベルに応じた周波数で発振する電圧制御発振器24と、電圧制御発振器24の出力クロックを入力してn分周して帰還クロック信号として出力する分周器25と、を備える。

(もっと読む)

多周波出力位相同期発振器

【課題】一つの位相同期回路を用いて多周波の出力信号を得ることが可能な多周波出力位相同期発振器を提供することを目的とする。

【解決手段】本発明に係る多周波出力位相同期発振器6は、外部から入力される基準信号と、後述する電圧制御発振器が出力する信号を分周した比較信号とを位相比較し位相差信号を発生する位相比較器2と、前記位相差信号の高周波成分を除去して直流電圧とするループフィルタ3と、ある一定の自走周波数を有し、前記直流電圧により発振周波数を変化させる電圧制御発振器4と、該電圧制御発振器4が出力する信号の周波数を複数の分周器のトータルで1/N分周し、前記位相比較器2に出力する分周器7、8、9、10とにより構成する。

(もっと読む)

分周回路およびデジタルPLL回路

【課題】出力信号に生じるジッタ量を抑えることができる分周回路を提供する。

【解決手段】直列に接続されたD−FF7,9,11を、入力信号S0を基準クロック信号として駆動し、分周比決定信号S21によって選択された分周比で入力信号S0を分周して第1の分周信号S7を生成する回路モジュール3と、直列に接続されたD−FF47,49,51,53を、第1の分周信号S7を基準クロック信号として駆動し、当該直列に接続されたD−FFの段数に応じた分周比である8分周で、第1の分周信号S7を分周して出力信号S57を生成する回路モジュール45と、回路モジュール45のD−FFの出力および4/5選択信号S24に基づいて、分周比決定信号S21を生成するOR回路55とを有する。

(もっと読む)

通信装置

【課題】複数回の周波数変換を行う通信装置において、周波数変換に用いる局部発振器の数を削減する。

【解決手段】送信系において、第1の周波数シンセサイザ51では、基準信号と帰還ループにより帰還された第1の出力信号(F4)との位相差に応じて該基準信号と同期した該第1の出力信号(F4)を出力し、第2の周波数シンセサイザ52では、該第1の出力信号(F4)と帰還ループにより帰還された第2の出力信号(F5)との位相差に応じて該第1の出力信号(F4)と同期した該第2の出力信号(F5)を出力する。そして、第1の周波数変換器1では、入力される第1の周波数信号(F1)を該第1の出力信号(F4)の周波数に従って第2の周波数信号(F2)に変換し、第2の周波数変換器2では、該第2の周波数信号(F2)を該第2の出力信号(F5)の周波数に従って第3の周波数信号(F3)に変換して送信する。

(もっと読む)

クロック発生装置

【課題】従来のクロック発生回路は1種類のクロックの発生しかできず、複数クロックに対応できなかった。また、同期信号とクロックとの位相関係によってテレビ受像機などの映像端末の性能を引き出せていなかった。

【解決手段】周波数意位相誤差演算回路120を設け、DTO10の周波数情報と位相比較器7、デジタルLPF8よりの位相誤差情報よりDTO10でバーストロックに同期したクロックだけでなく、ラインロックしたクロックをDTO121で同時に発生でき、複数のクロックが必要なシステムに対応でき、周波数拡散情報発生回路90で拡散情報を作り、DTO121にて加算することで容易に周波数拡散ができ、クロックよりの映像端末に対する妨害を減らすことができ、テレビ受像機などの映像端末の性能を引き出すことができる。

(もっと読む)

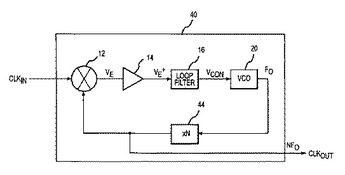

低電力と低いタイミング・ジッタのフェーズ・ロック・ループと方法

フェーズ・ロック・ループは、入力クロック信号から出力クロック信号を生成する。出力クロック信号は、クロック・ツリーを通して結合されて、出力クロック信号の位相を入力クロック信号の位相と比較する位相検出器にフィード・バックされる。出力クロック信号は、位相検出器から出力を受け取るように結合された制御入力を有する電圧制御発振器と、電圧制御発振器の出力に結合された周波数逓倍器とによって生成される。を持っている電圧制御発振器によって生成される。結果として、電圧制御発振器が相対的に低い周波数で動作することによって相対的に小さな電力を使用する一方、周波数逓倍器により生成されたCLKOUT信号は、相対的に高い周波数を持っている。  (もっと読む)

(もっと読む)

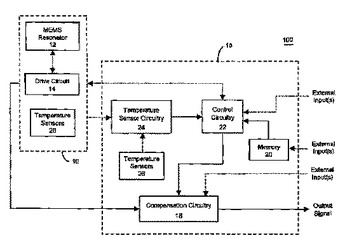

周波数および/または位相補償された微細電気機械発振器

本明細書で説明され、図示される多数の発明がある。1態様で、本発明は、出力信号を生成する微細電気機械共振器と、微細電気機械共振器の出力信号を受け取り、値のセットに応答して第2周波数を有する出力信号を生成するために微細電気機械共振器に結合された周波数調整回路構成と、を有する、補償された微細電気機械共振器を対象とする。1実施形態で、値を、微細電気機械共振器の動作温度および/または微細電気機械共振器の製造変動に依存する、微細電気機械共振器の出力信号の周波数を使用して、決定することができる。1実施形態で、周波数調整回路構成に、周波数逓倍器回路構成(たとえば、PLL、DLL、ディジタル/周波数シンセサイザ、および/またはFLLならびにこれらの任意の組合せおよびその組み合わせの変更)を含めることができる。周波数調整回路構成に、それに加えてまたはその代わりに、周波数分周器回路構成(たとえば、DLL、ディジタル/周波数シンセサイザ(たとえば、DDS)、および/またはFLL、ならびにこれらの任意の組合せおよびその組み合わせの変更)を含めることができる。  (もっと読む)

(もっと読む)

41 - 59 / 59

[ Back to top ]