Fターム[5J106CC54]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | 周波数変換回路 (1,116) | 逓倍回路 (59)

Fターム[5J106CC54]に分類される特許

1 - 20 / 59

原子発振器

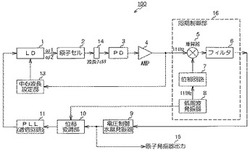

【課題】キャリア光を帯域通過フィルタによって減衰させて、信号検出のS/Nを改善して周波数安定度を高めた原子発振器を提供する。

【解決手段】の原子発振器100は、半導体レーザーにより構成されるLD(光源)1と、LD1に直流電流を与え、LD1の波長を所定の値に設定する中心波長設定部13と、アルカリ金属が封止された原子セル2と、アルカリ金属原子を透過したキャリア光(ωc)と共に第1の共鳴光(ω1)、及び第2の共鳴光(ω2)のうちいずれか一方の光を減衰させる波長フィルタ14と、波長フィルタ14を通過した原子セル2の透過光を検出するPD(光検出器)3と、を備えて構成される。

(もっと読む)

クロック発生装置及びクロック信号生成方法

【課題】CPUに供給するクロック信号の周波数に関わらず、周辺回路に所定の周波数のクロック信号を供給することができるクロック信号生成回路及びクロック信号生成方法を提供する。

【解決手段】本発明にかかるクロック信号生成回路は、CPUに入力される第1クロック信号から、周辺回路に入力される所定の周波数を有する第2クロック信号を生成する。外部から入力される逓倍比及び分周比のうち少なくとも1に基づき、発振子が出力するクロック信号から入力される第1クロック信号を生成する第1クロック生成部と、第1クロック信号から第2クロックを作成するための基準値を算出する基準値算出部と、第1クロック信号のカウント値と基準値との比較結果に基づき、第2クロックを生成する第2クロック生成部とを有し、基準値算出部は、逓倍比及び分周比のうち少なくとも1つが変更され第1のクロック信号の周波数が変更されると、基準値を再度算出する。

(もっと読む)

ルビジウム原子発振器

【課題】回路構成を単純化して部品コストを低減すると共に、回路の小型化を実現したルビジウム原子発振器を提供する。

【解決手段】このルビジウム原子発振器50は、ルビジウム原子の共振周波数により励振する光マイクロ波ユニット(OMU)1と、OMU1を透過した光の強度を検出する光検出部2と、Amp3に現れる周波数誤差信号の位相を検波する位相検波器4と、位相検波器4の出力信号を積分するループフィルタ5と、ループフィルタ5の電圧に基づいて所定の周波数を発振する電圧制御水晶発振器(VCXO)6と、マイクロ波の位相を低周波により変調する発振回路7と、VCXO6の発振信号をマイクロ波に逓倍する位相変調逓倍部8と、を備えて構成されている。

(もっと読む)

原子発振器

【課題】光検出器で吸収される光のレベルを高めてS/Nを改善した原子発振器を提供す

る。

【解決手段】この原子発振器50は大きく分けると、アルカリ金属原子と該アルカリ金属

原子の同位体とを混合した気体を封入したセル2と、可干渉性(コヒーレント性)を有し

、1つの中心周波数に対して2つの異なる周波数成分を有する第1の共鳴光対と第2の共

鳴光対を含む複数の光を気体に照射する光源(LD)1と、気体を透過した光の強度に応

じた検出信号を生成する光検出部(PD)3と、検出信号の強度に基づいて、アルカリ金

属原子に電磁誘起透過現象(以下、EIT現象と呼ぶ)を生起させるように第1の共鳴光

対の周波数を制御すると共に、アルカリ金属原子の同位体にEIT現象を生起させるよう

に、第2の共鳴光対の周波数を制御する周波数制御部12と、を備えて構成されている。

(もっと読む)

クロック位相同期回路

【課題】従属同期網に於けるクロック位相同期回路に関し、誤接続によるクロックループ接続状態の有無を判定する。

【解決手段】基準となる上位局からのリファレンス入力と電圧制御発振器1の出力信号又は分周器4により分周した信号との位相差を位相比較器3により求め、その位相差に対応した制御値を算出し、制御値に従った制御電圧を電圧制御発振器1に入力し、リファレンス入力に位相同期したクロックを出力するクロック位相同期回路であって、位相比較器3により求めた位相比較出力信号を基に、電圧制御発振器1の制御値を求める制御値演算部2と、この制御値演算部2により求めた制御値に所定の変動量を所定時間だけ加算して、制御値の変動経過を監視する監視制御部6とを備え、制御値算出部7により求めた制御値に、所定の変動量を所定時間加算したことによる制御値の変化を基に正常な従属同期網を構成しているか否かを判定する構成を備えている。

(もっと読む)

デジタルPLL

【課題】位相差情報をデジタル値で出力するデジタルPLLにおいて、消費電力を抑えたデジタルPLLを提供することにある。

【解決手段】デジタルPLL100は、発振器10、整数位相算出部20、小数位相算出部30、位相差算出部40、位相差変化量モニタ部50、および発振器制御部60を有する。PLLにおいては発振器の出力周波数が、分周比により設定された所望の周波数に近づく、即ちロック状態に近づくにつれ位相差の変化量は減少していくことから、位相差変化量モニタ部50にて位相差の変化量をモニタし、変化量が整数位相算出部20の1LSB未満である「1」未満になった時点で整数位相算出部20におけるカウンタ動作を停止する。

(もっと読む)

周波数補正回路

【課題】送信波の周波数に同期された周波数又はその逓倍波を容易かつ正確に出力できる周波数補正回路を提供する。

【解決手段】第1電圧制御発振器16の出力信号と基準発振信号との位相差に応じた位相差信号を第1位相比較器10により生成し、第1ループフィルタ12を介して第1位相差信号に応じた第1発振制御信号により第1制御発振器16の発振をフィードバック制御する第1フェーズロックループ回路106と、第2電圧制御発振器36の出力信号と比較対象信号との位相差に応じた位相差信号を第2位相比較器30により生成し、第2ループフィルタ32を介して第2位相差信号に応じた第2発振制御信号により第2制御発振器36の発振をフィードバック制御する第2フェーズロックループ回路114とを備え、第1発振制御信号に応じて第2発振制御信号を変動させることによって比較対象信号に応じて出力信号をロックする。

(もっと読む)

瞬時に同期を確立しかつ保持できる同期発振器

【課題】瞬時に同期を確立し、比較的に長時間、同期状態を高精度で保持することができる同期発振器を安価に実現する。

【解決手段】少なくとも、セットもしくはリセット付きカウンタ22と同期検出手段24とから構成され、前記同期検出手段24において、同期入力信号の立上り点、立下り点、もしくはゼロ交差点のタイミングを検出し、前記タイミングにおいて、前記カウンタ22をセットしあるいはリセットすることで、同期入力信号と瞬時に同期を確立し、前記同期入力信号が休止しあるいは停止した場合、あるいは取去られた後にも、比較的に長時間、同期状態を高精度で保持することができる。

(もっと読む)

スペクトラムアナライザおよびスペクトラム分析方法

【課題】フラクショナルスプリアスに起因するスペクトル波形の表示を阻止しつつ、迅速な測定を可能にする。

【解決手段】指定されたスパン(分析対象周波数範囲)の幅値が境界値より大きい場合、基準信号周波数を所定の基準値に設定し、RBW(分解能帯域幅)より狭いループフィルタ帯域を選択することによってフラクショナルスプリアスをRBWの内側にしてスペクトラム波形として表示されないようにする。また、指定されたスパンの幅値が境界値より小さい場合、基準信号周波数を基準値から所定値シフトさせ、そのシフト量と分周比の整数部との積に等しい分だけVCO出力信号の主信号成分とフラクショナルスプリアスとの周波数差を拡大させ、その拡大した周波数差より狭い範囲でループフィルタの帯域をRBWが含まれる領域に応じて設定してフラクショナルスプリアスのレベルを抑圧する。

(もっと読む)

時刻同期装置およびその時刻同期補正方法

【課題】GPS衛星電波が受信出来ない時も正確に同期タイミング信号を出力する時刻同期装置およびその時刻同期補正方法を提供する。

【解決手段】内蔵発振器1は、GPS受信器Rからの1pps信号と出力するクロックと間の位相差信号を発振制御部3へ出力し、この位相差を無くす発振周波数制御信号が発振制御部3内蔵発振器1へ出力される。1pps信号が断となった場合、発振制御部3は、ログ部LGのドリフト記録部5と信号断時間記録部6から、予め測定記録していた単位時間あたりの内蔵発振器1の周波数のドリフト量からドリフトを補正する発振周波数制御信号を生成して内蔵発振器1へ出力し、タイミング信号発生部2は、内蔵発振器1からのクロックにより生成した同期タイミング信号を外部へ出力する。

(もっと読む)

信号処理装置

【課題】 ジッタの少ないクロックを発生させる

【解決手段】 第1の発振器と、前記第1の発振器から出力される第1のクロックの周波数とは異なる周波数の第2のクロックを出力する第2の発振器と、前記第1の発振器からの第1のクロックと前記第2の発振器からの第2のクロックのうちの一方を選択する選択手段と、前記選択手段により選択された第1のクロックまたは第2のクロックの周波数を逓倍し、出力クロックを生成する生成手段と、前記第1の発振器からの第1のクロックを逓倍する逓倍回路と、前記逓倍回路からの出力信号と前記生成手段からの出力クロックとの位相差を検出し、前記位相差を示す信号を前記第2の発振器に出力することにより前記第2の発振器からの第2のクロックの周波数を変更する位相検出手段とを備える。

(もっと読む)

クロック・データ再生回路及び再生方法並びに局側装置

【課題】バースト信号間の無信号区間に入ったとき、一時的に参照クロック信号と周波数が大きくずれるという現象の発生を防止することができるクロック・データ再生回路及び再生方法並びに当該再生回路を用いた局側装置を提供する。

【解決手段】周波数逓倍部110により、参照クロック信号の周波数をデータ信号相当の周波数に逓倍して逓倍クロック信号とする他、入力選択部111を用いて入力を選択する。すなわち、データ信号としてのバースト信号が入力されているときは、入力されたバースト信号と位相が同期するように再生クロック信号を生成し、バースト信号が入力されていないときは逓倍クロック信号と位相が同期するように再生クロック信号を生成する。

(もっと読む)

クロック生成回路

【課題】位相ロックの精度を向上する。

【解決手段】クロック生成回路は、出力クロックの周期または位相を段階的に遅延する第1の遅延回路および前記第1の遅延回路の遅延時間を設定し制御する第1のカウンタを有する逓倍回路と、前記逓倍回路内の第1の遅延回路から出力された前記出力クロックを入力し、前記出力クロックを所定時間遅延させる第2の遅延回路および前記第2の遅延回路の遅延時間を設定し制御する第2のカウンタを有する位相同期回路を備え、前記逓倍回路は、初期値が第1の値であり第1のカウンタのカウンタ値が一定時間以内で変化しない場合に第2の値が設定される第3のカウンタをさらに有し、前記第3のカウンタのカウンタ値が前記第1の値から前記第2の値に変化した時、前記第2の遅延回路の遅延時間が前記第1の遅延回路の遅延時間と同じかあるいは少し長い遅延時間となるように前記第2のカウンタのカウンタ値を設定する。

(もっと読む)

原子発振器

【課題】周波数基準を実現させると共に、光源駆動制御回路系を簡略化して装置を小型化

し、且つ安価な光源を利用することでコストを低減することができる原子発振器を提供す

る。

【解決手段】この原子発振器50は、アルカリ金属の一種であるCs原子の異なる遷移エ

ネルギーに対応する二種類の周波数の励起光対を発生させる光源1と、少なくとも気体状

のCs原子を封入したCsセル2と、光検出器3と、光検出器3により検出した光強度の

変化に応じてその出力値(電圧等)を制御する周波数制御手段4と、周波数制御手段4の

出力値によりその出力周波数を制御可能な基準発振源5と、基準発振源5の出力周波数を

光源1が発生する二種類の励起光対の周波数差の周波数に逓倍する逓倍手段6と、逓倍手

段6で発生した周波数差の二種類の励起光対を光源1から発生させる光源駆動電流の変調

手段7と、を備えて構成されている。

(もっと読む)

原子発振器

【課題】光源の輝度劣化の影響を回避する。

【解決手段】第1の励起光52を出力する励起光出力部12と、第1の励起光52を分光し第2の励起光152を出力する分光器24と、第1の励起光52により励起される第1のガスセル13を含み第1の周波数信号O1を出力する第1の原子発振部100と、第2の励起光152により励起される第2のガスセル113を含み第2の周波数信号O2を出力する第2の原子発振部200と、第1の周波数信号O1と第2の周波数信号O2とを混合した混合信号301を出力する周波数混合器310と、混合信号301の周波数を変換した出力信号OUTを出力する周波数変換部300と、を含む原子発振器1。

(もっと読む)

原子発振器

【課題】安価な原子発振器を構成する。

【解決手段】原子共鳴器10が発生する共鳴信号54を増幅する増幅器18と、所定の周波数の低周波信号LWVを出力する低周波位相変調信号発生器21と、共鳴信号54と低周波信号LWVとに基づき制御電圧VCを出力する位相弁別器20と、制御電圧VCに基づき原子共鳴器10が正常に動作しているか否かを示すアラーム信号ALMを出力するアラーム回路30と、所定の電圧VDを発生する電圧発生部32と、アラーム信号ALMに基づき原子共鳴器10が正常に動作している場合は制御電圧VCを出力し、正常に動作していない場合は所定の電圧VDを出力するスイッチ回路34と、スイッチ回路34の出力に基づき出力信号OUTの周波数が制御される電圧制御水晶発振器23と、出力信号OUTと低周波信号LWVとに基づき逓倍及び合成したマイクロ波MWVを出力する周波数逓倍合成変調部22と、を含む原子発振器1。

(もっと読む)

原子発振器

【課題】τ秒平均時間の短い期間における短期安定度を向上させた原子発振器を提供する

。

【解決手段】周波数制御部2は、光検出器の出力信号をデジタル信号に変換するA/D変

換器12と、制御電圧を所定の周期又はデューティ比で間欠的に出力するタイミングを生

成するタイマ(制御周期生成手段)13と、タイマ13により生成されたタイミングに基

づいて出力された制御電圧Vcをアナログ電圧に変換するD/A変換器10と、タイマ1

3のタイミングに基づいて、パワーダウンする期間を指示した信号を出力するIO(パワ

ーダウン生成部)14と、全体の動作を制御するCPU11と、を備え、IO14は、少

なくとも周波数合成逓倍部4、又は/及び、原子共鳴部3をパワーダウンするように構成

されている。

(もっと読む)

PLL回路

【課題】感度関数と相補感度関数の両方が低減されたPLL回路を提供する。

【解決手段】本発明のPLL回路10は、一般的なPLL回路の構成を備えた第1ループ50と、相補感度関数を低減するための第2ループ52とを備えて構成されている。第1ループ50では、周波数が高い基準クロック34を用いて比較部14にて位相比較を行うことにより、感度関数を下げている。そして、第2ループ52からの出力により電流補償部16にて電流値を補完することにより、相補感度関数を下げている。

(もっと読む)

広帯域PLL発振回路

【課題】周波数逓倍回路を含む広帯域PLL発振回路において、逓倍回路出力端に高調波等の不要周波数信号を除去するフィルタを必要とせず、簡単な構成によって不要周波数信号に起因して間違った周波数に同期することなく、安定した動作が得られる広帯域PLL発振回路を提供する。

【解決手段】

逓倍回路に同調周波数制御機能を備え、発振周波数に応じて適切な同調周波数になるように制御する。また、PLLロックインまでの時間短縮のためにメモリに記憶した制御電圧情報をVCOに印加する機能を備え、この制御電圧情報によって同時に逓倍回路の同調周波数を制御する。

(もっと読む)

クロック再生装置

【課題】高速で安定したクロックを再生できるクロック再生装置を提供すること。

【解決手段】受信データからデータ受信用の再生クロックを得るクロック再生装置において、前記受信データから不連続を含む再生クロックを生成する再生クロック生成部と、この再生クロック生成部から出力される再生クロックを所定時間逓倍する再生クロック逓倍部とを有し、前記再生クロック生成部から出力された不連続を含む再生クロック信号を前記再生クロック逓倍部で演算し、連続した再生クロックを得ることを特徴とするクロック再生装置。

(もっと読む)

1 - 20 / 59

[ Back to top ]