Fターム[5J106EE18]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−付属構成 (846) | 定電圧回路 (39)

Fターム[5J106EE18]に分類される特許

1 - 20 / 39

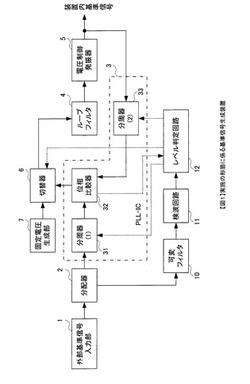

基準信号生成装置

【課題】 回路規模を増大させずに複数の外部基準信号を用いて所望の基準信号を生成でき、アンロック時にも安定した基準信号を出力する基準信号生成装置を提供する。

【解決手段】 分周された外部基準信号と分周された電圧制御発振器5の出力との位相を比較する位相比較器32を備え、複数の異なる周波数の外部基準信号を入力可能とし、可変フィルタ10が入力信号を帯域制限し、検波回路11が可変フィルタ出力の信号レベルを検出し、レベル判定回路12が、可変フィルタ10にいずれかの外部基準信号の周波数を通過させる帯域を設定し、信号レベルが適正範囲であれば、入力された外部基準信号の周波数を当該通過帯域の周波数として特定し、第1の分周器31に当該周波数に応じた分周値を設定すると共に、切替器6を位相比較器31側に切り替え、適正範囲外であれば、切替器6を固定電圧生成装置7側に切り替える基準信号生成装置としている。

(もっと読む)

PLL回路

【課題】PLLのチャージポンプ回路からの出力電流ミスマッチにより、PLLの特性劣化に繋がるリファレンススプリアスが発生する問題がある。

【解決手段】基準信号とフィードバック信号との位相差に応じて第1、第2のパルス信号を出力する位相比較器と、第1の制御信号に応じて、前記第1、第2のパルス信号のパルス幅をそれぞれ調整した第3、第4のパルス信号を生成するパルス幅調整回路と、前記第3、第4のパルス信号に応じて出力電流を生成するチャージポンプと、前記チャージポンプの出力に接続され、電流を電圧に変換するループフィルタと、前記ループフィルタの変換した電圧を積分した検出結果を出力する検出回路と、前記検出結果に応じて、前記第1の制御信号を生成する制御回路と、を有するPLL回路。

(もっと読む)

位相同期回路およびその制御方法

【課題】ばらつき条件(温度、電源電圧、経年変化等)下の安定動作を補償しかつ低ゲインの電圧−周波数特性を実現できる位相同期回路を提供する。

【解決手段】バラクタアレイを有するVCO101と、VCO101の特性をモニターするモニター回路102と、モニター結果に応じてバラクタアレイに供給するオフセット量を切り替えるオフセット発生回路103とを備える。ばらつき条件下のVCOの特性をモニターした結果からバラクタアレイのオフセット量を調整することで、位相同期回路の動作不良を防ぐ。

(もっと読む)

遅延制御回路、チャージポンプ回路、及びチャージポンプ回路における充放電電流制御方法

【課題】トランジスタがアンバランスであってもチャージポンプ回路に最適なバイアス電圧を与えられる遅延制御回路を提供する。

【解決手段】所定の信号を受けて電流入出力端子から充放電を行うチャージポンプ回路と、電流入出力端子の端子電圧に基づく電圧が電源として供給される遅延回路と、チャージポンプ回路の充放電電流の基準となるバイアス電圧を生成するバイアス生成回路と、を備え、チャージポンプ回路及び遅延回路が、それぞれ、第1導電型トランジスタと、第2導電型トランジスタを含んで構成され、バイアス生成回路が、第1導電型トランジスタの相互コンダクタンスと第2導電型トランジスタの相互コンダクタンスの和に基づいて、バイアス電圧を生成する。チャージポンプ回路の充放電により遅延回路の電源電圧を制御し、これにより遅延回路の遅延時間を制御する。

(もっと読む)

半導体集積回路

【課題】複数の無線通信チャンネルについて、PLL回路全体の動作特性に基づいて電圧制御発振器の精密なキャリブレーションを行う。

【解決手段】半導体集積回路は、高周波信号を生成する電圧制御発振器を含むPLL回路と、電圧制御発振器のトランジスタに選択的に負荷される複数のキャパシタと、複数の無線通信チャンネルについて電圧制御発振器の発振周波数を補正するためのキャパシタに関する情報を格納する格納部と、キャリブレーションモードにおいて、複数の無線通信チャンネルについてPLL回路のループ特性を測定することにより補正用キャパシタに関する情報を格納部に格納し、通常動作モードにおいて、選択された無線通信チャンネルに従って、格納部に格納されている情報を読み出すことにより補正用キャパシタを決定するキャリブレーション回路とを具備する。

(もっと読む)

可変インダクタ、電圧制御発振器、複合型PLL回路、フィルタ回路および増幅回路

【課題】制御電圧入力端子の個数を減少させることができる新規な可変インダクタならびにその新規な可変インダクタを備える電圧制御発振器、複合型PLL回路、フィルタ回路および増幅回路を提供する。

【解決手段】本発明の可変インダクタ5においては、複数のインダクタンス素子61、62、63、64におけるそれぞれの接続点とグランド10との間にそれぞれ接続された複数のスイッチダイオード7A、7B、7Cのそれぞれの一端側に対して、複数の定電圧入力端子8A、8B、8Cを介して、互いに異なる定電圧がそれぞれ供給されている。また、本実施形態の可変インダクタ5においては、複数のスイッチダイオード7A、7B、7Cにおけるそれぞれの他端側に対して、1個の制御電圧入力端子9を介して、制御電圧が供給されている。

(もっと読む)

DLL回路

【課題】LPF出力の変化に対するロック周波数の変化量のゲイン設定のばらつきの抑制でジッタ精度をより向上できるDLL回路の提供。

【解決手段】遅延クロックを生成する遅延回路101と、遅延クロックと入力クロックの位相差信号を出力する位相比較回路10と、位相差信号対応の位相差電圧を出力するチャージポンプ回路20と、チャージポンプ回路出力の高周波成分を除去するローパスフィルタ回路30と、ローパスフィルタ回路の出力電圧を電流に変換する第1電圧−電流変換回路40及び基準電圧Vrefを電流に変換する第2電圧−電流変換回路50を含み、第1電圧−電流変換回路の出力電流から第2電圧−電流変換回路の出力電流を減算した結果を変換した電圧とオフセット電流Idを変換した電圧とを含み、位相差電圧が基準電圧より小の場合、オフセット電流を変換した電圧を制御電圧Vcontとして遅延回路に出力する遅延制御回路102と、を備える。

(もっと読む)

発振回路、発振回路を持つ装置、および発振方法

【課題】局部発振周波数を制御する制御電圧を得る際に用いられる電源回路(DC/DCコンバータ)の内部発振周波数に起因する障害を回避する。

【解決手段】電源回路10と電圧制御発振器13と基準発振器15と電圧制御発振器の発振周波数f(VCO)を電圧制御する制御回路16を備える。電源回路10は内部発振器11の発振信号Voから所定電圧Vzを提供する。電圧制御発振器13は可変容量ダイオード14に印加される制御電圧Vcontによって発振周波数が変化する。制御回路16は、基準発振器15の発振周波数f(REF)に基づく比較周波数f(COMP)とf(VCO)に基づく検査周波数f(CHK)との比較結果によりVcontを制御する。Vcontは所定電圧Vzを用いて生成される。ここで、Nを自然数としたときに、内部発振器11の発振周波数f(DD)が比較周波数f(COMP)のN倍より高くN+1倍より低くなるようにする。

(もっと読む)

PLL回路およびその制御方法

【課題】従来のPLL回路は発振周波数を精度良くかつ安定して制御することができないという問題があった。

【解決手段】本発明にかかるPLL回路は、2つのクロック信号の位相差を検出するPFD401と、PFD401の検出結果に基づいて電圧404を出力するLPF403と、電圧404に基づいて出力するVCO出力クロック406の周波数を制御するVCO405と、VCO出力クロック406を分周して出力クロック408を出力する分周器407と、電圧404に基づいて分周器407の分周比を調整する自動調整回路411と、を備える。さらに自動調整回路411は、分周器407を制御する制御信号419と基準電圧を制御する制御信号420とを出力する比較回路434と、基準電圧選択器413と、を備える。このような回路構成により、PLL回路の発振周波数を精度良くかつ安定して制御することができる。

(もっと読む)

電圧制御型発振回路及び電圧変換回路

【課題】複雑な定電流源を使用せずに簡単な回路構成で制御電圧がゲートしきい値電圧以下でも制御電流を流すことができる電圧変換回路及び電圧制御型発振回路を提供すること。

【解決手段】電圧−電圧変換回路101は、制御電圧VINをゲート端子に受けるn型MOSトランジスタN110と、基準電圧VRをゲート端子に受けるn型MOSトランジスタN111と、n型MOSトランジスタN110,N111の共通ドレイン端子をドレイン端子に接続し、ソース端子を高電位電源VDDに接続するp型MOSトランジスタP110と、n型MOSトランジスタN110,N111の共通ソース端子と接地GND間に接続される抵抗体R100とを備える。電圧電流変換回路100は、さらに生成された制御電流に対応する動作電流が流されて電流値に応じた周波数で発振するリングオシレータ201と、基準電圧VRを印加するバイアス電圧発生回路301とを備える。

(もっと読む)

位相比較器、位相同期回路及び位相比較制御方法

【課題】入力断検出部を位相比較器に内蔵することで位相比較器を実装するPLL回路の小型化を図る。

【解決手段】参照信号を入力すると共に、参照信号に基づく被参照信号を帰還入力し、これら入力した参照信号及び被参照信号の立ち上がりエッジを検出し、参照信号の立ち上がりエッジ及び被参照信号の立ち上がりエッジ間の位相差を検出する位相差検出部21と、位相差検出部21にて検出した位相差に基づき、位相差を小さくすべく、定電流出力動作を実行する定電流出力部24と、被参照信号のエッジを検出した後、参照信号のエッジを検出する前に、被参照信号のエッジを再度検出した場合、参照信号の入力断として検出する入力断検出部23とを有している。

(もっと読む)

低域ろ波回路

【課題】容量素子の小型化を図る低域ろ波回路(ループフィルタ)において、容量素子としてMOS容量を使用した場合の電圧依存によるPLL応答特性のばらつきと、MOS容量として薄膜ゲートトランジスタを使用した場合のゲートリーク電流によるジッタ特性の劣化を抑制する。

【解決手段】ループフィルタは、第1の容量素子31と、この容量素子31に直列に接続された抵抗素子32及び第2の容量素子33とを備える。前記第1の容量素子31の一端に接続された第1の入力端IN1に第1の電流(Ip/10)を与え、前記第1の容量素子31の他端に接続された第2の入力端IN2に第2の電流(Ip/10)を与えることにより、第1の容量素子31の小型化が図られる。前記抵抗素子32に直列に接続された可変電圧電源35は、電圧制御端子36から、第1の容量素子31の両端の印加電圧が一定になるように制御される。

(もっと読む)

位相同期回路およびそれを用いた半導体集積回路装置

【課題】プロセスばらつき、環境変動によらず、所望の特性を満足する自動調整できる位相同期回路を提供すること。

【解決手段】位相同期回路は、位相周波数比較器1、チャージポンプ2、ループフィルタ3、分周器6、セレクタ7、電圧制御発振器8を備えている。分周器6は、出力信号と基準信号を入力して出力信号を分周して帰還信号を出力するとともに出力信号から選択信号とトリミング信号とリミット信号を出力する。電圧制御発振器8は、制御電圧と基準電圧とトリミング信号とリミット信号を入力して制御電圧に応じて出力信号周波数を変え、出力信号の上限周波数を制限できるとともに、トリミング信号によって制御電圧に対して出力する出力信号の周波数感度と、リミット信号によって出力信号の上限周波数を変えることができる。

(もっと読む)

位相ロック回路

【課題】位相ロック回路において、電圧制御発振回路や分周回路の性能が設計時よりばらついた場合であっても、電圧制御発振回路が出力する高速クロックを分周回路で良好に分周できるようにして、不良品を低減する。

【解決手段】第1の分周回路4に加えて、この分周回路4よりも動作速度の遅い第2の分周回路5を備える。前記2つの分周回路4、5で分周されたクロックの周波数同士を周波数比較回路6で比較し、第2の分周回路5の分周クロックの周波数よりも第1の分周回路4の分周クロックの周波数の方が速い場合には、VCO発振抑制回路7が電圧制御発振回路3出力クロックFoutの発振周波数を抑制する。

(もっと読む)

クロック信号生成回路、及び半導体装置

【課題】製造プロセスにおけるばらつきが原因による同期期間や同期期間終了後の自走期間において、周波数が変動することがなく、安定した動作を実現し、また安価な半導体装置を提供する。

【解決手段】第1の基準クロック信号を生成する基準クロック信号生成回路と、第1基準クロックの信号及び同期信号を用いて第1の基準クロック信号の立ち上がりのエッジ数を計数する第1のカウンタ回路と、第1のカウンタ回路の計数値を用いて第1の基準クロック信号の立ち上がりのエッジ数を計数する第2のカウンタ回路と、第1のカウンタ回路の計数値を用いて第1の基準クロック信号を分周し、第2の基準クロック信号を生成する第1の分周回路と、第2の基準クロック信号を分周し、クロック信号を生成する第2の分周回路と、を有するクロック生成回路を半導体装置に搭載する。

(もっと読む)

PLL回路

【課題】低ジッターを維持しつつ、発振周波数範囲を拡大できるPLL回路を提供する。

【解決手段】PLL回路は、レギュレータ21と、位相周波数比較器22と、チャージポンプ23と、所定の制御信号を前記レギュレータに出力し、前記レギュレータの出力電圧を制御する電源電圧制御部24と、電源投入または所定のテストモードの際に、前記位相周波数比較器の出力を、前記チャージポンプから前記電源電圧制御部に切り替える第1経路設定部25-1と、第1制御電圧を出力するロウパスフィルタ23と、第2制御電圧を出力する制御電圧発生回路27と、前記第1、第2制御電圧および前記レギュレータの出力電圧に応じて出力クロックを出力する電圧制御発振器28と、前記電源投入または前記所定のテストモードの際に、前記電圧制御発振器の制御端子に入力する制御電圧を、前記第1制御電圧から前記第2制御電圧に切り替える第2経路設定部25-2と、分周器29とを具備する。

(もっと読む)

PLL制御システム

【課題】VCOのバンド毎にチャージポンプ電流を設定しても、ループ帯域のばらつきを抑圧することができるPLL制御システムを提供する。

【解決手段】PLL制御システムにおいて、TCXO8と、分周器B8と、複数のバンドを有するVCO4と、分周器A5と、分周器A5と分周器B8の2つの分周信号を比較する位相比較器6と、VCO4への電圧を出力するループフィルタ2と、位相比較器6の比較信号に応じてループフィルタ2へ電流を供給するチャージポンプ回路3と、ループフィルタ2に対してプリチャージするプリチャージ回路1と、制御部9とを備え、制御部9は、プリチャージ回路1によるプリチャージを、複数のバンドに対応して予め設定された離散的な情報に基づいて離散的に制御する。

(もっと読む)

PLL回路

【課題】電圧制御発振回路が分周回路の設計値を越えた周波数で発振した場合にも、暴走状態を防止して動作安定を実現するPLL回路を提供する。

【解決手段】第1の複数電源電圧発生回路8は、2つの異なる電圧レベルB,Cを電圧選択回路9に出力し、電圧選択回路9は分周回路5の電源線へいずれかの電圧を出力する。電圧レベルBは、電圧制御発振回路4が暴走を始め、分周回路5が動作不可能となった場合に、分周回路5を動作可能状態にするレベルに設定してある。ループフィルタ3の出力が電圧制御発振回路4を暴走状態にして、分周回路5の動作可能範囲を越える場合、電圧比較回路6はHIGH信号を出力し、電圧選択回路9が分周回路の電源電圧を電圧レベルCから電圧レベルBへ切り替え、分周回路5の出力クロックが生成されるようになる。

(もっと読む)

リアルタイムクロック装置および該リアルタイムクロック装置を用いた半導体装置ならびに電子機器

【課題】低消費電流および安定動作を実現することができるリアルタイムクロック装置および該リアルタイムクロック装置を用いた半導体装置ならびに電子機器を提供すること。

【解決手段】水晶発振回路11と、該水晶発振回路11の出力を分周する計時回路(高速部)13と、計時回路(高速部)13の出力を分周する計時回路(低速部)14と、外部との間で信号のやり取りをするインターフェース回路15からなり、水晶発振回路11は第一の電圧VR1で駆動され、計時回路の少なくとも一部分(高速部)13は第二の電圧VR2で駆動され、計時回路の残りの部分およびインターフェース回路15は第三の電圧VDDで駆動され、第一の電圧VR1<第二の電圧VR2<第三の電圧VDDの大小関係を有する。第一の電圧VR1と第二の電圧VR2は第三の電圧VDDから生成される。

(もっと読む)

周波数比較器、周波数合成器及び関連方法

【課題】電圧に基づいて内部周波数を設定し、これを外部周波数と比較するアナログ周波数比較器と、アナログ周波数比較器の同じ原理でクロック信号を合成するアナログ周波数合成器、及び関連の方法を提供する。

【解決手段】周波数比較器は、第一信号と入力電圧に基づいて基準信号を生成する周波数検出回路と、該入力電圧に基づいて第二信号を生成する周波数発生器と、周波数検出回路と周波数発生器に結合され、基準信号と第二信号の一方に基づいて充電電流をイネーブルして電圧レベルを上げ、更に基準信号と第二信号のもう一方に基づいて放電電流をイネーブルして電圧レベルを下げる電荷ポンプ回路と、電荷ポンプ回路に結合され、該電圧レベルに基づいて第一信号と第二信号間の周波数関係を示す決定論理とを含む。

(もっと読む)

1 - 20 / 39

[ Back to top ]