Fターム[5J106EE19]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−付属構成 (846) | 定電流回路 (61)

Fターム[5J106EE19]に分類される特許

1 - 20 / 61

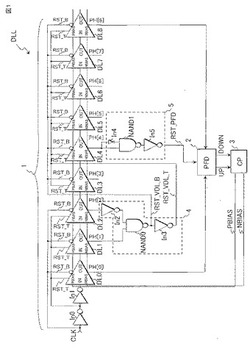

遅延ロックドループを内蔵する半導体集積回路およびその動作方法

【課題】擬似ロックを防止するための論理回路の回路規模を低減する。

【解決手段】遅延ロックドループ(DLL)は、複数の可変遅延回路DL0〜8の電圧制御遅延回路1と位相周波数比較器2とチャージポンプ3を具備する。初段の出力PH[0]と最終段の出力PH[8]は、比較器2に供給される。比較器2のアップ信号とダウン信号は、チャージポンプ3に供給される。擬似ロック防止回路4は、第M段の出力PH[1]と第M+1段の出力PH[2]に応答して、可変遅延リセット信号RST_VDL_T、Bを生成する。初段の回路DL0から第M+1段の回路DL2に、クロック入力信号CLKとクロック反転入力信号がリセット信号RST_B、Tとして供給される。第M+2段の回路DL3から最終段の回路DL8に、可変遅延リセット信号RST_VDL_T、Bがリセット信号RST_B、Tとして供給される。

(もっと読む)

クロック生成回路および電子機器

【課題】クロック生成回路の回路規模を抑制しつつ、クロック信号の周波数スペクトルを好適に拡散する。

【解決手段】クロック生成回路1の電流制御発振部13は、供給される電流に応じた遅延量で信号を遅延する複数の電流制御遅延回路11を含む閉ループ12によりクロック信号を生成する。位相制御部15〜18は、クロック信号と基準信号とを比較する比較器15を有し、これらの信号の位相差を減らすように変化する制御電流を、複数の電流制御遅延回路11に供給する電流として出力する。拡散電流生成部19は、複数の電流制御遅延回路11の一部に対して、制御電流の替わりに、制御電流と異なる電流値のスペクトラム拡散電流を供給する。

(もっと読む)

デジタル制御発振器

【課題】周波数制御により生じるノイズを低減すると共に、制御線を減少させて消費電力および面積を削減することが可能なデジタル制御発振器を提供する。

【解決手段】発振器制御ワードに応じた発振周波数の発振信号を出力するデジタル制御発振器であって、Nビットの前記発振器制御ワードを、上位N−A(但し、A≧1で、N>A)ビットと下位Aビットに分割し、前記上位N−AビットをN−AビットのBynary制御を行う第1のコードOTWbに、前記下位Aビットを2^(A+1)−2ビットのUnary制御を行う第2のコードOTWuに変換して出力する制御手段と、前記制御手段から出力される前記第1および前記第2のコードに応じた発振周波数の発振信号を出力する発振器24と、を備えている。

(もっと読む)

温度特性調整データ生成方法

【課題】n(nは1以上の整数)次の関数で表現される温度特性を持った信号のn−1次の温度係数を調整する際に、n次の温度係数の影響を軽減し、且つコストの増大を抑えることができる、温度特性の調整データを生成する方法を提供する。

【解決手段】温度特性調整データ生成方法は、n(nは1以上の整数)次の関数で表現される温度特性を持った信号を生成する回路を有する半導体装置の温度特性を調整するデータ(803)を、プログラム処理装置(6、10)を用いて生成する方法であって、n+1よりも少ない数の温度における前記信号の値を、前記信号に関する目標値に所定の補正値を加えた値(601)に近づけるように温度特性を調整するデータを生成するデータ生成処理を含む。

(もっと読む)

発振回路

【課題】 起動直後から安定した振動波形を有する出力信号を得ることができる発振回路を提供する。

【解決手段】 発振回路1Aは、入力電圧に基づいて振動波形を有する振動出力電圧を出力する主発振回路2Aと、主発振回路2Aの振動出力電圧に応じた出力信号と予め定められた周波数を有するクロック同期信号SYNCとが入力され、出力信号及びクロック同期信号SYNCの位相差に応じた電圧を出力する位相比較器3と、位相比較器3の出力電圧を平滑化する第1ローパスフィルタ4と、第1ローパスフィルタ4の出力電圧が基準電圧Vref1以上の場合、第1ローパスフィルタ4の出力電圧を主発振回路2Aに入力し、第1ローパスフィルタ4の出力電圧が基準電圧Vref1より低い場合、基準電圧Vref1を主発振回路2Aに入力する切替回路5Aとを備えている。

(もっと読む)

チャージポンプ回路、PLL回路及び電子回路装置

【課題】寄生容量(浮遊容量)の影響を抑制し、制御信号の電圧変動を抑えることで、リファレンスリークや妨害スプリアスを少なくすることが可能なチャージポンプ回路を提供する。

【解決手段】本実施形態のチャージポンプ回路は、セレクタ手段SEL1は、主定電流源I1_mainと主定電流源I2_mainまたは副電流源I2_subとを接続させ、かつ、主定電流源I2_mainと主定電流源I1_mainまたは副電流源I1_subとを接続させるよう接続状態を選択し、主定電流源I1_main及びI2_mainを常時他の電流源と接続させる。

(もっと読む)

PLL回路および電子機器

【課題】PLL回路の回路規模の増大を抑制しながら、安定性と周波数引込み速さとを独立に設定可能にする。

【解決手段】PLL回路1は、信号を遅延する遅延閉ループ19により発振信号を生成するリング発振部2と、位相比較部3、チャージポンプ4、平滑フィルタ5、平滑電流源6、遅れ成分フィルタ7、および補正電流源8を有する。遅れ成分フィルタ7は、平滑フィルタ5と並列にチャージポンプ4の出力に接続され、チャージポンプ4の出力信号に含まれる応答遅れ成分を抽出する。リング発振部2は、遅延閉ループ19において信号を遅延する遅延部として、平滑電流源6および補正電流源8の少なくとも一方の電流源から供給される電流により動作して信号を遅延する遅延部11を有する。

(もっと読む)

抵抗値調整回路

【課題】LSI内部の抵抗素子の抵抗値を精度よく且つ適時に較正する。

【解決手段】

複数の抵抗素子を有する半導体集積回路に設けられる抵抗値調整回路は、前記複数の抵抗素子のうち第1の抵抗素子に基準電圧を印加して第1の抵抗素子の抵抗値に反比例する定電流を生成し、前記半導体集積回路の外部のコンデンサに前記定電流を供給する定電流源と、前記コンデンサに前記定電流が供給されるときに、前記コンデンサの電圧が所定電圧上昇する時間を計測する充電時間計測部と、予め設定された基準充電時間と前記計測された計測充電時間の差分に基づいて前記複数の抵抗素子のうち第2の抵抗素子の抵抗値を較正するキャリブレーション部を有する。LSI外部のコンデンサは容量が既知であり、LSIの製造プロセスのばらつきに依存しないので、基準充電時間と計測充電時間の差分に基づいて、精度よく抵抗値を較正できる。

(もっと読む)

デジタル遅延線の時間遅延のプロセス、電圧、および温度のばらつき補正を行う装置と方法

【課題】プロセス、電圧、温度、補償回路、および連続的に遅延量を発生させる方法を提供する。

【解決手段】補償回路は2つの遅延線を含んでおり、各遅延線が遅延出力を供給する。2つの遅延線は、それぞれが多数の遅延エレメントを含み、その結果として1つ以上の電流枯渇型インバータを含む場合がある。遅延線の数は、2つの遅延線間で異なる場合がある。遅延出力は、2つの遅延出力に基づくオフセットパルスを決定した後、オフセットパルスの電圧を平均し、遅延量を決定する合成回路に供給される。遅延量は、1つ以上の電流または電圧となる場合があり、メモリバスドライバ、動的ランダムアクセスメモリ、同期DRAM、プロセッサ、あるいは他のクロック回路のようなアプリケーション回路の入力信号または出力信号に適用されるPVT補正量を示す。

(もっと読む)

位相同期ループ回路

【課題】出力周波数レンジの広いPLL回路を提供すること。

【解決手段】本発明の一態様は、入力パルス信号と出力側からフィードバックされたフィードバックパルス信号との位相差に基づいて生成された電圧を、制御電流Icへ変換する電圧電流変換回路104と、制御電流Icに応じた周波数のパルス信号を生成する電流制御発振器105と、制御電流Icを検出する電流検出部108と、検出された前記制御電流に基づいて、電流制御発振器105から発振される出力パルス信号の周波数レンジを切り替える周波数レンジ切替回路106と、を備えた位相同期ループ回路である。

(もっと読む)

電圧制御型発振回路及び電圧変換回路

【課題】複雑な定電流源を使用せずに簡単な回路構成で制御電圧がゲートしきい値電圧以下でも制御電流を流すことができる電圧変換回路及び電圧制御型発振回路を提供すること。

【解決手段】電圧−電圧変換回路101は、制御電圧VINをゲート端子に受けるn型MOSトランジスタN110と、基準電圧VRをゲート端子に受けるn型MOSトランジスタN111と、n型MOSトランジスタN110,N111の共通ドレイン端子をドレイン端子に接続し、ソース端子を高電位電源VDDに接続するp型MOSトランジスタP110と、n型MOSトランジスタN110,N111の共通ソース端子と接地GND間に接続される抵抗体R100とを備える。電圧電流変換回路100は、さらに生成された制御電流に対応する動作電流が流されて電流値に応じた周波数で発振するリングオシレータ201と、基準電圧VRを印加するバイアス電圧発生回路301とを備える。

(もっと読む)

チャージポンプ回路およびPLL回路

【課題】 広い範囲にわたって良好な特性のチャージポンプ電流の得られるチャージポンプ回路を提供する。

【解決手段】 第1のチャージポンプ部14Aに、定電流源Q1から出力される定電流を、スイッチ回路SW1、SW2の直列回路と、スイッチ回路SW3、SW4の直列回路とに振り分ける制御信号が供給する。残るチャージポンプ部14B、14Cには、定電流源Q1から出力される定電流を、スイッチ回路SW1、SW2の直列回路と、スイッチ回路SW3、SW4の直列回路とに振り分ける制御信号と、スイッチ回路SW1〜SW4をオフにする電位とが、スイッチ回路SWA〜SWDを通じて供給される。必要とするチャージポンプ電流に大きさに対応して、スイッチ回路SW11BA〜SW14Cを制御するとともに、定電流源Q1、Q2の出力電流の大きさを変更することにより、出力端子T3に、必要とする大きさのチャージポンプ電流を得る。

(もっと読む)

チャージポンプ回路およびPLL回路

【課題】消費電流を低減しつつ、出力のオーバーシュートを抑制することが可能なチャージポンプ回路を提供する。

【解決手段】チャージポンプ回路は、入出力端子を充電する場合は、第1のスイッチ素子、第4のスイッチ素子、および第5のスイッチ素子をオンするとともに、第2のスイッチ素子、第3のスイッチ素子、および第6のスイッチ素子をオフし、入出力端子を放電する場合は、第1のスイッチ素子、第4のスイッチ素子、および第5のスイッチ素子をオフするとともに、第2のスイッチ素子、第3のスイッチ素子、および第6のスイッチ素子をオンし、入出力端子を充放電しない場合は、第1のスイッチ素子、第2のスイッチ素子、第5のスイッチ素子、および第6のスイッチ素子をオフするとともに、第3のスイッチ素子、および第4のスイッチ素子をオンする。

(もっと読む)

低域ろ波回路

【課題】容量素子の小型化を図る低域ろ波回路(ループフィルタ)において、容量素子としてMOS容量を使用した場合の電圧依存によるPLL応答特性のばらつきと、MOS容量として薄膜ゲートトランジスタを使用した場合のゲートリーク電流によるジッタ特性の劣化を抑制する。

【解決手段】ループフィルタは、第1の容量素子31と、この容量素子31に直列に接続された抵抗素子32及び第2の容量素子33とを備える。前記第1の容量素子31の一端に接続された第1の入力端IN1に第1の電流(Ip/10)を与え、前記第1の容量素子31の他端に接続された第2の入力端IN2に第2の電流(Ip/10)を与えることにより、第1の容量素子31の小型化が図られる。前記抵抗素子32に直列に接続された可変電圧電源35は、電圧制御端子36から、第1の容量素子31の両端の印加電圧が一定になるように制御される。

(もっと読む)

PONシステムの局側装置、受信方法及びクロックデータ再生回路

【課題】 周波数変化を伴う入力信号に対しても高速かつ高精度に追従することができるクロックデータ再生回路を提供する。

【解決手段】 本発明のクロックデータ再生回路は、制御電圧Vcに対応する発振周波数でクロック信号Scを出力する電圧制御型発振器55と、入力信号(受信データ)RDとクロック信号Scとの位相差に対応してアップ信号Su又はダウン信号Sdを出力する位相比較器52と、アップ信号Su又はダウン信号Sdに対応するチャージポンプ電流Ipを生成するチャージポンプ53と、チャージポンプ電流Ipに対応する制御電圧Vcを生成するループフィルタ54と、位相差に基づいてチャージポンプ53又はループフィルタ54若しくはこれらの双方の動作パラメータを切り替える制御部58とを備えている。

(もっと読む)

PLL回路

【課題】安定かつ最適な位相雑音レベルで動作するPLL回路を提供する。

【解決手段】上記課題を解決するために、PLL回路100は、2つの入力信号の位相差に応じた電圧を出力する位相比較器101と、電流変換利得を調整して入力信号を任意の昇圧率で上昇させる可変チャージポンプ102と、所定の周波数特性を有するループフィルタ103と、VCO104と、ループフィルタ103の出力信号をデジタル値に変換するA/Dコンバータ105と、VCO104を選択するともにA/Dコンバータ105の出力値に応じて可変チャージポンプ102を制御するVCO選択回路106と、VCO104からの出力信号を1/N倍に分周する分周回路107と、を備える。

(もっと読む)

局所発振回路

【課題】消費電力を低減できる局所発振回路を提供する。

【解決手段】周波数fsの基準振動信号と周波数fout/(m×n)の分周信号の位相を比較する位相比較器1と、上記両信号の位相のずれに応じた電流IOUTを出力する電荷ポンプ10と、上記出力電流IOUTに応じた制御電圧VCを生成するループフィルタ3と、上記制御電圧VCに応じた発振周波数foutの信号を出力する電圧制御発振器4と、電圧制御発振器4の出力信号を設定周波数に応じた分周値(m×n)で分周して上記分周信号を出力する前置分周器5および可変カウンタ6とを備え、上記発振周波数foutを上記設定周波数に引き込む局所発振回路において、上記電荷ポンプ10は、出力電流IOUTの値を上記設定周波数に応じて切り換える。

(もっと読む)

クロック発生回路

【課題】高精度な周波数変調が可能なスペクトラム拡散クロック発生回路を提供する。

【解決手段】このスペクトラム拡散クロック発生回路において、PLL回路31は、それぞれ位相の異なるクロック信号CLKV1〜CLKV5を出力する。セレクタ23は、クロック信号CLKV1〜CLKV5のうちのいずれか1つを選択し、制御回路24はセレクタ9の信号選択動作を制御する。入力分周回路1は選択クロック信号を分周して基準クロック信号CLKRを出力する。PLL回路21は、基準クロック信号CLKRを周波数逓倍した発振クロック信号CLKOを生成する。これにより、発振クロック信号CLKOの位相を微調整することができる。したがって、高精度な周波数変調が可能なスペクトラム拡散クロック発生回路が実現できる。

(もっと読む)

発振器及びそれを用いた位相同期ループ回路

【課題】制御信号だけではなく、周波数も制御可能な変調機能を有する発振器、及びその発振器を用いた位相同期ループ回路を提供する。

【解決手段】出力信号の帰還信号と基準信号との位相を比較して、位相差を示す信号を出力する位相検出器1081と、位相検出器1081の出力信号が供給され、位相差をなくすための制御信号を出力するループフィルタ1082と、ループフィルタ1082からの制御信号に基づく周波数で発振する発振器1083とを備え、発振器1083は、制御信号に変調信号を加えることによって周波数を変調する変調手段を備える位相同期ループ回路(PLL回路)。

(もっと読む)

DLL回路及びこれを用いた半導体記憶装置、並びに、データ処理システム

【課題】FDLを調整するカウント信号のビット数を増加させても、高速に遅延量を確定させることが可能なDLL回路を提供する。

【解決手段】相対的に粗い調整ピッチでクロック信号を遅延させるディレイライン(CDL)10と、相対的に細かい調整ピッチでクロック信号を遅延させるディレイライン(FDL)20と、ディレイライン10,20の遅延量を制御する位相検知回路41,42及びカウンタ制御回路51,52とを備える。カウンタ制御回路51,52は、線形探索法によってディレイライン10を制御するとともに、二分探索法によってディレイライン20を制御する。これにより、ディレイライン20を調整するカウント信号のビット数を増加させても、高速に遅延量を確定させることが可能となる。

(もっと読む)

1 - 20 / 61

[ Back to top ]