Fターム[5J106FF08]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 入出力、ループ構成 (832) | 帰還回路 (189)

Fターム[5J106FF08]に分類される特許

1 - 20 / 189

自励発振型D級アンプおよび自励発振型D級アンプの自励発振周波数制御方法

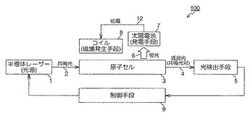

原子発振器

【課題】専用の電源を不要として、小型化と省エネを実現した原子発振器を提供する。

【解決手段】本実施形態に係る原子発振器100は、アルカリ金属原子(Na、Rb、Cs)が封入された原子セル3と、アルカリ金属原子に電磁誘起透過現象を発現させるための共鳴光2を照射する半導体レーザー(光源)1と、原子セル3を透過した透過光(共鳴光対)4を検出する光検出手段5と、アルカリ金属原子が発する蛍光6の強度に応じた電力を発電する太陽電池(発電手段)7と、太陽電池7から供給された電力によってアルカリ金属原子に与える磁場を発生するコイル(磁場発生手段)8と、光検出手段5で検知した信号を同期制御する制御手段9と、を備えて構成されている。

(もっと読む)

半導体装置

【課題】半導体装置の入出力クロックスキューを抑制する。

【解決手段】I/O電圧電源で駆動される第1のバッファ1及び第2のバッファ8と、I/O電圧電源の電圧レベルを示す電圧判定信号を生成する電圧判定部5と、第1のバッファ1を介して入力された入力クロック信号に基づいて出力クロック信号の位相を調整して第2のバッファへ出力するエコークロック生成部7と、電圧判定信号と位相の調整量との関係を選択するモード情報を記憶する記憶部6と、を有し、エコークロック生成部7は、電圧判定信号とモード情報とに基づいて出力クロック信号の位相の調整量を決定する。

(もっと読む)

PLL回路

【課題】出力クロック信号の周波数制御を精度良く行うことが容易となるPLL回路を提供する。

【解決手段】流出または流入の出力電流を出力するものであって、パルス信号に応じて前記出力電流のオン/オフが切替えられるチャージポンプと、周期性を有する多値の参照信号に応じて前記パルス信号を生成する、パルス信号生成部と、を備え、前記出力電流に応じた出力クロック信号を生成するPLL回路であって、前記参照信号に応じて前記出力電流の電流量を調節する、電流量調節部を備えたPLL回路とする。

(もっと読む)

周波数シンセサイザ

【課題】 外部基準信号の入力断で高速にスイッチを切り替えて一定の電圧を発振器の制御電圧として出力でき、出力周波数の変動量を最小限に抑えることができる周波数シンセサイザを提供する。

【解決手段】 制御回路11が、検波回路10からの検波出力を入力し、外部基準入力信号「入」の場合には、SW3にPLL−IC1の出力をループフィルタ4に出力させる切替信号を出力し、外部基準入力信号「断」の場合には、SW3に可変抵抗2の出力をループフィルタ4に出力させる切替信号を出力し、スイッチ高速切替回路12が、外部基準入力信号の「断」を検出して制御回路11より高速にSW3に可変抵抗2の出力をループフィルタ4に出力させる切替信号を出力する周波数シンセサイザである。

(もっと読む)

遅延回路、DLL回路、および半導体装置

【課題】 段数切替型の遅延回路において、段数切替時に発生するハザードを抑制する。

【解決手段】 本発明の段数切替型の遅延回路は、段数切替前後で遅延回路の内部ノードの論理状態が変化しないように、遅延のための経路として選択されていない段に遅延回路の入力が接続されている。これにより、遅延回路のハザードの発生を抑制することができ、ひいては遅延回路を備えるDLL回路や半導体装置の論理規模を低減でき、低消費電力化に寄与し、また、半導体装置の処理速度を向上させることができる。

(もっと読む)

PLL回路及びその制御方法

【課題】回路規模の増大を抑制しつつ、VCOの発振周波数を広い範囲で変化させることができるPLL回路及びその制御方法を提供すること。

【解決手段】本発明にかかるPLL回路1は、VCO11と、制御ロジック14と、位相比較器13と、を備える。VCO11は、両端の電位差に応じて容量値が変化する可変容量素子を有し、電位差に応じた発振周波数の出力信号を出力する。制御ロジック14は、可変容量素子の一端に所定の電圧を印加した状態で、基準信号と出力信号との周波数差に基づいて、当該可変容量素子の他端に印加する制御電圧Vtcを決定する。位相比較器13は、可変容量素子の他端の電圧を制御ロジック14により決定された制御電圧Vtcに固定した状態で、基準信号と出力信号との位相差に基づいて、可変容量素子の一端に印加する制御電圧Vtaを決定する。

(もっと読む)

半導体装置及びその制御方法

【課題】クロック信号にジッタ成分が重畳している場合であってもDLL回路を正しくロックさせる。

【解決手段】カウンタ部102のカウント値に応じてクロック信号LCLKを生成するディレイライン101と、クロック信号LCLKを反転させるか否かを制御する反転制御部103とを備える。カウンタ部102のカウント値を第1の初期値にリセットした後、反転制御部103はクロック信号LCLKを反転させ又は反転させることなく出力する。次に、カウンタ部102のカウント値を第2の初期値にリセットする。本発明によれば、ジッタなどの影響によってクロック信号LCLKを誤って反転させ、或いは誤って反転させなかった場合であっても、ダウンカウント(またはアップカウント)が多数回連続することがなくなる。これにより、第1及び第2の初期値としてオフセットした値を用いることが可能となる。

(もっと読む)

PLL回路

【課題】PLLのチャージポンプ回路からの出力電流ミスマッチにより、PLLの特性劣化に繋がるリファレンススプリアスが発生する問題がある。

【解決手段】基準信号とフィードバック信号との位相差に応じて第1、第2のパルス信号を出力する位相比較器と、第1の制御信号に応じて、前記第1、第2のパルス信号のパルス幅をそれぞれ調整した第3、第4のパルス信号を生成するパルス幅調整回路と、前記第3、第4のパルス信号に応じて出力電流を生成するチャージポンプと、前記チャージポンプの出力に接続され、電流を電圧に変換するループフィルタと、前記ループフィルタの変換した電圧を積分した検出結果を出力する検出回路と、前記検出結果に応じて、前記第1の制御信号を生成する制御回路と、を有するPLL回路。

(もっと読む)

時間差加算器を含むシステムオンチップ、時間差累算器を含むシステムオンチップ、シグマ−デルタタイムデジタル変換器、デジタル位相ロックループ、温度センサ、及びシステムオンチップ

【課題】 入力信号間の時間差を加算する時間差加算器を含むシステムオンチップを提供する。

【解決手段】 時間差加算器100は、第1入力信号SIN1、第2入力信号SIN2、第3入力信号SIN3、及び第4入力信号SIN4に応答して第1出力信号SOUT1及び第2出力信号SOUT2を生成する。時間差加算器100は、第1入力信号SIN1と第2入力信号SIN2との間の第1時間差TD1、及び、第3入力信号SIN3と第4入力信号SIN4との間の第2時間差TD2を加算することによって、第1時間差TD1と第2時間差TD2との和に相応する時間差(TD1+TD2)を有する第1出力信号SOUT1及び第2出力信号SOUT2を出力する。これにより、低い電源電圧環境において、時間ドメインで信号処理を遂行することができ、性能を向上させることができる。

(もっと読む)

半導体装置

【課題】DLL回路の調整を素早く完了する。

【解決手段】第1のクロック信号(図2のCLKIN)を遅延させて第2のクロック信号(図2のLCLK)を生成する遅延部(図2の33、34が相当する)と、第1のクロック信号と、第2のクロック信号をさらに遅延した信号(図2のRCLK)との位相を比較する位相比較回路(図2の36)と、遅延部の遅延量を決定するカウント値を遅延部に出力すると共に、位相比較回路の位相比較結果に応じてアップダウンするカウンタ回路(図2の37)と、初期設定動作時において、第1のクロック信号の周期を検知し、検知した周期に応じたカウント値の初期値をカウンタ回路に対して出力する初期遅延量制御回路(図2の30)と、を備える。

(もっと読む)

クロック発生装置及びクロック信号生成方法

【課題】CPUに供給するクロック信号の周波数に関わらず、周辺回路に所定の周波数のクロック信号を供給することができるクロック信号生成回路及びクロック信号生成方法を提供する。

【解決手段】本発明にかかるクロック信号生成回路は、CPUに入力される第1クロック信号から、周辺回路に入力される所定の周波数を有する第2クロック信号を生成する。外部から入力される逓倍比及び分周比のうち少なくとも1に基づき、発振子が出力するクロック信号から入力される第1クロック信号を生成する第1クロック生成部と、第1クロック信号から第2クロックを作成するための基準値を算出する基準値算出部と、第1クロック信号のカウント値と基準値との比較結果に基づき、第2クロックを生成する第2クロック生成部とを有し、基準値算出部は、逓倍比及び分周比のうち少なくとも1つが変更され第1のクロック信号の周波数が変更されると、基準値を再度算出する。

(もっと読む)

原子発振器用の光学モジュールおよび原子発振器

【課題】周波数安定度の高い原子発振器を得ることが可能な原子発振器用の光学モジュールを提供する。

【解決手段】光学モジュール2は、量子干渉効果を利用する原子発振器用の光学モジュールであって、所定の波長を有する基本波F、当該基本波Fの側帯波W1,W2、を含む光L1を出射する光源10と、光源10からの光L1が入射し、当該入射した光L1のうち側帯波W1,W2を透過させる波長選択部20と、アルカリ金属ガスを封入し、波長選択部20を透過した光が照射されるガスセル30と、ガスセル30に照射された光のうちガスセル30を透過した光の強度を検出する光検出部40と、を含み、

波長選択部20は、ファイバーブラッググレーティング20aと、ファイバーブラッググレーティングの温度を制御する温度制御部20bと、を有する。

(もっと読む)

原子発振器用の光学モジュールおよび原子発振器

【課題】周波数安定度の高い原子発振器を得ることが可能な原子発振器用の光学モジュールを提供する。

【解決手段】光学モジュール2は、量子干渉効果を利用する原子発振器用の光学モジュール2であって、所定の波長を有する基本波F、当該基本波の側帯波W1,W2、を含む光L1を出射する光源10と、光源10からの光が入射し、当該入射した光のうち側帯波W1,W2を透過させる波長選択部20と、アルカリ金属ガスを封入し、波長選択部20を透過した光L2が照射されるガスセル30と、ガスセル30に照射された光のうちガスセル30を透過した光の強度を検出する光検出部40と、を含み、波長選択部20は、所定の波長範囲の光を透過させる光フィルター部20aと、光フィルター部20aが透過させる光の波長範囲を変化させる光フィルター特性制御部20bと、を有する。

(もっと読む)

原子発振器用の光学モジュールおよび原子発振器

【課題】周波数安定度の高い原子発振器を得ることが可能な原子発振器用の光学モジュールを提供する。

【解決手段】光学モジュール2は、量子干渉効果を利用する原子発振器用の光学モジュールであって、所定の波長を有する基本波F、当該基本波Fの側帯波W1,W2、を含む光L1を出射する光源10と、光源10からの光L1が入射し、当該入射した光L1のうち側帯波W1,W2を透過させる波長選択部20と、アルカリ金属ガスを封入し、波長選択部20を透過した光が照射されるガスセル30と、ガスセル30に照射された光のうちガスセル30を透過した光の強度を検出する光検出部40と、を含み、波長選択部20は、ファイバーブラッググレーティング20aと、ファイバーブラッググレーティング20aに電圧を印加する電圧印加部20bと、を有する。

(もっと読む)

PLL回路

【課題】Trackingバンクの最小1bit以下の周波数分解能を実現でき、かつC/N特性の劣化を防止できるPLL回路を提供することを目的とする。

【解決手段】PLL回路101は、デジタル信号の値で周波数を離散的に調整し、微小周波数を1のアナログ信号の電圧値で調整し、所望の周波数の出力信号を出力する発振器10と、基準信号と発振器10の出力信号との位相差及び周波数差を表すデジタル値を出力する比較器11と、比較器11の出力するデジタル値を複数のデジタル信号として出力するループフィルタ44と、ループフィルタ44が出力する前記デジタル信号のうち発振器10で微小周波数の調整に対応する1のデジタル信号が直接入力され、入力されたデジタル信号をアナログ信号に変換するデジタルアナログ変換器13と、デジタルアナログ変換器13からのアナログ信号の高周波成分を除去するローパスフィルタ14と、を備える。

(もっと読む)

クロック周波数制御回路及びクロック周波数制御方法

【課題】 信号の分周比を比較的少なくし、また位相雑音の増加も抑圧した上で微少な周波数変化した信号を生成するPLL回路を実現する。

【解決手段】 本発明は、所定の電圧を加減することにより出力周波数を制御する相関回路入力される電圧に応じて出力周波数が変化する電圧制御発振器と、電圧制御発振器の出力を分周する第1の分周回路と、外部から入力される基準周波数を分周する第2の分周回路と、第1の分周回路と前記第2の分周回路との出力の位相に応じたパルスを出力する位相比較器と、位相比較器の出力から低周波成分を抽出し、電圧制御発生器に入力するローパスフィルタとを有する。

(もっと読む)

シリアルデータの受信回路、受信方法およびそれらを用いたシリアルデータの伝送システム、伝送方法

【課題】単一の伝送路で、高速なシリアルデータを伝送可能な伝送技術を提供する。

【解決手段】受信回路100は、pビットに2×q回(p、qは実数)の割合で第1レベルから第2レベルへの遷移が生ずるように生成されたシリアルデータDSOUTを受ける。VCO60は、入力された制御電圧Vcnt2に応じた周波数を有するサンプリングクロック信号CLK4を発生する。第1分周器22は、サンプリングクロック信号CLK4を分周比Mで分周する。第2分周器24は、受信したシリアルデータに応じたクロック信号CLKINを分周比Nで分周する。周波数比較器20は、第1分周器22の出力信号と第2分周器24の出力信号の位相差に応じた位相周波数差信号PFDを発生する。制御電圧生成回路42は、位相周波数差信号PFDに応じて、チャージポンプ回路40の周波数を調節するための制御電圧Vcnt2を生成する。

(もっと読む)

周波数シンセサイザおよび時間デジタル変換器

【課題】周波数シンセサイザにおいて、ループ帯域内位相ノイズの低減を小面積かつ低電流の構成で実現する。

【解決手段】周波数シンセサイザは、発振器1と、発振器1出力の分周信号CKVと参照信号Frefとの正規化された位相差を検出するTDC回路7とを備え、TDC回路7によって検出された正規化された位相差に基づいて発振器1の周波数を制御する。TDC回路7は、第2の発振器711と、第2の発振器711の出力信号OSC2の周期数をカウントするカウンタ712とを備え、カウンタ712の出力から、分周信号CKVの周期に相当するカウンタ値と、分周信号CKVと参照信号Frefとの位相差に相当するカウンタ値とを得て、これらのカウンタ値に基づいて、正規化された位相差を算出する。

(もっと読む)

半導体装置

【課題】レプリカ回路の精度を抜本的に向上する。

【解決手段】半導体装置10は、少なくともフィードバッククロック信号RCLK1に基づいて外部クロック信号CK,/CKを遅延させてなる内部クロック信号RLCLKを出力するDLL回路70と、内部クロック信号RLCLKに同期してデータを出力する複数の出力バッファ64aと、出力バッファ64aのレプリカであり、内部クロック信号RLCLKに同期してフィードバッククロック信号RCLK1を生成し、DLL回路70に供給する出力レプリカ73と、DLL回路70から内部クロック信号RLCLKを受け、複数の出力バッファ64a及び出力レプリカ73に伝送するクロックツリー72とを備え、クロックツリー72は、それぞれDLL回路70から複数の出力バッファ64a及び出力レプリカ73に至る内部クロック信号RLCLKの複数の伝送経路の信号線負荷が互いに実質的に等しくなるよう構成される。

(もっと読む)

1 - 20 / 189

[ Back to top ]