Fターム[5J106GG01]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 制御対象 (2,074) | 発振回路、VCO (652)

Fターム[5J106GG01]の下位に属するFターム

原子発振器 (61)

基準・局部・予備発振回路 (39)

Fターム[5J106GG01]に分類される特許

541 - 552 / 552

可調周波数変換器

回路基板にマウントされた電気回路を有する可調周波数変換器が開示される。上記回路は、共振器を備える位相同期ループ(PLL)を提供するにように設計されている。柔軟な材料が回路基板と共振器の間に配置される。電導性リードにより短絡させられる少なくとも1つの受動素子が共振器に作動的に接続される。周波数変換器の共振周波数は、電導性リードを切断し、関連付けられた受動素子を活性化させることにより変更することができる。 (もっと読む)

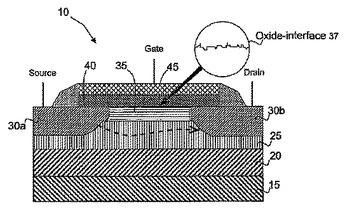

ストレインド・シリコン電圧制御発振器(VCO)

ストレインド・シリコン電圧制御発振器(VCO)は、ストレインド・シリコン層を有する第1Pチャネル金属酸化膜半導体(PMOS)装置を含み、ストレインド・シリコン層を有する第2PMOS装置に結合される。  (もっと読む)

(もっと読む)

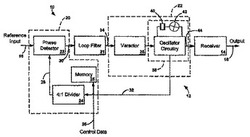

フェーズロックループ帯域幅校正回路及びその方法

フェーズロックループ周波数シンセサイザが、チャージポンプ(332)、フェーズロックループフィルタ(310)、電圧制御発振器(314)、及び帯域幅校正回路(304、450、460)を有する。帯域幅校正回路は、電圧制御発振器(314)のゲインを測定し、測定された電圧制御発振器のゲインを使用してチャージポンプ電流レベルを調節する。チャージポンプ電流レベルは、測定された電圧制御発振器のゲインとチャージポンプ電流レベルとの積が一定のフェーズロックループ帯域幅をもたらすように調節される。本発明はまた、プログラマブルチャージポンプに接続されたフェーズロックループフィルタの抵抗値にマッチした抵抗値を有するプログラマブルチャージポンプを有するフェーズロックループも開示している。フェーズロックループ帯域幅を電圧制御発振器のゲインの測定に基づいて校正する方法、及び受信されたRF信号を処理するシステムもまた、開示される。  (もっと読む)

(もっと読む)

セル配列を用いた可変インピーダンス回路

電圧制御回路(100)において、電圧制御発振器(110)(VCO)の周波数を制御する可変コンデンサを駆動するために、回路要素の配列(500)が用いられる。配列(500)は、複数のセル(600)、少なくとも1つの出力、複数の粗設定入力(383-388)及び複数の精細設定入力(380-382)を有する。両方の種類の入力は、前記セルの選択可能な組合せを有効にするようにされる。VCO(110)は、複数の周波数帯域にわたる範囲の複数のビットアドレス処理可能な参照周波数で動作する。アドレス制御回路(130)は、前記粗設定入力(383-388)を制御することによって、前記複数の周波数帯域のうちの1つを確定するとともに、また前記精細設定入力を制御することによって、前記周波数帯域のうちの1つを確定する。1つの実施例において、前記アドレス制御回路は、VCO回路(100)のための周波数帯域を設定するのに用いられ、アナログ信号は、前記帯域内の所望な周波数に同調するのに用いられる。  (もっと読む)

(もっと読む)

発振器の操向するための方法、及び発振器

本発明の目的は、周波数発振器を作ること、すなわち、外部外乱にも関わらず信頼性高く機能し、かつそれ専用の周波数を維持するために容易な制御を有するであろう水晶発振器をより正確に作ることである。この目的は、周波数発振器として、その出力周波数よりずっと低い範囲を持つ水晶発振器、或いは相当する機械共振器を選択することにより達され、その周波数は典型的には100kHz以下である。このような発振器は、サイズが小さく、製造するのが容易であり、それはまた、外部外乱にも関わらず、それ専用の周波数を非常によく維持する能力を持つ。その小さいサイズのおかげで、その発振器の消費電力は小さく、これは、例えばブルートゥース応用例において重要である。  (もっと読む)

(もっと読む)

周波数選択性を有し低位相ノイズかつ低熱ドリフトの発振器

電圧制御発振器(200)は、3端子デバイス(203)と、このデバイスの第1の端子(208)と第2の端子(210)とに跨って結合された回路(205)とを具備する。回路(205)は好ましくは、デバイス(203)をバイアスするとともに、デバイス(203)によって発生した選択量のノイズをデバイス(203)にフィードバックしてデバイス(203)の第3の端子(216)に存在する比例量の位相ノイズを低減する働きをする。

(もっと読む)

(もっと読む)

移動体通信システムにおける移動局の基地局との周波数同期のための方法及び装置

移動体通信システムにおいて移動局を基地局に同期させる方法において、基準周波数発振器が再調整される。簡単な構成の安価な基準周波数発振器の使用を可能とするため、移動局の温度変化及びその位置の変化に起因する周波数変化が個別に判定/又は予測される。周波数変化が大きいときに、移動局は、周波数変化が小さいときよりも頻繁に基地局と同期化される。  (もっと読む)

(もっと読む)

半導体集積回路

【課題】制御電圧対発振周波数特性が調整可能なVCOを含む半導体集積回路を提供する。

【解決手段】この半導体集積回路は、リング状に直列に接続された複数のインバータと、バイアス電圧VBP1に従って電源電位VDDから複数のインバータに向けてそれぞれ電源電流を流す第1群のPチャネルトランジスタQP11等と、バイアス電圧VBN1に従って複数のインバータから電源電位VSSに向けてそれぞれ電源電流を流す第1群のNチャネルトランジスタQN11等と、バイアス電圧VBP2に従って電源電位VDDから複数のインバータに向けてそれぞれ電源電流を流す第2群のPチャネルトランジスタQP21等と、バイアス電圧VBN2に従って複数のインバータから電源電位VSSに向けてそれぞれ電源電流を流す第2群のNチャネルトランジスタQN21等とを具備する。

(もっと読む)

半導体集積回路

【課題】 高い周波数範囲と低い周波数範囲との広い範囲においてそれぞれ良好な特性を得ることの可能なPLL回路を提供する。

【解決手段】 制御電圧Vcに応じた周波数で発振動作する電圧制御発振器31を有し、発振信号を分周した比較信号φcompと基準クロックφinとの位相比較を行って、該位相比較の結果を制御電圧Vcにフィードバックさせることで基準クロックφinと発振信号φoutとを同期させるPLL回路において、電圧制御発振器31に、制御電圧Vcを制御電流Icに変換する電圧電流変換回路311と、制御電圧にほとんど依存しない補助電流Isを制御電流Icに付加する補助電流付加回路314と、制御電流Icの大きさに応じた周波数で発振動作する周波数可変発振器162と、制御電圧Vcの値に基づき補助電流付加回路314の動作状態のオン・オフを切り換える制御手段32とを設けた。

(もっと読む)

電圧制御発振器の自走周波数の自動調整機能を有する位相ロックループ回路

【課題】 高度の安定性を有する基準クロック信号を発生するための回路を必要とせず、従って、動作安定性がそのような回路の安定性によって影響されることのない、電圧制御発振器(VCO)の自走周波数の自動調整機能を有するPLL回路を提供する。

【解決手段】 PLL回路20では、位相比較器26の比較結果信号が所定レベルにある期間中にVCO22が出力するパルス信号のパルス数をカウントし、そのカウント値に基づいて、マイクロコンピュータ32がディジタルデータを更新する。DAC36がそのディジタルデータに対応したアナログ信号を発生する。このアナログ信号と、位相比較器の比較結果信号をローパスフィルタ28で平滑化した信号とを、結合器30で加え合わせ、その加え合わせた信号をVCOの周波数制御信号とすることで、VCOの自走周波数が自動調整されるようにした。

(もっと読む)

送信機及びプログラムを記憶した記憶媒体

【課題】 2RF対応の送信機において、送信スプリアスを防止すると共に、シンセサイザ部の誤動作を防止し、さらに小型化、低価格化を実現する。

【解決手段】 送信周波数の異なる2つの無線部にそれぞれ設けられQPSK変調波をミキサで周波数変換するためのローカル信号floaを得るためのPLL回路構成されたシンセサイザ部において、VCO13の周波数制御端子のインピーダンスを可変する可変位相器17を設け、この可変位相器17を他方の無線部からの干渉波に対してハイインピーダンスとなるように位相制御信号により制御する。

(もっと読む)

発振器及びそれを用いた位相同期ループ回路

制御信号に信号を加えることによって周波数を制御することが可能な変調機能を備えた発振器(1083)、及びそれを用いたPLL回路(108A)において、発振器は、インバータ又はバッファ及び制御信号により遅延値が制御されるカスケード接続された複数の遅延段(201〜203)を有し、反転位相により閉ループを形成するリング発振器(200)からなり、複数の遅延段の一部において制御信号に変調信号を加えることにより発振周波数を変調する変調機能を備える。 (もっと読む)

541 - 552 / 552

[ Back to top ]