Fターム[5J106GG11]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 制御対象 (2,074) | 波形・レベル変換回路 (32)

Fターム[5J106GG11]に分類される特許

1 - 20 / 32

信号生成装置及び信号生成方法

【課題】任意のジッタが付加された良好な信号波形を有する信号を容易に生成することができる信号生成装置を提供する。

【解決手段】基準クロックを基に制御データに応じた周波数の出力クロックを生成し出力するダイレクトデジタルシンセサイザ(DDS)と、ジッタ設定に応じてDDSの出力周波数を制御するための一連の設定データが格納されたジッタ制御テーブルを有し、基準クロックに同期させてDDSに制御データを供給する制御部とを備え、基準クロックに同期したタイミングで制御データをジッタ制御テーブルに格納されている設定データで順次書き替えることで、短時間かつ一定の時間間隔で制御データの切り替えを行い、周期的に周波数が変化する、すなわちジッタが付加された出力クロックをDDSにより生成できるようにする。

(もっと読む)

デューティ補正付き位相調整回路及びシリアライザ

【課題】クロックのばらつきが引き起こすジッタを抑制することが可能なデューティ補正付き位相調整回路及びシリアライザを提供することを目的としている。

【解決手段】正クロック信号及び負クロック信号が入力され前記正クロック信号と前記負クロック信号のデューティ及び位相を調整した正クロック出力信号及び負クロック出力信号を出力する。

(もっと読む)

PLL回路

【課題】PLLのチャージポンプ回路からの出力電流ミスマッチにより、PLLの特性劣化に繋がるリファレンススプリアスが発生する問題がある。

【解決手段】基準信号とフィードバック信号との位相差に応じて第1、第2のパルス信号を出力する位相比較器と、第1の制御信号に応じて、前記第1、第2のパルス信号のパルス幅をそれぞれ調整した第3、第4のパルス信号を生成するパルス幅調整回路と、前記第3、第4のパルス信号に応じて出力電流を生成するチャージポンプと、前記チャージポンプの出力に接続され、電流を電圧に変換するループフィルタと、前記ループフィルタの変換した電圧を積分した検出結果を出力する検出回路と、前記検出結果に応じて、前記第1の制御信号を生成する制御回路と、を有するPLL回路。

(もっと読む)

周波数制御装置、周波数制御方法、クロック生成回路、電子機器、及び、プログラム

【課題】クロック生成回路におけるハンチング現象を抑制することのできる新たな技術を提供する。

【解決手段】電子機器500は、周波数制御装置510と信号処理部540とを備える。周波数制御装置510は、出力クロック信号を生成するクロック生成回路(クロック生成部512)と、出力クロック信号の周波数を制御する周波数制御部514とを備える。クロック生成部512は、入力された発振制御信号に基づき出力クロック信号を生成する出力クロック生成部(発振部610)と、発振制御信号を生成して出力クロック生成部に供給する発振制御部616とを有する。周波数制御部514は、発振制御部616を制御して発振制御信号を徐々に変化させることにより、出力クロック信号の周波数を徐々に変化させる。

(もっと読む)

同期回路、同期方法、および受信システム

【課題】受信機の個体差や伝送チャネルの時間変動に応じて最適なループゲインを探索できるようにするとともに、伝送フレーム内で複数の変調方式が用いられる場合でも最適なループゲインを探索することができるようにする。

【解決手段】ループゲイン制御部34から初期化フラグを受け取ったPLL制御誤差比較部33は、制御誤差値を算出し、比較器63において、この制御誤差値の大小比較を開始する。制御誤差比較結果に基づいてループフィルタ43−1およびループフィルタ43−2に供給するループゲインを制御する。伝送モード別ゲイン選択部71は、複数の内部のレジスタのうち、伝送モード番号TMに対応するループゲインレジスタG1main[TM]に保持させる値をゲイン制御シーケンサ72から入力される値によって更新する。

(もっと読む)

クロック生成回路および電子機器

【課題】クロック生成回路の回路規模を抑制しつつ、クロック信号の周波数スペクトルを好適に拡散する。

【解決手段】クロック生成回路1の電流制御発振部13は、供給される電流に応じた遅延量で信号を遅延する複数の電流制御遅延回路11を含む閉ループ12によりクロック信号を生成する。位相制御部15〜18は、クロック信号と基準信号とを比較する比較器15を有し、これらの信号の位相差を減らすように変化する制御電流を、複数の電流制御遅延回路11に供給する電流として出力する。拡散電流生成部19は、複数の電流制御遅延回路11の一部に対して、制御電流の替わりに、制御電流と異なる電流値のスペクトラム拡散電流を供給する。

(もっと読む)

同期回路

【課題】小面積で広帯域特性及び低位相雑音特性を得ることが可能な同期回路を提供する。

【解決手段】位相検出器11は、参照信号と帰還信号との位相差を検出する。電圧生成器12,13は、位相検出器の出力信号に基づき電圧を発生する。パルス発生器16は、参照信号に基づきパルス信号を生成する。電圧制御発振器14は、パルス信号に同期して、発振信号を発振する。分周器15は、電圧制御発振器からの信号を分周し、帰還信号を生成する。電圧制御発振器14は、電圧発生回路から供給される電圧レベルをシフトするレベルシフト回路14cと、電圧発生回路からの電圧とレベルシフト回路からのレベルシフトされた電圧により駆動される複数のインバータ回路14a、14bからなるリング発振器とにより構成され、インバータ回路の1つにパルス信号が供給される。

(もっと読む)

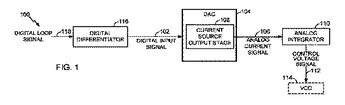

アナログ積分のためのデジタル補償を有するフェイズロックループ

フェイズロックループ(PLL)デバイスは、アナログ積分器によるアナログ電流信号の積分を少なくとも部分的に補償するために、デジタルループ信号を微分するように構成されたデジタル微分器を含む。デジタルアナログコンバータ(DAC)は、デジタル入力信号に基づいてアナログ電流信号を発生する電流源出力ステージを含む。アナログ積分器は、アナログ電流信号を積分して、電圧制御発振器(VCO)を制御するための電圧制御信号を発生する。  (もっと読む)

(もっと読む)

位相誤差検出装置、位相誤差検出方法、集積回路及び光ディスク装置

【課題】周波数誤差が生じているときでも±180度を越える位相誤差の検出を可能とし、PLLの安定性を向上させることができる位相誤差検出装置を提供する。

【解決手段】アナログ入力信号をサンプリングクロックに基づいてAD変換してデジタル再生信号を生成するAD変換部1の出力より位相誤差を検出する位相誤差検出装置は、AD変換部1の出力より前記位相誤差を生成する位相誤差生成部2と、位相誤差を補正する位相誤差補正部3とを含み、位相誤差補正部3は、過去の位相誤差により位相誤差検出範囲を決定し、位相誤差生成部2が生成した位相誤差が位相誤差検出範囲外であった場合に当該位相誤差を補正する。

(もっと読む)

クロック発生装置およびクロック発生装置におけるジッタ低減方法

【課題】よりジッタの少ないクロック信号を発生させること。

【解決手段】周期信号を発生するDDS回路と、入力信号と基準信号とを比較して2値化信号を出力するコンパレータと、を有し、前記DDS回路において発生される前記周期信号に対し、前記基準信号との交差点における変化率を増加させる補正を行う変化率補正手段を備えることを特徴としている。

(もっと読む)

位相補間回路

【課題】線形領域での信号重ね合わせを行なうことなく所望の位相のクロック信号を生成可能な位相補間回路を提供する。

【解決手段】位相補間回路は、一定の周波数及び位相を有する基準タイミング信号のパルスの位相と同一の位相の第1のパルスと前記基準タイミング信号のパルスの位相からずれた位相の第2のパルスとを含むパルス列を生成するパルス列生成回路と、前記第1のパルスの位相と前記第2のパルスの位相との重み付け平均に応じた一定の位相位置にパルスを有する出力パルス信号を前記パルス列に基づいて生成するパルス位相平均化回路とを含み、前記重み付け平均の重みは、所定期間内において前記パルス列に含まれる前記第1のパルスの数と前記第2のパルスの数との比率に応じた重みである

(もっと読む)

位相同期回路、情報再生装置、電子機器、位相同期回路のゲイン制御方法

【課題】PLLゲインを自動制御してキャプチャ時間の短縮やエラーレートの改善を実現するに当たり、ロック判定の手法として種々の方法を提案する。

【解決手段】媒体再生時のPLL動作時に、PLLロック状態を示す情報を用いてPLLゲインを切り替えることでロバストなPLLを実現する。PLLロック状態の検出は、フレームシンクの検出結果、位相誤差の絶対値の積算量、の何れかを評価指標として測定し、一定区間での当該評価指標の大小を判定し、判定結果に基づき位相同期ループがロックしているか否かを示すRF品質信号RQを生成する。フレーム同期信号の検出間隔を監視し、その監視結果に基づきRF品質信号RQを生成するとよい。RF品質信号RQは、概ねPLLがロック時はH、アンロック時はLとなる。RF品質信号RQがHレベルの区間では低倍率となり、RF品質信号RQがLレベルの区間では高倍率となるように、PLLゲインを制御する。

(もっと読む)

位相同期ループの出力VCOにおいて50%デューティサイクルを達成するための方法および装置

【課題】PLLの出力において所望のデューティサイクルを達成するための方法および装置を提供する。

【解決手段】本方法は、制限差動増幅器214を使用して、差動コモンモードクロック信号からデューティサイクルを有するシングルエンドクロック信号を発生させるステップと、シングルエンドクロック信号213のデューティサイクルに応じて差動バイアス電流信号229、230を発生させるステップと、差動バイアス電流信号を制限差動増幅器に与えることによって、シングルエンドクロック信号のデューティサイクルを所望のデューティサイクルに修正するステップとを含む。CML−CMOS変換器回路は、制限差動増幅器214と、シングルエンドクロック信号のデューティサイクルの測定値を発生するための低域フィルタと、(i)測定値を基準電圧と比較し、(ii)比較に応じて差動バイアス電流信号を発生するための第2の差動増幅器とを含む。

(もっと読む)

PLL制御装置及びPLL制御方法

【課題】大規模なPLCシステムに用いても、PLLの受信ダイナミックレンジ拡大、雑音耐力向上が実現でき、アナログ素子の特性のバラツキなどに影響されずに安定して動作し、広範囲な安定したジッタ特性が得られるようにする。

【解決手段】PLL制御装置は、入力信号からタイミング位相ベクトル信号を抽出するタイミング抽出回路と、供給される制御係数に基づき基準信号の位相及び/又は発振周波数を制御するVCXOと、タイミング位相ベクトル信号の位相及び位相差に基づき制御係数を出力する2次PLL回路とを備える。この2次PLL回路は、タイミング位相ベクトル信号に基づき制御係数を発生する制御係数発生回路と、制御計数発生回路からの制御係数につき6dB単位での対数軸上におけるレベル調整を行う第1のレベル調整回路と、第1のレベル調整回路からの制御係数について±6dBレベルの微調整を行う第2のレベル調整回路とを有する。

(もっと読む)

デューティ検出回路およびCDR回路

【課題】入力データが交播パターン以外の場合であっても、高速かつ高精度にデューティを検出する。

【解決手段】デューティ検出回路は、入力データDinとこの入力データDinに周波数および位相が同期したクロックCKとを入力とし、入力データDinをクロックCKに同期してラッチして基準パルス幅を示すパルス信号Refを出力するフリップフロップ1と、入力データDinの平均電圧レベルとパルス信号Refの平均電圧レベルとの差を、入力データDinのデューティ100%からの変動分を示す検出信号Outとして出力する出力回路2とを備える。

(もっと読む)

半導体装置及びその駆動方法

【課題】デューティ補正クロック及びその反転クロックが実質的に正確に180度の位相差を有して出力可能な半導体装置のデューティ補正回路を提供すること。

【解決手段】本発明の半導体装置は、第1クロックと、第2クロックと、前記第1、第2クロックのデューティを補正するための信号である補正信号とを受信し、前記補正信号に基づいて前記第1、第2クロックのデューティに対してデューティ比が補正された第1出力クロック及び第2出力クロックを出力するデューティ比補正回路と、前記第1出力クロックの所定の基準遷移時点と前記第2出力クロックの所定の基準遷移時点との間隔に相当する情報をもつ前記補正信号を形成して前記デューティ比補正回路に出力するクロックエッジ検出部とを備える。

(もっと読む)

同期損失防止方法及び同期損失防止装置

【課題】CDR回路側の原因による接続ノード間の同期化の非成立を抑制し、接続失敗を抑制することができる同期損失防止方法及び同期損失防止装置を提供する。

【解決手段】受信データから同期化クロックを生成するCDR(Clock Data Recovery )回路と、受信データの受信開始から同期化検出時間Nを経過しても同期化クロックに基づく接続ノード間の同期化が非成立のときに、接続失敗処理を行う接続失敗処理段階(S15)と、受信データの受信開始から同期化リトライ判定時間(N/2)を経過しても同期化クロックに基づく接続ノード間の同期化が非成立のときに、CDR回路の動作を補正処理する補正処理段階(S13)とを備える。

(もっと読む)

電圧制御発振回路

【課題】電圧電流変換部の制御電圧入力用MOSトランジスタにデプレッション型を使用した際に発生する発振周波数(バイアス電流)オフセットの製造プロセスばらつきが補正された電圧制御発振回路を提供する。

【解決手段】電圧制御発振回路1は、制御力電圧がゲートに入力される第1のデプレッション型MOSトランジスタ13と、その第1のデプレッション型MOSトランジスタ13のゲート・ソース間電圧が0Vのときのオフセットを補償する第2のデプレッション型MOSトランジスタ15を有し、制御電圧に応じたバイアス電流を発生する電圧電流変換回路3を備える。

(もっと読む)

PLL回路

【課題】基準信号と分周信号の位相差によらず、両信号の位相差を精度よく検出して、その位相差に基づいて発振周波数を制御する。

【解決手段】PLL回路は、信号生成回路1と、位相検波器2と、検波フィルタ3と、周波数調整回路4と、電圧制御型発振器(VCO)5と、分周器&パルス生成回路6と、パルス幅整形回路7とを備えている。信号生成回路1は基準信号の各周期の中間点近傍で論理が変化する中間点信号を生成し、分周信号の論理変化タイミングと中間点信号の論理変化タイミングでそれぞれ論理が変化するようなパルス幅整形信号をパルス幅整形回路7にて生成して、このパルス幅整形信号に基づいてPLL検波電圧を生成するため、基準信号と分周信号が非同期であっても、基準信号と分周信号との位相差に応じたPLL検波電圧を精度よく生成できる。

(もっと読む)

ルビジウム原子発振器

【課題】スイープ電圧発生のための回路規模を小型化し、且つ非ロック時における周波数引き込み動作を自動的に行なうことが可能なルビジウム原子発振器を提供する。

【解決手段】このルビジウム原子発振器100は、OMU1と、増幅器2と、出力信号をデジタル信号に変換するA/D変換器3と、ロック状態又は非ロック状態を判定する状態判定部11と、位相変調信号fmの周波数成分を選択的に出力するBPF13と、スイープ電圧データを生成するスイープ電圧データ生成手段12と、タイマ15と、第1のBPF13の出力信号又はスイープ電圧データ生成手段12の出力信号を選択するSW−A14と、アナログ信号に変換するD/A変換器5と、位相検波して周波数制御信号を生成する位相検波器6と、周波数制御信号を積分処理する積分回路7と、周波数制御信号に従い出力周波数が制御されるVCXO8と、を備えて構成されている。

(もっと読む)

1 - 20 / 32

[ Back to top ]