Fターム[5J106RR06]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成要素 (681) | 固定分周器(ループ内) (52)

Fターム[5J106RR06]に分類される特許

1 - 20 / 52

フラクショナルPLL回路

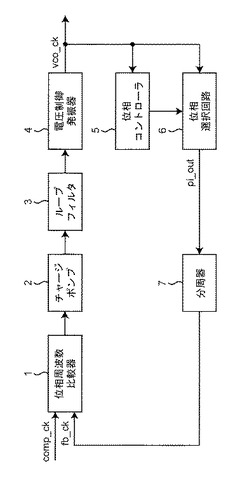

【課題】分周器の分周比を変化させることを動作原理としない新規なフラクショナルPLL回路を提供する。

【解決手段】フラクショナルPLL回路は、位相周波数比較器1、チャージポンプ2、ループフィルタ、電圧制御発振器4、位相コントローラ5、及び位相選択回路6を備える。位相選択回路6は、電圧制御発振器4からの出力クロック信号vco_ckのクロックの1周期を等分した位相のうちのいずれかを選択し、選択された位相に立ち上がりエッジを有する移相クロック信号pi_outを生成し、これを帰還信号として位相周波数比較器1に送る。位相コントローラ5は、移相クロック信号pi_outの周期を出力クロック信号vco_ckの周期から予め決められた移相量で変化させるように、位相選択回路6によって選択される移相クロック信号pi_outの立ち上がりエッジの位相を決定し、決定された位相を選択するように位相選択回路6を制御する。

(もっと読む)

周波数シンセサイザ及び周波数合成方法

【課題】広い帯域幅、高い周波数分解能及び低い位相ノイズを提供する周波数シンセサイザ及び対応する周波数合成方法を提供する。

【解決手段】第1のリファレンス信号を提供するリファレンス信号源22と、合成周波数出力信号を所定の周波数で生成する周波数信号生成部24と、前記合成周波数出力信号を周波数チューニング信号とミキシングして、ミキシング信号46を出力するミキシング部26と、前記周波数チューニング信号を提供する周波数チューニング部28とを備え、前記周波数チューニング部28は、前記周波数チューニング信号を交互に提供する、第1のサブ周波数チューニング部及び第2のサブ周波数チューニング部を有し、前記ミキシング信号から所望の周波数レンジを選択して周波数シンセサイザ出力信号を出力する周波数選択部30を備えた。

(もっと読む)

周波数シンセサイザおよび時間デジタル変換器

【課題】周波数シンセサイザにおいて、ループ帯域内位相ノイズの低減を小面積かつ低電流の構成で実現する。

【解決手段】周波数シンセサイザは、発振器1と、発振器1出力の分周信号CKVと参照信号Frefとの正規化された位相差を検出するTDC回路7とを備え、TDC回路7によって検出された正規化された位相差に基づいて発振器1の周波数を制御する。TDC回路7は、第2の発振器711と、第2の発振器711の出力信号OSC2の周期数をカウントするカウンタ712とを備え、カウンタ712の出力から、分周信号CKVの周期に相当するカウンタ値と、分周信号CKVと参照信号Frefとの位相差に相当するカウンタ値とを得て、これらのカウンタ値に基づいて、正規化された位相差を算出する。

(もっと読む)

周波数シンセサイザ及び周波数シンセサイザの調整方法

【課題】位相雑音を改善すると共に、安定して作動する周波数シンセサイザ等を提供する。

【解決手段】電圧制御発振部から出力された周波数信号と周波数設定部から出力された周波数信号との差分を増幅して得られた差分信号を、前記周波数設定部から出力された周波数信号と直交する検波信号と直交検波して得た両周波数信号の位相差に基づいて前記電圧制御発振部の制御電圧を調整する周波数シンセサイザを立ち上げる際に、前記差分信号を得る差動増幅器から電圧制御発振部を切り離した状態で、第1の位相補正部により予め定めた補正量だけ前記検波信号の位相を補正し、第2の位相補正部により前記検波信号をクロック単位で遅らせて出力することにより、前記周波数設定部よりディジタルの周波数信号が出力された時点から前記差分信号が得られるまでのタイミングと、検波信号が得られるまでのタイミングとをそろえる。

(もっと読む)

高周波発振源

【課題】3倍波を位相関係により抑圧して2倍波を出力する高周波発振源を得る。

【解決手段】2つの入力端子、第1および第2の入力端子から、同一の周波数を入力することが可能なダブルバランスミクサ21と、ダブルバランスミクサ21の第1および第2の入力端子にそれぞれ接続され、同一の周波数を出力する電圧制御発振器11,12と、電圧制御発振器11,12の位相が同相または逆相となるように制御する位相制御手段31とを備え、同一の周波数を出力する2つの電圧制御発振器11,12に0度または180度の位相差を与えてダブルバランスミクサ21に入力することで、3倍波を位相関係により抑圧して2倍波を出力することが可能となる。

(もっと読む)

PLL回路

【課題】高速かつ確実に低雑音特性を得ることができるPLL回路を得ることを目的とする。

【解決手段】相互に異なる移相量PS14,PS24,PS34がそれぞれ設定されており、N分周された発振信号の位相を設定されている移相量だけ変える移相器4−1〜4−3と、移相量の差分の関係が移相器4−1〜4−3のそれぞれに設定されている移相量の差分の関係と一致する条件の下で、相互に異なる移相量PS15,PS25,PS35がそれぞれ設定されており、R分周された基準信号Refの位相を設定されている移相量だけ変える移相器5−1〜5−3とを設ける。

(もっと読む)

PLL回路

【課題】PLL回路の不安定状態や位相雑音特性の劣化を回避する。

【解決手段】

発振周波数が電圧制御発振器からのフィードバック信号と外部から入力される基準信号との位相差に応じて制御されるPLL回路において、前記フィードバック信号を分周する分周器と、前記基準信号を逓倍する逓倍器と、前記分周器からの出力信号と前記逓倍器からの出力信号とをミキシングし周波数変換するミキサと、前記ミキサからの出力信号を分周しデジタル分周信号を出力する第一のデジタル分周器と、前記基準信号を分周しデジタル分周信号を出力する第二のデジタル分周器と、前記第一のデジタル分周器からのデジタル分周信号と、前記第二のデジタル分周器からのデジタル分周信号とを、デジタル位相比較する位相比較器と、を備える。

(もっと読む)

分数分割電荷補償手段を有する周波数シンセサイザ

【課題】分数−N補償法で用いられる電荷ポンプを容易に整合し、分数分割によって導入された望ましくない周波数成分を濾波する。

【解決手段】VCO周波数分割器309と基準周波数信号303との間の位相不整合の分数−NPLLにおける補償が可変電荷ポンプ装置307により行われる。移相比較器305は、電荷ポンプ装置の電荷ポンプのいくつかを早くオンにし、残りの電荷ポンプを遅れてオンにするために補償論理501を有する。このプロセスは、部分電荷を適切に補償するために正確な時点で等価電荷をオンにする。

(もっと読む)

周波数シンセサイザ及び無線送信装置

【課題】VCOの出力帯域を選択設定可能な周波数シンセサイザにおける消費電力を低減すること。

【解決手段】互いに並列に接続されたミキサ111と分周器112とを有する周波数変換回路110を設け、VCO101の周波数帯域選択時に分周器112を用いることにより、VCO101の周波数帯域選択時の位相比較器102の最高動作周波数を低くすることができ、消費電力を低減できる。また、送信時にはミキサ111を用いることにより、送信時のループゲインを下げずに済む。

(もっと読む)

ディジタル制御発振回路、周波数シンセサイザ及び無線通信機器

【課題】ディジタル発振回路自体の位相ノイズを増大させることなく、発振周波数が高く且つ最小周波数変化量が小さい周波数シンセサイザを実現できるようにする。

【解決手段】周波数シンセサイザは、ディジタル制御発振回路11と、発振周波数制御部12とを備えている。ディジタル制御発振回路11は、2本の導体が互いに間隔をおいて並行に配置された並行部15Aと、2本の導体が電気的に絶縁されて交差する交差部15Bとをそれぞれ奇数個有するループ状の伝送線路15と、アクティブ回路17と、第1の可変容量部21及び第2の可変容量部22とを有している。発振周波数制御部12は、第1の可変容量部21に含まれる第1の可変容量素子の高容量状態と低容量状態とを切り替える第1の制御信号をΣΔ変調するΣΔ変調回路40を有している。

(もっと読む)

周波数シンセサイザ

【課題】広帯域を細かく設定でき、周波数の引き込み範囲が広く、かつ消費電力の少ない周波数シンセサイザを提供する

【解決手段】電圧制御発振部1の出力周波数の正弦波信号を直交検波し、検波に用いた周波数信号の周波数との差分の周波数(速度)で回転するベクトルの位相差を取り出して出力周波数の調節に利用するPLLは、出力周波数調節用の第1の位相差検出部71と、周波数引き込み用の第2の位相差検出部74とを備え、前記第1の位相差検出部71の出力に係る信号をディジタル/アナログ変換した結果が予め定めたしきい値を越えたときに、前記第2の位相差検出部74の出力に係る信号をディジタル/アナログ変換する手段105から切り離すと共に、当該第2の位相差検出部74における消費電力を小さくする。

(もっと読む)

フェーズロックループにおけるデジタル制御された発振器の出力のディザリング

PLLのデジタル制御された発振器(DCO)は、DCO_OUT信号がディザされた間隔で変化する周波数を持つように、ディザされる。一例では、DCOは、入って来るデジタルチューニングワードのディザされていないストリームを受け取り、ディザされた基準クロック信号REFDを受け取り、DCO_OUT信号を出力し、その周波数変化がディザされた間隔で起こるようになっている。PLLがセルラー電話の送信機の局部発振器で用いられる場合、DCOの新規なディザリングは、デジタルイメージノイズが、メイン局部発振器周波数からの特定の周波数オフセットで、より少なくなるように、デジタルイメージノイズを周波数拡散する。デジタルイメージノイズの周波数拡散によって、PLL基準クロックの周波数を増大する必要なく、ノイズの仕様を満たすことが可能になる。基準クロックの周波数の増大を回避して、ノイズの仕様を満たすことにより、パワーの消費の増大が回避される。  (もっと読む)

(もっと読む)

周波数シンセサイザおよびその制御方法

【課題】周波数シンセサイザがロック状態にあり、かつ、電圧制御発振器の電圧制御信号が一定の電圧範囲からはずれたときに、ロック状態を保ったまま、電圧制御信号を一定の電圧範囲に戻す。

【解決手段】ローパスフィルタ3が生成する制御電圧信号11によって直流バイアス電圧が制御された可変容量ダイオード52の他に補償用可変容量ダイオード53、54を電圧制御発振器5に設け、制御電圧信号11をモニタし、制御電圧信号11の電圧が可変容量ダイオード52の容量を容易に変えられる範囲外の電圧となったときに制御信号16、17のレベルを変化させるモニタ回路8と、その制御信号16、17のレベルの変化をロック状態が解除されないゆっくりとした電圧変化に鈍らせて補償用可変容量ダイオードに直流バイアス電圧を与える時定数回路72とを備える。

(もっと読む)

PLL回路

【課題】PLLのロック時間を高速化する。

【解決手段】PLLを構成するローパスフィルタ107に対して回路の最大電圧を与えて充電する。その過程でクロック計数カウンタ102が基準クロック10の一周期におけるVCO出力クロックの数をカウントし、所定の2時点でのカウント値により基準クロックとVCO出力クロック27に対する分周クロックとのロックポイントにおける位相差を推定する。この推定は、演算処理回路105において、VCO個体のカタログデータに基づいて行ない、カウンタロード値24を算出し、分周カウンタ109はこれを分周信号28、位相比較器106は該推定位相差とし、充電後にローパスフィルタに供給する。

(もっと読む)

位相差補正回路及び位相差補正方法

【課題】現用系と予備系の基準クロックの位相同期の精度を向上させる。

【解決手段】基準クロック供給システムは、現用系のクロック供給回路及び予備系のクロック供給回路の冗長構成で形成され、現用系から第1の基準クロックを供給すると共に予備系から第1の基準クロックに位相同期させた第2の基準クロックを供給する。位相差補正回路は、基準クロック供給システムから第1及び第2の基準クロックを受信する側で第1及び第2の基準クロック間の位相差を測定し、その位相差情報を基準クロック供給システムにフォードバックさせる位相差測定部を有し、位相差情報に応じて、基準クロック供給システムによる第1及び第2の基準クロックの位相同期動作に補正をかける。

(もっと読む)

電圧制御装置およびクロック出力装置

【課題】電圧制御型水晶発振器(VCXO)から出力される信号の周波数をより高精度に制御することができる電圧制御装置20を提供する。

【解決手段】本発明の電圧制御装置20は、電圧制御型水晶発振器(VCXO)の温度毎の制御電圧値を、異なる条件下で予め2種類測定しておき、実際に温度補正を行う際には、現在のVCXOの温度に対応する制御電圧値を、それぞれの測定条件毎に1つずつ抽出し、抽出した制御電圧値を平均したものを現在の温度における制御電圧としてVCXOに供給する。

(もっと読む)

ローカル信号生成回路

【課題】従来のローカル信号生成回路は、回路面積と消費電力が大きくなる問題があった。

【解決手段】本発明にかかるローカル信号生成回路は、基準信号と帰還信号の位相差を検出し、誤差信号を出力する位相比較器21aと、誤差信号を受け昇圧電圧を生成するチャージポンプ回路22aと、昇圧電圧を整形してチューニング電圧Vtuを生成するループフィルタ23aと、チューニング電圧Vtuに基づき所定の周波数を有する第1の出力信号(I_high、Q_high)を生成する電圧制御発振器24aと、第1の出力信号(I_high、Q_high)を所定の周波数に分周した第2の出力信号(I_low、Q_low)として出力すると共に、第1の出力信号(I_high、Q_high)を前記所定の周波数に分周した分周信号を帰還信号を生成する分周器26aに出力するプリスケーラ25aと、を有するものである。

(もっと読む)

周波数シンセサイザ

【課題】回路規模が小さく、回路構成を簡単にする。

【解決手段】電圧制御発振器19が出力する信号を入力して分周する分周器11、12と、分周器11、12の出力信号を混合する周波数混合器13と、周波数混合器13が出力する2つの周波数の内の一方の周波数の信号を入力して分周する分周器14を、電圧制御発振器19と位相比較器17との間のPLL回路内の帰還ループ中に備える。位相比較器17は、分周器14が出力する信号を一方の入力端に入力し、基準信号発生器16が出力する基準クロック信号を他方の入力端に入力する。ループフィルタ18は、位相比較器17の位相比較結果に基づいた電圧を電圧制御発振器19に与える。電圧制御発振器19は、入力される電圧に対応した周波数で発振する信号を分周器11、12に与える。

(もっと読む)

受信装置とこれを用いた電子機器

【課題】本発明は、温度係数が大きい振動子を用いて受信装置を構成することを目的とする。

【解決手段】上記目的を達成するために、本発明の受信装置1は、受信信号に基づく第2周波数調整部10と、温度センサー部5に基づく第1周波数調整部6を用いて周波数調整を行う。この構成により、使用温度範囲にわたって受信品質の劣化を抑えた周波数調整を行うことができ、温度係数の大きい発振器を高周波受信装置に用いることが可能となる。

(もっと読む)

PLL回路

【課題】PLL回路のロックアップ時間を短縮することである。

【解決手段】VCO選択回路15は、プログラマブル分周器14に設定される分周データに基づいて複数のVCOの内の1つを指定するVCO選択信号を出力する。また、VCO選択回路15は、VCOに与えられる周波数制御電圧と上限の基準値A及び下限の基準値Bを比較し、周波数制御電圧が基準値Aより大きいときには、発振周波数帯域が1つ上のVCOを選択する信号を出力し、基準値Bより小さいときには、1つ下のVCOを選択する信号を出力する。

(もっと読む)

1 - 20 / 52

[ Back to top ]