Fターム[5J500AA12]の内容

Fターム[5J500AA12]に分類される特許

101 - 120 / 897

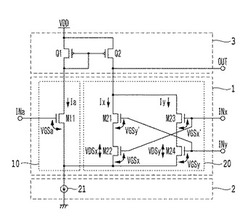

多入力差動増幅器

【課題】各動作モードにおいてレベルシフト回路を用いることなく所望の入力電圧範囲となる多入力差動増幅器を提供する。

【解決手段】差動部1は、バイアス部2と出力部3との間に設けられ、第一入力部10と第二入力部20とを有する。第一入力部10は、ソースがバイアス部2と接続され、ドレインが出力部3と接続された1個のn型MOSFET(M11)からなる。第二入力部20は、直列接続される2個のn型MOSFET(M21)、(M22)と、直列接続される2個のn型MOSFET(M23)、(M24)とが2列に並列接続される。また、入力端INaはM11のゲートに接続され、入力端INxはM22とM23のゲートに接続され、入力端INyはM21とM24のゲートに接続される。バイアス部2は1つの定電流源21を有し、出力部3は2つのp型MOSFET(Q1、Q2)で構成のカレントミラー回路を有する。

(もっと読む)

差動増幅器及びデータドライバ

【課題】従来の差動増幅器は出力誤差が増大する問題がある。

【解決手段】本発明の差動増幅器は、内挿機能を有し、第1導電型トランジスタで形成される第1、第2の差動対(21、22)と、第2導電型トランジスタで形成される第3、第4の差動対(23、24)と、第1、第2の差動対に動作電流を供給する第1、第2の電流源(41、42)と、第3、第4の差動対に動作電流を供給する第3、第4の電流源(43、44)と、第1、第2の差動対にそれぞれ流れる電流量が第1、第2の電流源が出力する動作電流よりも小さくなる第1の動作範囲において、第1の差動対に供給される動作電流の変化点を制御する第1の制御回路51と、第3、第4の差動対にそれぞれ流れる電流量が第3、第4の電流源が出力する動作電流よりも小さくなる第2の動作範囲において、第4の差動対に供給される動作電流の変化点を制御する第2の制御回路52と、を有する。

(もっと読む)

差動増幅回路

【課題】入力電力に対する利得の線形動作領域を広くすることができる差動増幅回路を提供することを課題とする。

【解決手段】差動増幅回路は、ゲートが第1の差動入力信号端子に接続され、ソースが基準電位ノードに接続され、ドレインが第1の差動出力信号端子に接続される第1のトランジスタ(211)と、ゲートが第2の差動入力信号端子に接続され、ソースが基準電位ノードに接続され、ドレインが第2の差動出力信号端子に接続される第2のトランジスタ(212)と、第1のトランジスタのゲート及び第2のトランジスタのドレイン間に接続される第1の可変容量(401)と、第2のトランジスタのゲート及び第1のトランジスタのドレイン間に接続される第2の可変容量(402)と、第1の差動出力信号端子又は第2の差動出力信号端子の信号の包絡線を検波する第1の包絡線検波器(405)とを有する。

(もっと読む)

低歪み可変利得増幅器(VGA)

【課題】非対称な信号の非対称性を補正する。

【解決手段】第1抵抗は、増幅器の入力ノード及び出力ノードの間に接続され、入力ノードは非対称信号を受信する。第2抵抗は、増幅器の入力ノードに接続される。第2抵抗は、線形レジスタを含む。第3抵抗は、第2抵抗に接続される。出力ノードにおける非対称信号を補正するべく、増幅器によって提供される非対称補正量を調整するように第3抵抗を変化させる。非対称補正量は、第1抵抗及び第2抵抗と第3抵抗との組み合わせの関数である。

(もっと読む)

半導体スイッチ

【課題】端子切替時の応答特性を改善した半導体スイッチを提供する。

【解決手段】電源回路部は、正の電源電位よりも高い第1の電位と、負の第2の電位と、を生成する。駆動回路部は、前記電源回路部に接続され、端子切替信号に応じて前記第1の電位をハイレベルとし前記第2の電位をローレベルとする制御信号を出力する。スイッチ部は、制御信号を入力して端子間の接続を切り替える。前記駆動回路部は、第1と、第2のレベルシフタと、第1の回路と、を有する。前記第2のレベルシフタは、前記第1のレベルシフタの出力電位に応じて互いに排他的にオンする第2のハイサイドスイッチと第2のローサイドスイッチとを有し、前記制御信号を出力する。前記第1の回路は、前記端子切替信号に応じて、前記制御信号の電位の変化よりも前に前記第2のローサイドスイッチに前記電源電位を供給し、または前記ハイサイドスイッチに前記接地電位を供給する。

(もっと読む)

出力回路及びデータドライバ及び表示装置

【課題】出力期間の切替時における出力信号の遅延発生を抑制する出力回路、データドライバと表示装置の提供。

【解決手段】出力回路は差動増幅回路110、105,出力増幅回路120と第1の制御回路160、入力端子101、出力端子104、第1乃至第3の電源端子VDD、VSS、VMLを備える。差動増幅回路は前記入力端子の入力信号と前記出力端子の出力信号を入力する差動入力段110と第1及び第2のカレントミラー130、140を備える。出力増幅回路120は第1の電源端子VDDと出力端子104との間に接続された第1導電型の第1のトランジスタ121と出力端子104と第3の電源端子VMLとの間に接続された第2導電型の第2のトランジスタ122とを備える。第1の制御回路160は、第1導電型の第3のトランジスタ161と第1のスイッチ162を備える。

(もっと読む)

電流電圧変換回路、物理量測定装置

【課題】 回路規模の増加を抑えつつ、高い精度の電流電圧変換を行い、低ノイズの電圧信号を出力する電流電圧変換回路等を提供する。

【解決手段】 電流電圧変換回路10であって、電圧信号101P、101Nを出力するオペアンプ20と、入力された電流信号100P、100NのDCオフセット電流に応じた電荷を充放電する第1のキャパシタ40P、40Nと、オペアンプのオフセット電圧に応じた電荷を充放電する第2のキャパシタ41P、41Nと、第1の期間においてオン状態となり第2の期間においてオフ状態となる第1のスイッチ30P、30Nおよび第3のスイッチ32P、32Nと、第1の期間においてオフ状態となり第2の期間においてオン状態となる第2のスイッチ31P、31Nとを含む。

(もっと読む)

スイッチトキャパシタ積分および加算回路

【課題】単一の演算増幅器を使用して積分器と加算器の両方を実現するスイッチトキャパシタ回路を提供する。

【解決手段】1つの入力信号は、(1)1つまたは複数の積分ブランチと、(2)1つまたは複数の第1の加算ブランチとを介して演算増幅器の入力に送られる。第2の入力信号は、1つまたは複数の第2の加算ブランチを介して演算増幅器の入力に送られる。ブランチの各々は、キャパシタと、異なるクロック位相によって制御されるいくつかのスイッチとを含む。スイッチトキャパシタ回路はシングルエンドまたは差動とすることができる。

(もっと読む)

増幅回路

【課題】負帰還回路の構成によってゲインが変化することを防止できる増幅回路を提供する。

【解決手段】オペアンプ1において、初段増幅回路10は、反転入力端子41に入力される入力信号61と、非反転入力端子42に入力される入力信号62とを増幅して初段増幅信号を出力する。後段増幅回路20は、後段増幅信号を出力する。初段増幅回路10において、トランジスタTR1は、正成分61Aを入力とするエミッタフォロワ回路を形成する。トランジスタTR2は、負成分61Bを入力とするエミッタフォロワ回路を形成する。これにより、オペアンプ1における反転入力端子41側の入力インピーダンスを高くすることができる。トランジスタTR5は、正成分61A,62Aを増幅して初段増幅信号の正成分を出力する。トランジスタTR6は、負成分61B,62Bを増幅して初段増幅信号の負成分を出力する。

(もっと読む)

駆動回路、及び、光送信装置

【課題】変調信号の大きさ及び応答速度を向上可能な駆動回路及び光送信装置を提供する。

【解決手段】差動信号の入力に応じて発光素子LDの駆動電流を増減する駆動回路3である。差動信号の正相信号Vinpが入力される端子と、差動信号の逆相信号Vinnが入力される端子と、発光素子LDのアノードに接続されている端子と、正相信号Vinpが入力される端子及びアノードに接続されている端子に接続されている正相信号処理回路と、逆相信号Vinnが入力される端子及びアノードに接続されている逆相信号処理回路と、を備える。正相信号処理回路は、正相信号Vinpに応じて、駆動電流を増加するように制御し、逆相信号処理回路は、逆相信号Vinnに応じて、駆動電流を減少するように制御する。

(もっと読む)

差動増幅回路および液晶表示装置

【課題】消費電流を増加させずにスルーレートを向上する差動増幅回路、表示用駆動回路を提供する。

【解決手段】差動増幅回路は、差動信号を入力する入力段と、入力段の出力に基づいて容量性負荷を駆動する出力段とを具備する。入力段は、差動信号を入力する差動信号入力部(MN1/MN2、MN11/MN12/MP21/MP22)と、差動入力部にバイアス電流を供給する電流源(MN3、MN10/MP20)と、電流源(MN3、MN10/MP20)に並列に挿入される可変容量(Cs)を含むスルーレート調整部(414、415)とを備える。

(もっと読む)

広帯域増幅器

【課題】高い周波数までの二次歪成分を除去し、出力電流信号の線形性を向上させることができ、二次歪耐性(IIP2)を向上させることができる広帯域増幅器を実現する。

【解決手段】第1及び第2のMOSトランジスタQ1,Q2による差動対が発生する二次歪成分電流と逆極性の電流信号を差動対の負荷電流源となる第3及び第4のMOSトランジスタQ3,Q4によって発生し、逆極性の二次歪電流を相互に打ち消し合うように作用させて線形性を向上させ、更に、第1及び第2のMOSトランジスタQ1,Q2の入力へのバイアスを設定する第1のバイアス回路を第1及び第2のMOSトランジスタのドレイン電流が流れるように、且つ、該ドレイン電流をゲート電圧で二回微分した成分の絶対値が極小となるようなバイアス値を得るようにし、且つ、第3及び第4のMOSトランジスタQ3,Q4のサイズを二次歪み成分が主成分である電流を生成するように設定する。

(もっと読む)

半導体集積回路

【課題】DCオフセットキャンセル回路の回路規模と消費電力とを低減する。

【解決手段】差動増幅器5の非反転出力端子と反転出力端子にDCオフセットキャンセル回路51の差動入力端子が接続され、キャンセル回路51の出力信号は差動増幅器5の出力DCオフセット電圧を低減する。回路51はオンチップローパスフィルタ51と直流制御増幅器512を有し、フィルタ511は第1定電流源CS1、差動対の第1と第2のトランジスタ素子Mp1、Mp2、オンチップ容量C1を含む。第1定電流源CS1は素子Mp1、Mp2の共通電極に接続され、回路51の差動入力端子Vinp、Viinは素子Mp1、Mp2の制御入力電極に接続される。オンチップ容量C1の一端と他端に素子Mp1、Mp2の出力電極とが接続され、直流制御増幅器512は容量C1の両端の電圧に直流的に応答する。

(もっと読む)

送信装置および送受信システム

【課題】受信装置の終端抵抗器の抵抗値がばらついている場合であっても安定した通信を行うことができる送信装置を提供する。

【解決手段】送信装置10Aは、第1トランジスタ11、第2トランジスタ12、電流源13、送信回路14、差演算部15および電流調整部16を備える。トランジスタ11,12は差動対を構成している。差演算部15は、トランジスタ11,12のうちの一方がオン状態で他方がオフ状態であるときの第1出力端10aおよび第2出力端10bそれぞれからの出力電圧値を入力して、これら2つの出力電圧値の差(対象電圧)を求める。電流調整部16は、この対象電圧を入力するとともに、参照電圧入力端10dに入力された参照電圧を入力して、参照電圧に基づいて対象電圧を評価し、その評価結果に基づいて、対象電圧が目標値または目標範囲内となるように電流源13の出力電流値を調整する。

(もっと読む)

バイアス回路

【課題】プロセス、温度及び/又は電源電圧の変動による電流源の電流の変動を防止することができるバイアス回路を提供することを課題とする。

【解決手段】バイアス回路は、第1の定電位のノードと前記第1の定電位よりも低い第2の定電位のノードとの間の第3の電位のノードに接続される第1の抵抗(R11)と、ドレインが前記第1の抵抗を介して前記第3の電位のノードに接続され、ゲート及びソースが前記第2の定電位のノードに接続されるデプレッション型電界効果トランジスタ(Q11)とを有し、前記デプレッション型電界効果トランジスタのドレインは、第1の電流源のバイアス電圧を出力する。

(もっと読む)

信号レベル変換回路、物理量検出装置及び電子機器

【課題】第2の入力信号に重畳されたノイズを増幅せずに第1の入力信号の信号レベルを変換することができる信号レベル変換回路並びにこれを用いた物理量検出装置及び電子機器を提供すること。

【解決手段】信号レベル変換回路1は、第1の差動増幅回路10と第2の差動増幅回路20とを含む。第1の差動増幅回路10は、第1の入力信号と第2の入力信号の電位差をG1倍して出力する。第2の差動増幅回路20は、第1の差動増幅回路10の出力信号と第2の入力信号との電位差をG2倍して出力する。この2つのゲインG1とG2は、G1×G2<0かつ0<−(G1+1)×G2<2の関係を満たす。

(もっと読む)

トランスコンダクタンスアンプ及びそれを用いたGm−Cフィルタ

【課題】線形性能が優れたGmアンプ、このGmアンプを用いて高速動作が可能で、入力電圧範囲が広く、かつ線形性能の優れたGm−Cフィルタを提供する。

【解決手段】入力信号が端子17、18から供給され、ソース端子が電源端子に接続されるMOSトランジスタ11、12、同相制御信号がゲート端子から供給されるMOSトランジスタ13、14、出力信号を出力する出力端子対の平均電圧を一定にするためMOSトランジスタ13、14のゲート端子に同相制御信号を出力する同相制御アンプ15、入力信号を入力して、MOSトランジスタ11、12に入力される入力信号の大小に応じて基板電圧を制御する基板制御信号をMOSトランジスタ11、12の基板端子に供給する基板電圧制御回路21、22によってGmアンプを構成する。

(もっと読む)

物理量検出方法および物理量検出装置

【課題】物理量の検出精度が低下することを抑制することができる物理量検出方法および物理量検出装置を提供する。

【解決手段】第1スイッチ群SW1〜SW3を制御して第3ノードN3を第1ノードN1に接続すると共に第2スイッチ群SW4〜SW6を制御して第4ノードN4を第2ノードN2に接続した状態で、センシング部10に基準電圧より所定電圧高いまたは低い第1電圧を印加し、センシング部10から出力された電気的信号を増幅回路30で増幅して第1増幅信号を出力する。その後、センシング部10に第1電圧を印加したときの第1、第2スイッチ群SW1〜SW6をそのまま維持し、センシング部10に基準電圧を基準として反対の極性となる第2電圧を印加し、センシング部10から出力された電気的信号を増幅回路30で増幅して第2増幅信号を出力する。そして、演算回路30にて、第1、第2増幅信号を減算する演算工程を行う。

(もっと読む)

半導体集積回路装置

【課題】アンプの動作周波数に依存性を有するバイアス電流を供給することにより、消費電流を大幅に低減する。

【解決手段】DLL回路2は、入力されたクロック信号CKに基づいて、該クロック信号CKの周波数に比例関係を持つ制御電圧VCNTLを生成する。トランスリニア回路3は、DLL回路2が生成した制御電圧VCNTLに基づいて、クロック信号CKの周波数の2乗の関係を持つ電流を生成する。カレントミラー回路5は、トランスリニア回路3が生成した電流からアンプ電流を生成し、アンプ4のテール電流として該アンプ4に供給する。

(もっと読む)

金属検出システム作動方法及び金属検出システム

【課題】2つ以上の送信周波数を使用する金属検出システムを提供する。

【解決手段】少なくとも2つの送信周波数グループから選択される送信周波数を有する送信信号を生成する送信装置3と接続される送信コイル4と、受信装置5に含まれる少なくとも1つの増幅装置14,15の信号入力へ出力信号を提供し、出力信号が、システムが平衡状態にあるように相互に相殺する第1及び第2の受信コイル6,7とを備えた、平衡コイルシステムを含む金属検出システム1を作動させる。制御装置16が、少なくとも1つの増幅装置14,15の信号入力と接続される少なくとも1つの制御可能インピーダンス装置12,13の制御入力に提供される制御信号を送信装置3の送信周波数に従って生成し、送信周波数が増減されるとき、インピーダンス値が増減されるような方法で制御信号が、制御可能インピーダンス装置12,13のインピーダンス値を制御する。

(もっと読む)

101 - 120 / 897

[ Back to top ]