Fターム[5J500AA12]の内容

Fターム[5J500AA12]に分類される特許

61 - 80 / 897

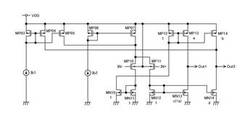

電圧電流変換回路

【課題】差動入力部を有するとともに、出力部を構成するカレントミラー回路のミラー比を調整して入力オフセット電圧をもたせた電圧電流変換回路において、差動入力部および入力オフセット電圧の温度特性を平坦なものにする。

【解決手段】平坦な温度特性を有する第1の定電流Ib1に正の温度特性を有する第2の定電流Ib2を加えた電流をバイアス電流として、MP10及びMP11からなる差動入力部に供給することにより、差動入力部の温度特性とバイアス電流の温度特性とを相殺させて差動入力部の温度特性をゼロ(平坦なもの)にすることができる。また、電流吐き出し型の第1のカレントミラー回路の出力と、電流吸い込み型の第2のカレントミラー回路の出力との接続点を電圧電流変換回路の出力端子Out2とし、この接続点に第1の定電流Ib1に比例した電流を加える構成により、温度特性のない入力オフセット電圧も実現することができる。

(もっと読む)

増幅回路

【課題】追加プロセスなしに、コモンモード入力電圧が定格電源電圧の任意倍数の電圧でも耐えることができる高耐圧の入力段とすることが可能な増幅回路を提供する。

【解決手段】増幅回路の入力段は、入力端子IN1,IN2が接続された第1の差動対トランジスタ10と、N1VDDに接続された第1の入力段電流バイアス手段20と、第1の差動対トランジスタ10と第1の入力段電流バイアス手段20に接続された第1の入力段カスコードトランジスタ群30と、第1の差動対トランジスタ10に接続された第2の入力段カスコードトランジスタ群40と、0VからN1VDDまで変化するコモンモード入力電圧が入力されたときに、第1の差動対トランジスタ10、第1の入力段カスコードトランジスタ群30、第2の入力段カスコードトランジスタ群40のVGSとVGDの絶対値がVDD以内となるバイアス電圧に調整する入力段バイアス調整回路60を備えている。

(もっと読む)

電子回路及び光受光回路

【課題】 入出力信号のオフセットを補償して、入力電流が増大しても増幅動作を行うことができる電子回路及び光受光回路を提供する。

【解決手段】 本発明の電子回路30は、相補的な入力電流を、相補的な電圧信号に変換して出力する差動トランスインピーダンスアンプ10と、出力を入力し、出力が差動トランスインピーダンスアンプ10の入力に接続される差動回路18であって、差動回路18の電流源Is5が入力電流の平均値I2に基づいて制御される差動回路18と、を備えることを特徴とする。

(もっと読む)

差動増幅回路

【課題】基本波周波数のゲイン変化を生じさせることなく、2次高調波のみを抑圧および低減した回路面積の小さい差動増幅回路の実現。

【解決手段】差動対をなし、差動信号S,ZSが入力される2個のMOSトランジスタTr1,Tr2と、2個のMOSトランジスタTr1,Tr2のドレイン間に直列に接続された2個の容量素子C1,C2と、2個の容量素子C1,C2の接続ノードとバイアス電源端子GND間に接続されたインダクタンス素子L1と、を有する差動増幅回路。

(もっと読む)

タッチ感知回路

【課題】隣接した駆動電極のカップリングキャパシタンスの変化の差を検出し、タッチスクリーンパネルに対するタッチ有無を感知することでディスプレイノイズを除去することができるタッチ感知回路の提供。

【解決手段】第1駆動電極に印加された駆動信号と第1駆動電極に隣接した第2駆動電極に印加された駆動信号の入力をそれぞれ受け、微分して第1微分信号及び第2微分信号を生成する微分器と、第1微分信号及び第2微分信号の入力を受け、増幅して増幅信号(out_amp)を出力する増幅器、及び、差動増幅信号の入力を受け、直流信号に変換された検出信号を出力する検出器を具備し、第1駆動電極と第1受信電極、及び、第2駆動電極と第2受信電極が交差するノードに形成された第1カップリングキャパシタンス、及び、第2カップリングキャパシタンスの変化の差をセンシングし、タッチスクリーンパネルのタッチ可否を感知するタッチ感知回路。

(もっと読む)

オペアンプ

【課題】低い電源電圧に対応する生産プロセスで生産された製品に対して高い電源電圧を供給した場合にも、ホットキャリアに起因するオペアンプ特性の劣化を回避することができるオペアンプを提供する。

【解決手段】バイアス電源回路が、2つのカレントミラー回路の間に挿入された一対の抵抗部を有して定電流バイアス電位の他に付加バイアス電位を生成し、差動増幅器が、差動入力トランジスタ対と能動負荷トランジスタ対との間に挿入され且つ当該付加バイアス電位によってバイアスされる電圧降下用トランジスタ対を含むオペアンプ。

(もっと読む)

分布定数型増幅器

【課題】分布定数型差動増幅器の出力波形におけるジッタを低減する。

【解決手段】分布定数型増幅器は、複数の増幅器を有する。複数の増幅器はそれぞれ、固有の遅延時間を持って一の信号源からの入力信号を受ける。また、複数の増幅器はそれぞれ、固有の遅延時間に対応する遅延時間をもって共通の負荷に出力信号を提供する。複数の増幅器それぞれに関して、固有の遅延時間と対応する遅延時間の和は等しく設定されている。複数の増幅器のそれぞれは、一対の差動トランジスタと、該一対の差動トランジスタと当該増幅器の出力との間に直列に挿入された一対のカスコードトランジスタを含む。一対の差動トランジスタは、当該一対の差動トランジスタそれぞれのコレクタ−ベース間の接合容量が準飽和領域の接合容量となるように、バイアスされている。

(もっと読む)

差動増幅回路

【課題】チップ面積を小さくする。

【解決手段】一端がグランド端子14に接続される定電流源13と、ソースが共通に定電流源13の他端に接続され、ゲートが入力端子A、Bにそれぞれ接続される第1および第2の差動対(Q11、Q12およびQ13、Q14に相当)と、第1の差動対のそれぞれのドレインにそれぞれのソースを接続するnMOSトランジスタQ15、Q16と、nMOSトランジスタQ15、Q16のそれぞれのドレインを出力端子C、Dとし、出力端子C、Dと電源端子11との間に接続される負荷部(図1のQ17、Q18に相当)と、を備え、第1の差動対のそれぞれのドレインを第2の差動対の逆相となるそれぞれのドレインに接続し、nMOSトランジスタQ15、Q16のそれぞれのゲートは、nMOSトランジスタQ15、Q16のドレインにそれぞれ接続する。

(もっと読む)

オフセット調整差動増幅回路

【課題】オフセット調整差動増幅回路において、オフセット調整値を温度に対して安定して維持することを提供する。

【解決手段】オフセット調整差動増幅回路は、差動対を構成する第1、第2のMOSトランジスタM1、M2と、第1のMOSトランジスタM1のソースに一端が接続される第1の抵抗R1と、第2のMOSトランジスタM2のソースに一端が接続され、第1の抵抗R1の他端に他端が接続される第2の抵抗R2と、第1、第2の抵抗R1、R2の接続点と第1の電源端子との間に接続され、差動対の動作電流を供給する電流源M6と、第1のMOSトランジスタM1のソースにソースが接続され、第2の電源端子にドレインが接続され、ゲートにオフセット調整電圧VTが与えられ、第1の抵抗R1の両端に生じる電圧を調節するオフセット調整電流I7をオフセット調整電圧VTに応じて制御する第3のMOSトランジスタM7と、を有する。

(もっと読む)

増幅回路

【課題】動作電流を減少させることが可能となり、低消費電力化が可能となる増幅回路の提供。

【解決手段】この発明は、差動対を構成し、互いに逆相の差動入力信号vipx、vinxが入力されるMOSトランジスM1、M2と、MOSトランジスタM1、M2のそれぞれの負荷となるMOSトランジスタM3、M4とを備えている。また、MOSトランジスタM3のバルクには、抵抗R5を介してバイアス電圧が印加されるととともに、キャパシタC3を介して反転出力信号vonが入力される。さらに、MOSトランジスタM4のバルクには、抵抗R6を介してバイアス電圧が印加されるととともに、キャパシタC4を介して出力信号vopが入力される。

(もっと読む)

差動増幅器及びアナログ/デジタル変換器

【課題】スイッチに流れるオフリーク電流の影響を抑制し、利得の発振を抑える。

【解決手段】差動増幅器16は、入力信号が入力される入力端子27,28と、前記入力信号が増幅された出力信号を出力する出力端子25,26と、を備える差動増幅器16であって、前記入力信号を増幅し前記出力信号を生成する増幅部21と、前記増幅部21と電源端子との間に接続され、第1導電型トランジスタT34,T35と、前記第1導電型トランジスタT34,T35のゲート端子をドレイン端子に接続するかまたは前記出力端子25,26に接続するかを切り替える切り替えスイッチ22と、を有する負荷回路23と、前記切り替えスイッチ22のオフリーク電流を低減するキャンセル電流を生成するリークキャンセルスイッチ30と、を備える。

(もっと読む)

差動増幅器

【課題】差動増幅回路、カレントミラー回路およびレール・トゥ・レール回路を組み合わせた電気回路において、外部からの信号に応じて容量の充放電を高速化する機能を維持しつつ、容量の充放電に寄与しない無駄な電流を減少させた差動増幅器を提供する。

【解決手段】外部からの信号に基づくデジタル信号を生成する論理回路を内蔵するスイッチ制御回路を設けて、容量の充放電を高速化するスイッチをこのデジタル信号を用いて制御する。

(もっと読む)

差動増幅回路及び集積回路装置

【課題】差動対を構成する2つのPMOSトランジスターにおけるNBTIの発生を可能な限り防ぐことにより出力オフセット電圧の発生を抑制可能な差動増幅回路及び集積回路装置を提供すること。

【解決手段】差動増幅回路1は、第1の信号が入力されるPMOSトランジスター10(第1のPMOSトランジスターの一例)と、第2の信号が入力されるPMOSトランジスター20(第2のPMOSトランジスターの一例)と、制御信号XSTBに基づいて、PMOSトランジスター10のゲートとバックゲートを同電位にするか否かを選択するPMOSトランジスター14(第1のスイッチ部の一例)と、制御信号XSTBに基づいて、PMOSトランジスター20のゲートとバックゲートを同電位にするか否かを選択するPMOSトランジスター24(第2のスイッチ部の一例)と、を含む。

(もっと読む)

トランスコンダクタンス調整回路、回路装置及び電子機器

【課題】トランスコンダクタンスを精度良く調整することができるトランスコンダクタンス調整回路、回路装置及び電子機器等を提供すること。

【解決手段】トランスコンダクタンス調整回路100は、第1の信号I及び第1の信号Iと位相が90度異なる第2の信号Qが入力され、第1、第2の抵抗素子RA1と、第1、第2のキャパシターCA1、CA2と、演算トランスコンダクタンス増幅器で構成される中心周波数シフト回路110と、トランスコンダクタンス調整信号AGMを出力する調整信号生成回路120とを含む。調整信号生成回路120は、第2の信号Qと第1の出力信号OIとに基づいて、又は第1の信号Iと第2の出力信号OQとに基づいて、又は第1の信号Iと第1の出力信号OIとに基づいて、又は第2の信号Qと第2の出力信号OQとに基づいて、トランスコンダクタンス調整信号AGMを生成する。

(もっと読む)

受信信号処理装置

【課題】回路規模が小さく消費電力が少ない受信信号処理装置を提供する。

【解決手段】受信信号処理装置は、高周波の受信信号に局部発振信号を合成して周波数変換するミキサ部と、多段に構成された複数の利得可変増幅器を含む増幅部と、増幅部により増幅されたアナログ信号をデジタル信号に変換する変換部と、各利得可変増幅器の後段に設けられたスイッチと、利得可変増幅器の出力が後段の利得可変増幅器を迂回して変換部に入力される経路の開閉を設定する迂回スイッチ部と、各利得可変増幅器の出力が後段の利得可変増幅器を介さずに変換部に入力するために、スイッチ及び迂回スイッチ部を制御するスイッチ制御部と、受信信号が補正対象の利得可変増幅器に入力されず、補正対象の利得可変増幅器の出力が後段の利得可変増幅器を介さずに変換部に入力される場合に、補正対象の利得可変増幅器に設定される利得に応じてDCオフセットの補正値を設定するDCオフセット制御部とを含む。

(もっと読む)

差動信号発生回路および電圧制御ゲイン可変増幅器

【課題】電圧制御によりゲイン調整を行うゲイン可変増幅器制御用の制御電圧を、基準電圧を用いることなく生成し、電圧制御ゲイン可変増幅器全体の小型化および消費電力の削減を図る。

【解決手段】ゲイン可変増幅器制御回路を構成する差動対として、nチャネル型トランジスタTR11とpチャネル型トランジスタTR12とを用い、共通のゲイン制御電圧S1をこれらトランジスタTR11およびTR12のゲートに供給する。各トランジスタTR11、TR12を流れる電流は、ゲイン制御電圧S1が増加するにつれて一方は増加し、他方は減少する特性となり、基準電圧を用いたゲイン可変増幅器制御回路と同一特性のゲイン可変増幅器制御電圧を得ることができる。よって、基準電圧発生回路を設ける必要がないため、装置全体の小型化および消費電力の削減を図ることができる。

(もっと読む)

利得可変差動増幅回路

【課題】広いダイナミックレンジを確保しつつ利得を変化させることが可能な利得可変差動増幅回路を提供すること。

【解決手段】この利得可変差動増幅回路12は、差動対トランジスタQ1,Q2,Q3,Q4とそれらのトランジスタのそれぞれのコレクタに接続された負荷抵抗14,15,18,19とそれらのトランジスタのエミッタに共通に接続された電流源16,20とをそれぞれ含む差動増幅回路17,21を有し、次段差動増幅回路21の出力を、帰還トランジスタQ5,Q6を介して初段差動増幅回路17に帰還させる利得可変差動増幅回路において、該初段差動対トランジスタQ1,Q2を流れるべき電流を分岐させる電流分岐回路部12Cと、差動対トランジスタQ1,Q2に電流を供給する電流供給回路部12Bとを備える。

(もっと読む)

フィルタ回路

【課題】 歪特性に優れるフィルタ回路を得る。

【解決手段】 直列に接続された複数のLPFを有するフィルタ回路において、複数のLPFはそれぞれ、スイッチトキャパシタ回路SC、および、SCの出力信号を増幅して出力する全差動型増幅器AMPを有する。1ビットDAC40の出力信号が入力されるLPF1が有するAMP10のコモンモードフィードバック回路は離散時間型であり、フィルタ回路としての出力信号を出力するLPF2が有するAMP20のコモンモードフィードバック回路は連続時間型である。

(もっと読む)

スルーレート制御回路、制御方法及び半導体集積回路

【課題】出力アンプのスルーレートを、出力負荷変動があっても高精度に調整可能なスルーレート制御回路を提供すること。

【解決手段】制御時間設定回路がスルーレートを検出するタイミング信号を発生し、電圧比較回路が、出力アンプの出力信号と、上記のタイミング信号によるタイミングに応じた制御電圧との比較を行う。比較結果に応じて、出力アンプ制御回路が、出力アンプのバイアス電流を制御する。上記した処理を、スルーレート制御期間において複数回繰り返す。

(もっと読む)

差動増幅装置

【課題】 差動増幅装置が出力するオフセット電圧を充分に抑制する。

【解決手段】 差動増幅器10は、キャパシタCを介して+IN端子に入力される信号と、−IN端子に入力される信号の差分を増幅する。スイッチS1は、+IN端子が、キャパシタCを介した信号を入力するか否かを切り替える。抵抗RINは、+IN端子と−IN端子の間に接続される。オフセット電圧補正回路20は、+IN端子がキャパシタCを介した信号を入力しないようにスイッチS1が制御された補正期間において、差動増幅器10の出力信号に基づき差動増幅器10のオフセット電圧を補正する。

(もっと読む)

61 - 80 / 897

[ Back to top ]