Fターム[5J500AA51]の内容

Fターム[5J500AA51]の下位に属するFターム

入力(出力)信号切換型増幅器 (61)

ゲート増幅器、出力信号を遮断できる増幅器 (31)

双方向増幅器 (8)

Fターム[5J500AA51]に分類される特許

361 - 376 / 376

プログラム可能な低雑音増幅器および方法

プログラム可能利得の低雑音増幅器は、第1の基準電圧(VDD)に結合されたソースと、テール電流線(18)に結合されたドレンとを有するテール電流トランジスタ(Q3)を含む。或る差動入力の実施の形態は、複数の差動的に結合された入力トランジスタの対(Q4,Q5;Q7,Q8;Q10,Q11;Q13,Q14)を有する。各対は、第1の入力線(19A)に結合されたゲートと、第1の出力線(26A)に結合されたドレンとを有する第1の入力トランジスタ(Q4,Q7,Q10,Q13)を含む。また各対は、第2の入力線(19B)に結合されたゲートと、第1のトランジスタのソースに結合されたソースと、第2の出力線(26B)に結合されたドレンとを有する第2の入力トランジスタ(Q5,Q8,Q11,Q14)を含む。いくつかまたは全ての対の第1および第2の入力トランジスタのソースは、スイッチ・トランジスタ(Q6,Q9,Q12)のゲートに与えられる制御信号(B1,B2,B3)によりテール電流線(18)に選択的に結合される。  (もっと読む)

(もっと読む)

デュアルモード音声増幅器

音声信号のためのデュアルモード電力増幅器は、低レベルの音声信号では線形モードで、及び高レベルの音声信号では切り替えられたモード(クラスD)で動作する。

(もっと読む)

(もっと読む)

トランスインピーダンスアンプ

【課題】 高感度および広入力ダイナミックレンジを実現でき、かつ、バーストデータに対応した瞬時応答を実現できるトランスインピーダンスアンプを提供する。

【解決手段】 入力端子が信号入力端子に接続されたトランスインピーダンスアンプコア回路210と、トランスインピーダンスアンプコア回路210と同じ構成で入力端子が開放されたトランスインピーダンスアンプコア回路220と、両トランスインピーダンスアンプコア回路210,220の各出力端子が差動入力端子に接続された中間段バッファ回路230と、中間段バッファ回路の差動出力端子が差動入力端子に接続されたヒステリシスコンパレータ251を有し両トランスインピーダンスアンプコア回路210,220の利得を切り替える利得切替判断回路250とを備える。両トランスインピーダンスアンプコア回路210,220にそれぞれ帰還抵抗を具備させ、中間段バッファ回路230の差動出力信号に応じて利得切替判断回路250のヒステリシスコンパレータ251によりそれらの帰還抵抗の値を切り替える。

(もっと読む)

AVアンプ

【課題】マルチチャンネルオーディオシステムの複数のスピーカの中からモニターテレビ装置の内蔵スピーカに代わりをさせるスピーカをユーザの状況に応じて任意に選択する。

【解決手段】サラウンドプロセッサ回路C2は、インプットセレクタ回路C1で選択された入力機器のオーディオ信号を、マルチチャンネルオーディオシステムの複数のスピーカに供給するマルチチャンネルオーディオ信号に変換する。信号経路切り換えスイッチSW1,SW2は、モニターアウト端子CN2のオーディオL,Rチャンネル端子に、ユーザの設定に応じてマルチチャンネルオーディオ信号の一部を選択的に出力する。

(もっと読む)

利得可変型増幅器

【課題】高電力レベルの高周波信号が入力されても低消費電力状態の維持を可能とする。

【解決手段】カスコード接続された第1及び第2のFET1,2により増幅経路101においてカスコードアンプが構成され、また、第4のFET4を中心としてバイパス経路102が構成される一方、第1のFET1のドレインD1と第2のFET2のソースS2の接続点には、第3のFET3のドレインD3が接続されると共に、この第3のFET3のソースS3は接地されており、高電力レベルの高周波信号が入力された際には、第1及び第2のFET1,2を非動作状態とする一方、第3のFET3を導通状態とすることで、第1及び第2のFET1,2の段間を低インピーダンスにして、段間に掛かる入力信号の振幅を低減し、低消費電力状態の維持を可能としたものである。

(もっと読む)

電力増幅器

【課題】 熱的に安定し、かつ、低歪で、低消費電力の電力増幅器を提供する。

【解決手段】 この電力増幅器は、第1のスイッチ回路SW1が導通状態で第2のスイッチ回路SW2がベースバイアス電圧を高くする場合に、第2のインピーダンス回路ZZ1による高周波成分に対するバイパス経路が形成される。これにより、大きな出力電力を要求される場合に、高周波成分についてのバイパス経路が形成され、電流集中の発生を抑えながら高い線形性を実現できる。一方、第1のスイッチ回路SW1が開放状態で第2のスイッチ回路SW2がベースバイアス電圧を低くする場合には、上記バイパス経路は直流的にも交流的にも開放となり、入力信号が増大した際のコレクタ電流の増加を抑制でき、消費電流を少なくすることができるので、バッテリーの消耗を抑えることが可能になる。

(もっと読む)

定電流回路、駆動回路および画像表示装置

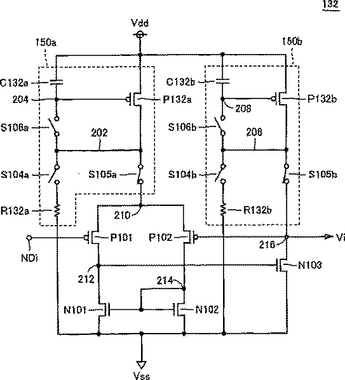

電圧発生回路114に含まれる第1の増幅回路(132)は、P型TFT素子(P101,P102)およびN型TFT素子(N101,N102)によって構成される差動回路と、定電流回路(150a,150b)と、N型TFT素子(N103)とを含む。定電流回路(150a;150b)は、P型TFT素子(P132a;P132b)と、キャパシタ(C132a;C132b)と、スイッチ(S104a〜S106a;S104b〜S106b)と、抵抗素子(R132a;R132b)とからなる。キャパシタ(C132a;C132b)は、電圧設定時、すなわちダイオード接続されるP型TFT素子(P132a;P132b)に電流が供給されているときのノード(204;208)の電圧を保持する。  (もっと読む)

(もっと読む)

スピーカ用増幅装置

【課題】 放熱部の大きさを抑えて装置全体を小型化することが出来るスピーカ用増幅装置1を提供する。

【解決手段】 本発明に係るスピーカ用増幅装置1は、少なくとも4台のスピーカ3〜8にそれぞれ音響信号を供給する少なくとも4つの増幅回路11a、11bを具えており、これら少なくとも4つの増幅回路は複数のブロック10a、10b、10cに分けられている。そして、該スピーカ用増幅装置1は、ブロック毎に、ブロックを構成する複数の増幅回路11a、11bにそれぞれ入力される音響信号の信号レベルを比較する比較器16を具えており、ブロック毎に、前記比較器16の比較結果に基づいて、少なくとも1つの増幅回路に対して高い電源電圧が供給されると共に該少なくとも1つの増幅回路以外の増幅回路に対して低い電源電圧が供給される。

(もっと読む)

差動増幅器を用いた差動信号受信装置

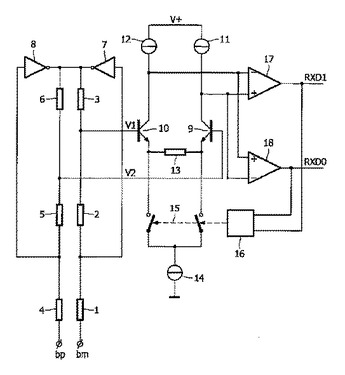

本発明は、差動型データバス用受信器であって、2つの抵抗分岐(1、2、3:4、5、6)と、2つのトランジスタ(9、10)を有する差動増幅器と、抵抗器(13)と、さらに電流源(14)からの電流を、2つのトランジスタ(9、10)を結合する抵抗器(13)のいずれかの側に切り替え可能なスイッチ(15)を制御する制御ロジック(16)と、さらに反対極性を有する差動増幅器の2つのトランジスタ(9、10)に結合された2つの演算増幅器(17、18)とを有し、受信器において、制御ロジックが、2つの演算増幅器の出力信号から、「0」または「1」のどちらがバス上に予測されるかを検出するとともに、その受信器がそれに従って、受信されたバス信号との比較が行われるように、スイッチ(25)を設定する、受信器に関する。  (もっと読む)

(もっと読む)

増幅装置

【課題】 高周波増幅器または受信機が歪みによる干渉波の影響を受けた時、受信品質劣化や受信できない状態を回避できる増幅装置を得ることを目的とする。

【解決手段】 交流信号を伝送する交流信号伝送路が分岐した第1分岐伝送路が接続され、この第1分岐伝送路から入力される上記交流信号を、第1制御信号に応じた増幅値で出力する第1増幅器39aと、上記交流信号伝送路が分岐した第2分岐伝送路が接続され、この第2分岐伝送路から入力された上記交流信号を、第2制御信号に応じた増幅値で出力する第2増幅器39bと、上記第1増幅器の増幅値と上記第2増幅器の増幅値との和を出力する出力合成部310と、を備え、

上記第1制御信号及び上記第2制御信号は、上記第1増幅器または上記第2増幅器のいずれか一方の増幅値を、いずれか他方の増幅値に影響が無い程度に小さくするよう制御する信号とした。

(もっと読む)

可変利得増幅回路

【課題】 利得を可変にしつつ、信号源とのインピーダンスマッチングを実現する。

【解決手段】 可変利得増幅回路1は、所定の利得を有し、一端が回路出力部に接続される増幅器A1と、上記増幅器A1とは異なる利得を有し、一端が上記回路出力部に接続される増幅器A2と、一端が回路入力部に接続され、他端が上記増幅器A1の他端に接続されるインダクタL1と、上記インダクタL1と共に変圧器Tを構成し、一端が接地され、他端が上記増幅器A2の他端に接続されるインダクタL2と、を備えた構成である。これにより、入力信号Vinが入力される信号経路に応じた入力インピーダンスの変動を抑えることができ、信号源とのインピーダンスマッチングを担保できる。

(もっと読む)

高忠実度で高出力の切り替え式増幅器

【課題】大きな出力を提供しかつ高い忠実度を与える出力段アーキテクチャを提供する。

【解決手段】傾斜増幅器出力段(10)を備えた傾斜増幅器機構について記載している。本デバイスは、MRIシステム内にあるような傾斜コイル(18)に対して電流を提供するために使用することができる。開示した回路は、第1の電圧で動作している第1のブリッジ増幅器(12)と、第2の電圧で動作している第2のブリッジ増幅器(14)と、第3の電圧で動作している第3のブリッジ増幅器(16)と、傾斜増幅器制御段(30)との直列結合を含んでいる。これらの増幅器は異なるレベルの出力電圧を提供することができると共に、あるレンジの出力電圧及び電流レベルを提供するために異なる時刻及び周波数で切り換えることができる。

(もっと読む)

周辺回路切換による電力増幅器の効率的電力制御

【課題】低電力動作モードでも高い効率および高い直線性を維持できるRF電力増幅器を提供する。

【解決手段】第1の増幅器出力段および並列接続の第2の増幅器出力段を有する電力増幅器を提供する。この第1の増幅器出力段は高電力動作モードおよび低電力動作モードの両方の期間中にイネーブルされる(すなわち、十分にバイアスされる)。第2の増幅器出力段は低電力動作モードの期間中にディスエーブルされ、高電力動作モードの期間中だけイネーブルされる。これら第1の増幅器出力段および第2の増幅器出力段はいずれもごく低レベルの休止電流状態で動作することはないので、この電力増幅器の直線性は高電力動作モードおよび低電力動作モードの両方について維持される。  (もっと読む)

(もっと読む)

切換可能な可変出力電力レベルを有する飽和電力増幅器

【課題】出力電力レベルを選択でき、所望の電力レベル範囲全体にわたって電力効率の高い無線周波数電力増幅用の飽和増幅回路を提供する。

【解決手段】互いに並列に接続した二つの増幅器を電力増幅器に備える。第2の増幅器の受ける入力は第1の増幅器の受ける入力の遅延バージョンとする。第1の増幅器の出力は、第2の増幅器の出力とほぼ同相になるように、遅延をかける。低出力電力動作の場合は第1の増幅器のみをイネーブルする。高出力電力動作の場合は第1の増幅器および第2の増幅器の両方をイネーブルする。これら第1および第2の増幅器を飽和増幅器として動作させる。第1の可変出力電力制御信号で第1の増幅器サブセクションの出力電力を制御し、第2の可変出力電力制御信号で第2の増幅器サブセクションの出力電力を制御する。  (もっと読む)

(もっと読む)

高精度のチョッパ安定化電流ミラー

チョッパにより安定化させられた電流ミラーは、入力電流Iinをミラーするように接続された1対のFETを含んでいる。一実施形態においては、スイッチング回路網S1およびS2では、これらの各入力がこれらのFETのドレインに接続されており、それぞれクロック信号CLK1およびCLK2を用いて動作させられる。r0ブースト増幅器A1は、その入力がS2のこれらの出力に接続されており、その出力が、クロック信号CLK2Sを用いて動作させられるスイッチング回路網S3を経由して1対のカスコードFETのこれらのゲートに接続され、一方のカスコードFETのドレインが、Iinに接続され、他方のドレインが、このミラーの出力Ioutを供給する。S1は、不整合エラーを低下させるようにクロックされ、S2およびS3は、A1のオフセット電圧に起因したエラーを低下させるようにクロックされ、CLK2およびCLK2Sは、寄生キャパシタンスに起因したエラーを低下させるためにCLK1に対してシフトされる。  (もっと読む)

(もっと読む)

差動増幅装置

入力段(1)と出力段(2)とを有する差動増幅装置(53)が提供される。入力段(1)は、少なくとも1つの制御可能な電流源(11)を有して差動増幅器(3,4)のバイアス信号を制御するオフセット補償段(10)が接続される差動増幅器(3,4)を有する。望ましくは計装用増幅器として使用可能な本発明の差動増幅装置により、非常に正確な入力オフセットの補償が実施可能である。  (もっと読む)

(もっと読む)

361 - 376 / 376

[ Back to top ]