Fターム[5J500AH18]の内容

Fターム[5J500AH18]に分類される特許

1 - 20 / 74

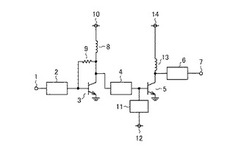

送信増幅器

【課題】低ひずみ、低雑音、且つ小形な送信増幅器を得る。

【解決手段】多段接続した増幅器のうちの少なくとも1段以上に、バイポーラトランジスタ3のコレクタ電極とベース電極との間に接続された抵抗9を備え、出力電源10からインダクタ8および抵抗9を介してバイポーラトランジスタ3のベース電極に入力バイアスを供給する増幅器を備える。

バイポーラトランジスタ3の動作条件を決める入力バイアスを、抵抗9と出力電源10とにより決定するので、バイアス回路によるひずみがバイポーラトランジスタ3に重畳されないため、低雑音な送信増幅器を実現することができる。

また、入力バイアスを供給するためだけにインダクタを設ける必要がないため、小形な送信増幅器を実現することができる。

(もっと読む)

電力増幅器における動的バイアス制御

【課題】平均電力効率(APE)が改良されることができるセルラ電話における電力増幅器を提供する。

【解決手段】RF出力電力増幅器(PA)は、第1および第2のAB級増幅回路を含んでいる。高電力オペレーティングモードにおいて動作する場合、第1の増幅器はPA出力端子を駆動する。第1の増幅器のパワートランジスタ(単数または複数)は、高い出力電力での効率性および線形性を最適化するように、バイアスをかけられる。低電力オペレーティングモードにおいて動作する場合、第2の増幅器は出力端子を駆動する。第2の増幅器のパワートランジスタは、低い出力電力での効率性および線形性を最適化するように、バイアスをかけられる。増幅器のパワートランジスタを適切にサイジングすることによって、エミッタ電流密度は、実質的に等しく維持されるので、PA電力利得は、2つのオペレーティングモードにおいて同じである。

(もっと読む)

RF電力増幅器およびその動作方法

【課題】ランプアップまたはランプダウンにおいてスイッチングスペクトラムの劣化を軽減すること。

【解決手段】初段と最終段のバイアス回路81、83が、初段と最終段の増幅回路41、43のアイドリング電流を決定する。電力検出回路5、6は、最終段出力信号Poutの信号レベルに応答する電力検出信号VDETを生成する。誤差増幅器7に検出信号VDETと目標電力信号VRAMPが供給され、電力制御電圧VAPCが制御信号増強回路9の入力に供給され、出力から増強制御信号VENを生成する。制御信号増強回路9は、所定の非線型の入出力特性を有する。増強制御信号VENが初段と最終段のバイアス回路81、83とに供給され、初段と最終段の増幅回路41、43のアイドリング電流は増強制御信号VENによって制御され、RF電力増幅器の制御利得の低下が補償される。

(もっと読む)

容量性負荷駆動回路および流体噴射装置

【課題】変調信号のオンデューティー比が上限付近の状態が継続しても、D級増幅器を正

常に動作させて駆動信号を出力が可能とする。

【解決手段】駆動波形信号から生成した変調信号を電力増幅した後、平滑化することによ

って駆動信号を生成する。変調信号を電力増幅するデジタル電力増幅器では、電源とグラ

ンドとの間で2つのNチャンネル(以下ch)MOSFETをプッシュ・プル接続し、更

に、電源側のNchMOSFETに対して並列にPchMOSFETを接続する。こうす

れば、電源側のNchMOSFETをONにするためのブートストラップコンデンサーに

蓄えられた電荷が不足してNchMOSFETをONにすることができない場合でも、P

chMOSFETをONにすることで電力増幅を行うことができ、駆動信号を出力するこ

とが可能となる。

(もっと読む)

スイッチングアンプおよびパルス幅変調回路

【課題】 電源パンピング現象によって生じる回路素子の破損を、動作を停止させることなく防止すること。

【解決手段】 コンデンサC1の充電電圧の絶対値が所定値以上であることを検出回路25が検出すると、定電流生成手段のスイッチ手段がオン状態にされ、定電流Iの電流値が大きくなる。これにより、第1電流I1および第2電流I2の電流値が大きく、かつ、その比が小さくなる。従って、コンデンサC1、C2の充電速度の比が小さくなり、PWM信号OUTの変調度が低下する。従って、MOSFET16が長期間連続してオン状態になることがなくなり、コンデンサC1の充電電圧が所定値以上である状態が回避され、コンデンサC1の破損を防止できる。

(もっと読む)

差動増幅回路、レギュレータモジュール及びハイパワーアンプ

【課題】製造時の工程及び製品の消費電力の点で優れたレギュレータモジュール、及びそれを用いたバイアス回路を提供する。

【解決手段】パワーアンプモジュールとレギュレータモジュール801を含むパワーアンプをバイポーラトランジスタと電界効果トランジスタとを同一基板上に備える技術によって1チップで構成する。レギュレータモジュール801はデプリーション型トランジスタによる差動増幅回路を内包する。該差動増幅回路の一方のFETQ4のソース端子を、ダイオード接続したバイポーラトランジスタQ7を介して、FETQ3のソース端子と接続することで、バイポーラトランジスタQ7の電位差をレギュレータの出力電圧とすることが可能となる。

(もっと読む)

定電圧回路

【課題】電界効果トランジスタの閾値電圧に対する依存性が抑制された定電圧を供給する定電圧回路を提供する。

【解決手段】本発明にかかる定電圧回路は、第1および第2のノードで互いのドレインおよびゲートが共通接続される電界効果トランジスタQ11およびQ12と、電界効果トランジスタQ11、12のゲートが共通接続される前記第2のノードと電界効果トランジスタQ12のソースとの間に接続される抵抗器R11と、コレクタが前記第2のノードに接続されるバイポーラトランジスタQ13と、電界効果トランジスタQ12のソースに接続し、バイポーラトランジスタQ13のベースにバイアス電圧を供給するバイアス回路101と、を備え、電界効果トランジスタQ11、12のドレインが共通接続される前記第1のノードに電圧源Vbatが接続され、電界効果トランジスタQ11のソースから定電圧を供給する。

(もっと読む)

バンドギャップリファレンス回路および回路を製造する方法

【課題】最低所要供給電圧が低く、小さいチップ領域を占め、電流消費が低く、供給電圧の変動に強いバンドギャップリファレンス回路を提供する。

【解決手段】電圧ジェネレータ(VG)と、供給回路(SC)と、バイアス要素(BB)および制御要素(CB)を含むバイアス回路(BC)とを、バンドギャップリファレンス回路は含む。供給回路(SC)の制御要素(CS)およびバイアス回路(BC)の制御要素(CB)のうちの一つは、擬似格子整合型高電子移動度トランジスタまたはヘテロ接合バイポーラトランジスタを含み、供給回路(SC)のバイアス要素(BS)およびバイアス回路(BC)のバイアス要素(BB)のうちの一つは、ロングゲート擬似格子整合型高電子移動度トランジスタまたは抵抗を含む。擬似構成整合型高電子移動度トランジスタおよびヘテロ接合バイポーラトランジスタは、GaAs BiFET技術プロセスを用いて製造される。

(もっと読む)

FET用自動バイアス調整回路

【課題】サーミスタを使わずに簡便な回路で所望の温度補償が達成できると共に、抵抗での消費電力が増加しないようにし、また温度補償の特性変更や調整を抵抗の仕様等の変更のみで任意に行えるようにする。

【解決手段】FET1のゲート電圧を制御するためのPNPの第1トランジスタQ1 が設けられ、上記FET1のドレイン及び第1トランジスタQ1 のエミッタには、FET1のドレイン電流検出用の抵抗R4を介して正電源4が配置され、第1トランジスタQ1 のベースと接地との間に第1抵抗R1、このベースと正電源4との間に第2抵抗R2が接続される回路で、上記第2抵抗に対し並列となるように、直列接続のダイオード(PNPトランジスタでもよい)D1 と第3抵抗R3を接続する。これによれば、R2とR3のそれぞれの値の組合せの調整で任意の温度勾配のドレイン電流を得ることができる。

(もっと読む)

回路ユニット、回路ユニットを有するバイアス回路、並びに第1及び第2の回路ユニットを有する差動増幅回路

ヘテロ接合バイポーラトランジスタ及びロングゲート疑似格子整合高電子移動度トランジスタを備える回路ユニット(CU)。前記ロングゲート疑似格子整合高電子移動度トランジスタのソース(S)又はドレイン(D)が、前記ヘテロ接合バイポーラトランジスタのコレクタ(C)又はエミッタ(E)に電気的に結合される。 (もっと読む)

カレントミラー回路

【課題】低電圧での動作を可能とし、アーリー効果による電流比の悪化を抑圧可能とする。

【解決手段】

NPN型の第1及び第2のトランジスタ1,2のベース、第1のトランジスタ1のコレクタ、及び、デプレッション型のNチャンネルMOSトランジスタである第3のトランジスタ3のゲートが相互に接続されると共に、定電流源4に接続される一方、第1及び第2のトランジスタ1,2のエミッタは、共にグランドに接続され、第2のトランジスタ2のコレクタは、第3のトランジスタ3のソースに接続されて、この第3のトランジスタ3のドレインに出力可能に構成されてなり、低電圧での動作を可能とし、アーリー効果による電流比の悪化が抑圧可能となっている。

(もっと読む)

電力増幅器用バイアス回路

【課題】この発明は、増幅用トランジスタのコレクタ電圧に応じてアイドル電流を制御することにより、低歪特性を実現することができる電力増幅器用バイアス回路を提供する。

【解決手段】電力増幅器用バイアス回路が、電圧駆動バイアス回路と電流駆動バイアス回路とを並列に設けた併用バイアス回路を備えている。Vc2によるアイドル電流制御回路10が付加されている。増幅用トランジスタのコレクタ電圧Vc2がTrx2の閾値電圧(約1.3V)以下の場合、Trx2がオフする。Vref(2.4〜2.5V)はTrx1とDx2がオンする電圧(約1.3+0.7V)より高いため、電流Ix1が流れてTrx1がオンする。そのため、抵抗Rx1やRx2を介して、Tr2aやTr2bのベースからGNDへ向けて、電流が引き抜かれる。その結果、Tr2a、Tr2bのアイドル電流が下がる。

(もっと読む)

バイアス回路

【課題】動作中におけるノイズの侵入によって、回路動作が停止しても、起動回路を再度駆動させることなく、また、外部からリセット信号を入力させることなく、回路動作を復帰可能とし、起動回路における消費電流の低減を図る。

【解決手段】一定の電流を外部へ供給する基準電流供給部100と、基準電流供給部100からの電流供給を受け、供給された電流に電流を生成する定電流供給部110と、基準電流供給部100と定電流供給部110の動作開始のための電流を供給する起動用定電流供給部120とを有し、起動用定電流供給部120からの電流が基準電流供給部100の起動用のアイドリング電流として供給されることでノイズの影響を受けること無く、従来に比して起動時間の短縮が可能となっている。

(もっと読む)

増幅素子

【課題】ECMのインピーダンス変換および増幅に、J−FETを入力としバイポーラトランジスタを出力とする増幅素子に、バックゲート構造のJ−FETを用いると、バックゲート−半導体基板間の容量が、増幅素子の入出力間の寄生容量(ミラー容量)となり、増幅素子の入力ロスが増大する問題に対し有効な半導体装置を提供する。

【解決手段】接地されたp型半導体基板11にp型半導体層12を積層し、p型半導体層12にn型チャネル領域22を有するJ−FETと、n型コレクタ領域33bを有するバイポーラトランジスタを設けた増幅素子とする。これにより、増幅素子の入出力間の寄生容量が発生しなくなるため、ミラー容量による入力ロスの増大を防止できる。また、J−FETのチャネル領域は、エミツタ拡散31と同時に形成できるため、IDSSSや、ピンチオフ電圧が安定し、増幅素子としての消費電流のばらつきが低減し、生産性が向上する。

(もっと読む)

基準電圧回路及びこの基準電圧回路を有する発振回路

【課題】一般的な製造可能であり、且つノイズを低減せさることが可能な基準電圧回路及びこの基準電圧回路を有する発振回路を提供することを目的とする

【解決手段】基準電圧回路200では、出力端子から出力される安定した出力基準電圧VREFを抵抗R11と抵抗R12とから構成される分圧回路211で分圧した電圧によりトランジスタM11のゲート−ソース間電圧VGS11を駆動することで、安定した出力基準電圧VREFを得る。

(もっと読む)

定電圧発生回路およびレギュレータ回路

【課題】オフセット電圧に影響されずに一定電圧を発生する定電圧発生回路を小さな占有面積で実現する。

【解決手段】第1電位と第2電位とを出力する基準電位発生部Q1,Q2,R1-R3と、第1および第2電位を2個の入力とし、第1動作期間に出力が出力線に接続される第1アンプ部と、第1および第2電位を2個の入力とし、第2動作期間に出力が出力線に接続される第2アンプ部と、ローパスフィルタ11と、を備え、第1と第2動作期間を交互に行い、第1アンプ部は、第2動作期間においてオフセット電圧を記憶し、第1動作期間において記憶したオフセット電圧分を相殺して第1電位と第2電位を等しくする出力を行い、第2アンプ部は、第1動作期間においてオフセット電圧を記憶し、第2動作期間において記憶したオフセット電圧分を相殺して第1電位と第2電位を等しくする出力を行う。

(もっと読む)

光受信回路

【課題】光入力信号の周波数特性に正確に対応した光入力のダイナミックレンジの拡大とともに、低電圧動作及び小型化を実現すること。

【解決手段】この光受信回路1は、光信号を受けて該光信号に対応する電流信号Ipdに変換するフォトダイオード2と、電流信号Ipdを電圧信号に変換するトランスインピーダンスアンプ3と、該電圧信号の瞬時状態に対応して電流信号Ipdがトランスインピーダンスアンプ3をバイパスするように動作するFET12とを備えることを特徴とする。

(もっと読む)

改良された指数関数電流発生器と方法

【課題】ImがIbleedより小さいときでさえ、比率が制御信号に指数関数的に関連する電流対を発生させる。

【解決手段】対の比率が制御信号に指数関数的に関係する電流対Ip、Imを発生する装置および方法であって、ここにIpまたはImのいずれかは最小値より大きいかまたは最大値より小さい。装置はImまたはIpの値を感知するために使用される帰還修正回路を含む。感知されたImまたはIpの値が最小値より小さいかまたは最大値より大きいとき、修正回路はブースト電流Iboostを供給する。Iboostは好ましくは所望値およびIpまたはImの差に比例するよう維持される。

(もっと読む)

温度補償回路及び電流源回路

【課題】 簡単な構成で電流源回路を温度補償することができる温度補償回路及び電流源回路を提供する。

【解決手段】 温度補償回路1は、第1トランジスタM1と同チャネル型のMOSFETにて構成した第2トランジスタM2を設けて構成してあり、ゲート電圧生成手段たる第2トランジスタM2のソースは前記第1トランジスタM1のゲートに接続してある。また、温度補償回路1にはスイッチング素子として動作させる第3トランジスタM3が設けてあり、第3トランジスタM3のドレインと第2トランジスタM2のソースとを直列接続してある。

(もっと読む)

バンドギャップ基準電圧回路

【課題】電源電圧の変動に依存することなく、電源電圧変動除去比の良いバンドギャップ基準電圧回路を提供する。

【解決手段】電圧供給回路51によって電源電圧V5は電源電圧Vddの変動に依存しなくなる。すると、抵抗41に発生する正の温度係数を持つ電圧(V3−V2)は、電源電圧Vddでなくて電源電圧V5に基づくので、電源電圧Vddの変動に依存しない。よって、バンドギャップ基準電圧回路の電源電圧変動除去比が良くなる。

(もっと読む)

1 - 20 / 74

[ Back to top ]