Fターム[5J500AK66]の内容

Fターム[5J500AK66]に分類される特許

1 - 20 / 90

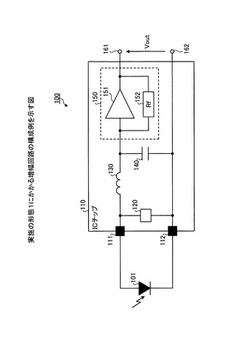

増幅回路および受光回路

【課題】回路の小型化を図ること。

【解決手段】増幅回路100は、パッド111と、TIA150と、オンチップインダクタ130と、シャント容量140と、を1つのチップに備えている。パッド111には電流信号が入力される。TIA150は、入力された電流信号を電圧信号に変換して出力する。オンチップインダクタ130は、パッド111とTIA150との間に直列に接続されている。シャント容量140は、一端がオンチップインダクタ130とTIA150との間に接続され、他端がグランドに接続されている。

(もっと読む)

高周波増幅器

【課題】ユニットセルの組み合わせで形成されるすべてのループ発振を抑制することができる高周波増幅器を提供する。

【解決手段】実施の形態に係る高周波増幅器は、入力された信号を分配する分配回路と、分配回路が分配した信号を増幅するFETセルと、分配回路とFETセルのゲート端子との間に直列に接続され、キャパシタと抵抗との並列回路から構成される安定化回路と、FETセルが増幅した信号を合成する合成回路とを備え、安定化回路をFETセルごとに配置する。

(もっと読む)

無線装置およびその製造方法

【課題】ICチップのプロセスばらつきによって高周波特性がばらついた場合でも、回路特性を最適化できるICチップを基板にフリップチップ実装する無線装置を提供する。

【解決手段】無線装置は、マイクロ波、ミリ波帯の電力増幅器用高周波ICチップ100、バンプ102、入力端子103、出力端子104、基板105、アンダーフィル106、プロセスばらつき検出部110を有する。プロセスばらつき検出部は、プロセスばらつきによる回路特性の変動量をモニタし、モニタされた回路特性の変動量を用いて、算出されたパラーメータを有するアンダーフィル106が、基板105とミリ波帯の電力増幅器用高周波ICチップ100との間に充填されることで、プロセスばらつき及びアンダーフィルの影響があっても、所望の回路特性が得られる無線装置を提供できる。

(もっと読む)

半導体パッケージ、及び半導体パッケージの製造方法

【課題】高周波電力増幅器の汎用性を確保しつつ、低コスト化及び小型化が可能な半導体パッケージ(P)を提供すること。

【解決手段】接地導体(131)と、前記接地導体(131)の上部に設けられた2層の高周波基板(130)と、上層の前記高周波基板(130)を挟むように設けられた一対の導体(134)と、を含む、半導体パッケージ(P)が提供される。また、この半導体パッケージ(P)を含む高周波電力増幅器(100)が提供される。

(もっと読む)

電力増幅回路

【課題】簡単な構成により利得を下げずに効率を向上させることができる電力増幅回路を得る。

【解決手段】基板1上に、熱感応式分配器2、電力増幅素子3a,3b、及び合成器4が設けられている。熱感応式分配器2は、入力信号を最大で2つに分配する。電力増幅素子3a,3bは、分配された入力信号をそれぞれ電力増幅する。合成器4は、電力増幅素子3a,3bの出力信号を1つに合成する。電力増幅素子3a,3bで発生した熱が、基板1を介して熱感応式分配器2に伝わる。熱感応式分配器2は、温度が高くなるほど多くの電力増幅素子3a,3bに入力信号を分配する。

(もっと読む)

ドハティ増幅装置及び通信装置

【課題】ドハティ増幅装置の効率低下を防止する。

【解決手段】ドハティ増幅装置は、メインアンプを構成するメインアンプデバイス1と、ピークアンプを構成するピークアンプデバイス2と、メインアンプデバイス1及びピークアンプ2が実装された基板15とを有している。メインアンプデバイス1は、第1デバイス本体1c、第1入力端子1a、及び、第1出力端子1bを備え、第1入力端子1a及び第1出力端子1bが第1デバイス本体1cを挟んで対向して配置されている。ピークアンプデバイス2は、第2デバイス本体2c、第2入力端子2a、及び、第2出力端子2bを備え、第2入力端子2a及び第2出力端子2bが第2デバイス本体2cを挟んで対向して配置されている。ピークアンプデバイス2は、メインアンプデバイス1の位置に対して、メインアンプデバイス1の第1入力端子から第1出力端子に向かう入出力方向Dsにずれた位置に、実装されている。

(もっと読む)

増幅装置、送信装置

【課題】出力信号の歪みを抑えつつ効率を向上することのできる増幅装置、送信装置を提供する。

【解決手段】実施形態に係る増幅装置は、飽和出力電力が互いに異なる複数の増幅回路を具備している。実施形態に係る増幅装置は、入力端子に入力された入力信号の包絡線信号を検出する検波器と、前記検波器が検出した包絡線信号の信号電圧を、それぞれ異なる参照電圧と比較する複数の比較器と、前記複数の比較器の比較結果に基づいて前記複数の増幅回路のいずれか一つを選択する切替制御部とを具備している。そして、実施形態に係る増幅装置は、前記入力端子を前記切替制御部が選択した増幅回路の入力に接続するとともに、前記切替制御部が選択した増幅回路の出力を出力端子に接続する切替部とを具備することを特徴としている。

(もっと読む)

トランスインピーダンスアンプ、半導体デバイス、および光通信モジュール

【課題】高速、かつ高品質な受信動作が実現可能な、トランスインピーダンスアンプを含んだ光通信モジュールを提供する。

【解決手段】トランスインピーダンスアンプTIAにおいて、単相電流信号を入力として単相電圧信号に変換するプリアンプPRAMPと、プリアンプPRAMPの出力の単相電圧信号の中心電位を検出する閾値検出回路ATCと、プリアンプPRAMPの出力の単相電圧信号を差動化するとともに増幅するポストアンプPSAMPと、プリアンプPRAMPに電源を供給する電源回路PSPYとを有する。特に、電源回路PSPYは、プリアンプPRAMPの入力電圧信号または出力電圧信号でプリアンプPRAMPの電源端子に流れる変化電流とその変化電流と逆相の変化電流とを出力する。これにより、電源電流変化量を相殺する。

(もっと読む)

高周波電力増幅器

【課題】レイアウト面積を増加させることなく、各トランジスタの負荷インピーダンスを均一にすることができる高周波電力増幅器を得る。

【解決手段】半導体チップ2上に、トランジスタ3a,3bと、トランジスタ3a,3bに隣接したコレクタパッド4a,4bとが設けられている。トランジスタ3a,3bとコレクタパッド4a,4bはそれぞれコレクタ配線6a,6bにより接続されている。半導体チップ2外に外部パッド8が設けられている。この外部パッド8に出力端子9が接続されている。コレクタパッド4a,4bと外部パッド8はそれぞれワイヤ10a,10bにより接続されている。コレクタパッド4aは、コレクタパッド4bよりも外部パッド8から遠い位置に配置されている。コレクタパッド4aから出力端子9までの電気長は、コレクタパッド4bから出力端子9までの電気長と同じである。

(もっと読む)

ドライバ集積化回路

【課題】プロセスの耐圧を超える電圧が出力でき、要求される装置性能(高速・高電圧)を満足するドライバ集積化回路の構成を提供する。

【解決手段】差動入力回路と、レベルシフト回路と、出力回路が、同一のプロセスで製造され、基板電位(サブ電位)が異なる、3つ以上のチップに分割配置されており、それぞれのチップの基板印加電圧が異なるように設定することにより、プロセス耐圧よりも大きい出力電圧を提供する。

(もっと読む)

半導体装置

【課題】差分周波数Δfが数百MHzにおいても高周波半導体チップのドレイン端面の電圧が平滑化された半導体装置を提供する。

【解決手段】高周波半導体チップと、高周波半導体チップの入力側に配置された入力側分布回路と、高周波半導体チップの出力側に配置された出力側分布回路と、入力側分布回路に接続された高周波入力端子と、出力側分布回路に接続された高周波出力端子と、高周波半導体チップのドレイン端子電極近傍に配置された平滑化キャパシタとを備え、高周波半導体チップと、入力側分布回路と、出力側分布回路と、平滑化キャパシタとが1つのパッケージに収納されたことを特徴とする半導体装置。

(もっと読む)

C級増幅器

【課題】高効率でかつ広帯域化されたC級増幅器を提供する。

【解決手段】本実施の形態に係るC級増幅器は、電源電圧がVdc、最大電流がImaxの増幅素子の流通角θoがπ(rad)未満において、前記増幅素子の等価回路の従属電流源から見た基本波の負荷インピーダンスをZ1=R1+j・X1、2倍波の負荷インピーダンスをZ2=R2+j・X2とし、X1とR1の関係を−R1≦X1≦R1、R1をR1=Vdc/Imax・π・{1−cos(θo/2)}/{θo/2−sin(θo)/2}、X2/X1をX2/X1=−{θo/2−sin(θo)/2}/{sin(θo/2)−sin(1.5・θo)/3}に、あるいはそれぞれの近傍にする。

(もっと読む)

地上放送波受信用アンテナ装置及びその構成部品

【課題】FM帯以下の周波数帯域において、アンテナ素子長を55[mm]程度まで短縮しても、従来と同等以上の性能を有する地上放送波受信用アンテナ装置を提供する。

【解決手段】アンテナ素子10の受信波のうち当該アンテナ素子10の共振点以下の周波数の受信波を増幅する、受信周波数に対して等価雑音抵抗が2Ω以下となる化合物半導体HEMTとを含んで増幅器12−Aを構成し、雑音指数(NF)をFM帯以下の広い周波数帯域にわたってほぼ一定になるようにした。

(もっと読む)

集積回路および中継基板

【課題】本発明は、マイクロ波帯やミリ波帯において、1つの集積回路で複数の機能を実現する集積回路と、その集積回路が表面実装される中継基板とに関し、特性の劣化の原因となる広帯域設計をすることなく、多様に異なる帯域に柔軟に対応可能とすることを目的とする。

【解決手段】基板上に個別に形成された複数の回路と、前記基板上で前記複数の回路に隔たって形成され、前記複数の回路の何れにも接続され得る特定の回路とを備え、前記特定の回路と前記複数の回路とは、表面実装型の中継基板との突起電極を介する接続に供されるパッドを有する。

(もっと読む)

半導体装置

【課題】携帯電話機などの移動体通信機器に搭載される電力増幅器をバランスアンプから構成する場合に、電力結合器における電力合成の損失を低減することができる技術を提供する。

【解決手段】本実施の形態における技術的思想は、アイソレーション容量素子を、並列接続された対称性の高い2つの容量素子CisoAと容量素子CisoBに分割することにより、容量素子CisoAおよび容量素子CisoBを配線基板の層間容量素子として形成する場合であっても、それぞれの容量素子CisoAと容量素子CisoBに起因する寄生容量をほぼ等しくできる。

(もっと読む)

高周波電力増幅装置

【課題】トークカレントの低減を実現可能な高周波電力増幅装置を提供する。

【解決手段】例えば、出力レベルに応じていずれか一方が活性化されるパワーアンプ回路PA2m,PA2sと、伝送線路LNmn,LNsubを備え、LNmn,LNsubが互いに近接配置された領域を持つ。LNsubの他端(PA2sの出力ノード)は、PA2sが活性化された際、NMOSトランジスタMNswのオンに伴い接地電源電圧GNDとの間に容量C3が接続され、PA2mが活性化された際、MNswのオフに伴い開放状態とされる。PA2sが活性化された際、LNmnとLNsubには同一方向の電流が流れるため、強め合う磁気結合が生じる。一方、PA2mが活性化された際、LNmnに流れる電流と、MNswのオフ容量に伴いLNsubに洩れる電流とは反対方向となり、LNmnとLNsubには弱め合う磁気結合が生じる。

(もっと読む)

半導体装置

【課題】差分周波数Δfが数百MHzにおいても高周波半導体チップのドレイン端面の電圧が平滑化された半導体装置を提供する。

【解決手段】高周波半導体チップと、高周波半導体チップの入力側に配置された入力整合回路と、高周波半導体チップの出力側に配置された出力整合回路と、入力整合回路に接続された高周波入力端子と、出力整合回路に接続された高周波出力端子と、高周波半導体チップに接続される平滑化キャパシタ用端子とを備え、高周波半導体チップと、入力整合回路と、出力整合回路とが1つのパッケージに収納された半導体装置。

(もっと読む)

バイアス回路

【課題】受信雑音性能の低下をともなうことなく簡易な構成により受信用トランジスタを過入力による破壊から防ぐことのできるバイアス回路を得る。

【解決手段】過入力保護回路を有さない受信用増幅器に用いられるバイアス回路であって、受信用増幅器を構成する受信用トランジスタ2のゲート端子に接続されたゲートバイアス回路8と、受信用トランジスタ2のドレイン端子に接続されたドレインバイアス回路9とを備える。ゲートバイアス回路8は、過入力時における受信用トランジスタ2のゲート電流Igまたはゲート電圧Vgの変化を検知して変化信号を生成する変化検知手段を有する。ドレインバイアス回路9は、過入力時の変化信号に応答して、受信用トランジスタ2に対するドレイン電圧Vdを低減させる。

(もっと読む)

高周波回路

【課題】低周波発振と高周波発振とを共に抑制することができる高周波回路を提供する。

【解決手段】高周波回路は、複数のトランジスタ12、複数の入出力整合回路14−1,14−2、複数の抵抗体18、低周波発振抑制回路17を含む。複数のトランジスタは、半導体基板11上に並列に配列形成される。複数の入出力整合回路は、それぞれ第1の絶縁基板13−1上、第2の絶縁基板13−2上に、複数のトランジスタにそれぞれ接続されて設けられている。低周波発振抑制回路は、所望の周波数帯域を透過帯域として有し、並列に配列形成された複数のトランジスタのうち、両側のトランジスタのゲート端子に接続される。複数の抵抗体は、複数の入出力整合回路間のうち、トランジスタに最も近い位置に形成されるとともに、透過帯域の最も低い周波数の発振に対して低周波発振抑制回路を作用させることが可能な長さで、複数の入出力整合回路間に形成される。

(もっと読む)

高周波モジュールおよびその動作方法

【課題】高温通電時にはバイアスジャンプを回避し、実運用時には外部電源を製品によらず共通化し、かつ端子数を削減する。

【解決手段】半導体装置24と、入力整合回路17と、出力整合回路18と、運用時用ゲートバイアス回路70と、運用時用ゲートバイアス回路70に接続された運用時用ゲートバイアス端子41aと、入力整合回路17に接続された高周波入力端子兼高温動作時用ゲートバイアス端子21aと、出力整合回路18に接続されたドレインバイアス回路80と、ドレインバイアス回路80に接続されたドレインバイアス端子41bと、出力整合回路18に接続された高周波出力端子21bとを備え、1つのパッケージに収納された高周波モジュール1およびその動作方法。

(もっと読む)

1 - 20 / 90

[ Back to top ]