Fターム[5J500AS16]の内容

Fターム[5J500AS16]に分類される特許

1 - 20 / 38

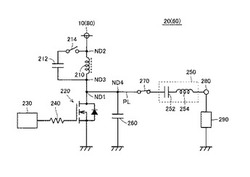

電源装置、非接触送電装置、車両、および非接触電力伝送システム

【課題】E級増幅回路を備える電源装置、非接触送電装置、車両、および非接触電力伝送システムにおいて、E級増幅回路を他の用途で利用可能にする。

【解決手段】チョークコイル210、スイッチング素子220、ゲート駆動装置230、共振回路250、およびキャパシタ260は、スイッチング素子220の零電圧スイッチングを実現するE級増幅回路を構成する。チョークコイル210は、その磁気回路を開閉可能に構成される。チョークコイル210の磁気回路の開放時、スイッチ214,270は、それぞれオン,オフされる。ゲート駆動装置230は、磁気回路の開閉に応じてスイッチング素子220のスイッチング周波数を変更する。

(もっと読む)

半導体装置及びその駆動方法

【課題】2つの電位の誤差を増幅して出力する半導体装置におけるスタンバイ状態からの復帰に際して生じる動作遅延を抑制する。

【解決手段】チャネルが酸化物半導体層に形成されるトランジスタによって、トランスコンダクタンスアンプの出力端子とキャパシタの一方の電極の電気的な接続を制御する。よって、トランスコンダクタンスアンプがスタンバイ状態となる場合であっても、当該トランジスタをオフ状態とすることでキャパシタの一方の電極において長期に渡って電荷の保持を行うことが可能となる。また、トランスコンダクタンスアンプをスタンバイ状態から復帰する際には、当該トランジスタをオン状態とすることで、キャパシタの充放電を早期に収束させることができる。これにより、早期に当該半導体装置の動作を定常状態とすることが可能となる。

(もっと読む)

誤差増幅回路及びスイッチングレギュレータ

【課題】位相補償回路を内蔵する誤差増幅回路と比較して、回路規模及び回路の消費電流を大きくすることなく、位相補償容量を外付けにすることができる誤差増幅回路及び当該誤差増幅回路を用いたスイッチングレギュレータを提供する。

【解決手段】所定の基準電圧Vref1と入力電圧Vfb1との誤差を増幅して出力する誤差増幅器12と、誤差増幅器12にバイアス電流Ibias1を供給する電流生成回路11とを含む集積回路10を備えた誤差増幅回路10aにおいて、集積回路10は、電流生成回路11に接続されたバイアス電流制御端子T1と、位相補償抵抗14を介して誤差増幅器12の出力端子T11に接続された位相補償端子T2とを備え、誤差増幅回路10aは、位相補償端子T2に接続された位相補償容量30を集積回路10の外部に備える。

(もっと読む)

電力変換器のための制御装置

【課題】電力変換器のための制御装置を提供する。

【解決手段】電力変換器のための制御装置は、第1の増幅ステージと、第1の増幅ステージに連結される第2の増幅ステージとを備える。第1の増幅ステージは、電力変換器の出力信号に従ってエネルギー貯蔵素子の第1の端子における第1の増幅された信号を生成する。第2の増幅ステージは、エネルギー貯蔵素子の第2の端子における第2の増幅された信号を生成し、出力信号における変化に応答して、第2の増幅された信号を変化させる。第2の増幅ステージは、更に、第1の増幅された信号に基づいて、第2の増幅された信号の変化を減少させる。

(もっと読む)

パルス幅変調信号生成回路

【課題】回路動作初期やDutyの設定によらずスイッチングノイズの影響を受けない所望するPWM信号を出力されるパルス幅変調信号生成回路を提供する。

【解決手段】波形整形回路4で、三角波生成回路2から出力されたワンパルス信号a、bおよび電圧比較器3から出力されたPWM信号Xに基づいて、該PWM信号Xの立上り直後と立下り直後に生じるチャタリングをマスクする信号f、gを生成する。

(もっと読む)

ミキサー

【課題】各入力チャンネルに入力する信号を結線および面倒な設定を行うことなく簡易に設定できるようにする。

【解決手段】入力チャンネル31−1は、入力パッチ30でパッチされた5つの入力ポートのいずれか1つを選択できるソースセレクタ31a−1を備えている。ソースセレクタ31a−1は、可動接点a1を5つの固定接点b1,c1,d1,e1,f1のいずれかに切り換えることにより、5つの入力ポートのいずれか1つを選択している。他のソースセレクタ31a−Nの構成も、ソースセレクタ31a−1と同様とされており、ソースセレクタ31a−1〜31a−Nによる選択の切り換えは全入力チャンネル31−1〜31−Nにおいて一括して行われる。

(もっと読む)

レベルシフト回路

【課題】バッテリの電源投入時等の電源電圧の急激なオーバーシュートに対する耐性を向上させるレベルシフト回路を提供する。

【解決手段】レベルシフト回路1は、バッテリからの高電圧レベルの入力信号VINを入力するレベルシフト部10と、レベルシフト部10の中間信号Vmを一定以下に制限するクランプ部20と、中間信号をより低電圧のCMOSレベルで出力する出力バッファ部30とを備える。出力バッファ部30の初段においてpMOSトランジスタ31の負荷を抵抗32とすることにより、電源電圧のオーバーシュートに対する耐性を向上させる。

(もっと読む)

半導体装置および電子機器

【課題】パワー半導体素子を駆動するためのドライバを低コストで得ることが可能な半導体装置およびそれを備えた電子機器を提供する。

【解決手段】半導体装置101は、ハイサイド駆動部62からの駆動信号を受ける第1のスイッチング機能部と、ローサイド駆動部64からの駆動信号を受ける制御電極とを有する第2のスイッチング機能部とを備え、ハイサイド駆動部62は、ノーマリーオン型の電界効果トランジスタを含み、スイッチング制御信号の基準電圧を出力ノードの電位へシフトした駆動信号を出力し、第1のスイッチング機能部はノーマリーオン型の第1の電界効果トランジスタTr1を含み、第2のスイッチング機能部はノーマリーオン型の第2の電界効果トランジスタTr2を含み、ハイサイド駆動部62および第1の電界効果トランジスタTr1は第1の半導体チップ71に含まれている。

(もっと読む)

基準信号発生器及びLCDバックライト用PWM制御回路

【課題】周波数が急激に変わる時に起こるピーキング現象を防止して内部素子を保護できる基準信号発生器及びLCDバックライト用PWM制御回路を提供する。

【解決手段】本発明の基準信号発生器は、ロード制御信号SLCによって漸次変化する可変抵抗を提供する抵抗可変部100と、抵抗可変部100の可変抵抗に応じて漸次変化する可変電流の生成を調節する電流調節部200と、漸次変化する可変電流を生成する電流生成部300と、可変電流によって充電電圧が第1基準電圧Vref1に到達するまで充電を制御し、充電電圧が第1基準電圧Vref1に到達すると、放電を開始して第2基準電圧Vref2に到達するまで放電を制御し、初期駆動終了信号または保護信号の入力時に周波数が漸次変化する周波数バッファリング区間を有する三角波形の基準信号を生成する基準信号生成部400とを含むことを特徴とする。

(もっと読む)

電源装置、試験装置、および制御方法

【課題】指定電圧に応じた低ノイズの出力電圧を出力端子から出力する電源装置。

【解決手段】指定電圧に応じた出力電圧を出力端子から出力する電源装置であって、ハイ電位およびロー電位のいずれを出力端子に接続するかをそれぞれ切り替える複数のスイッチと、複数のスイッチのそれぞれがハイ電位を出力するパルス幅を制御して、出力電圧を指定電圧に近付ける多相パルス幅変調部と、指定電圧または出力電圧に応じて、ハイ電位およびロー電位の間の電位差を変更する変更部と、を備える電源装置を提供する。

(もっと読む)

受光回路

【課題】従来の受光回路は、入力のノイズ成分により誤動作を起こす可能性があった。

【解決手段】本発明は、入力光信号に応じて光電流を出力するフォトダイオードと、反転増幅器の入出力間に帰還抵抗を接続し、フォトダイオードのカソードと入力が接続された第1の増幅器と、第1の増幅器と同様な構成を有し、フォトダイオードのアノードと入力が接続された第2の増幅器と、第1の増幅器の出力と第2の増幅器の入力との間に接続される容量素子と、を有する受光回路であって、光電流の電流値に応じて第2の増幅器の入力にバイアス電流を出力して、バイアス電流により第2の増幅器の出力に応じた当該受光回路の出力電圧信を制御し、当該受光回路の感度を調整するバイアス電流制御回路を有し、バイアス電流制御回路は、第2の増幅器の出力に応じて感度を変化させることを特徴とする受光回路である。

(もっと読む)

電力増幅装置

【課題】駆動信号の歪みを抑制防止すると共に、スイッチングロスも低減可能な電力増幅装置を提供する。

【解決手段】出力する駆動信号の基準となる駆動波形信号の振幅値をパルスデューティからなる変調信号にパルス変調し、そのパルス変調された変調信号をデジタル電力増幅回路28で電力増幅し、その電力増幅された電力増幅変調信号を平滑化して駆動信号として出力するにあたり、パルス密度変調回路26による変調信号のパルス幅を調整することにより、パルスデューティ比が50%付近で周波数が高くなるとき、変調信号のパルス幅を所定の時間長さ以上に制御する。具体的には、変調信号のエッジを検出したら、変調を許可する制御信号をオフにする。

(もっと読む)

半導体装置

【課題】レベルシフトを行う場合に、低電圧で動作するトランジスタが使用可能であり、そのトランジスタがオンオフ動作する際の出力変化速度(動作速度)の向上を半導体チップ内の少ない占有面積で容易に実現可能な半導体装置の提供。

【解決手段】レベルシフト部5は、MOSトランジスタN2と、抵抗R2と、抵抗R1とを備え、これらが直列接続されている。抵抗R1には、ツェナーダイオードZD1が並列接続されている。ツェナーダイオードZD1は、MOSトランジスタN2がオフからオンになるときに、レベルシフト部5の出力電圧LOを所定値にクランプする。MOSトランジスタN2のドレインとソースとの間には、ツェナーダイオードZD2が並列接続されている。ツェナーダイオードZD2は、MOSトランジスタN2がオフのときに、MOSトランジスタN2のドレインとソースとの間の電圧を所定値にクランプする。

(もっと読む)

受光アンプ回路

【課題】高速化と高出力化の両立した受光アンプ回路が求められている。

【解決手段】本発明は、受光信号を光電変換し、その光電流に応じて出力トランジスタのオンもしくはオフ状態を制御する受光アンプ回路であって、前記出力トランジスタの制御端子に接続され、前記光電流に応じて、前記出力トランジスタのオンもしくはオフ状態を制御する第1の制御回路と、前記出力トランジスタの制御端子と接地電圧端子との間に接続され、前記出力トランジスタがオフする場合、前記出力トランジスタの制御端子と前記接地電圧端子を導通することで前記出力トランジスタの制御端子の放電を行うスイッチと、を有する受光アンプ回路である。

(もっと読む)

駆動回路

【課題】容量性負荷の駆動電流路の充電時定数又は放電時定数を決定する抵抗器の数を増加させることなく、充電時定数又は放電時定数のばらつきを抑えることができる駆動回路を提供することを目的とする。

【解決手段】複数のプッシュプル構成の出力段に含まれる一対のトランジスタの少なくとも1つに直列にカレントミラー用トランジスタを挿入し、これらのカレントミラー用トランジスタの各々とカレントミラー回路を形成する共通トランジスタを設けて、共通トランジスタを流れるミラー電流値をミラー電流設定回路によって設定する。

(もっと読む)

デジタル−アナログ変換器における電流セル回路

【課題】電流セル回路から検出される電圧を電流に変換し、出力電圧の範囲を広げることで、出力電圧が高くなるにつれて減少する電流量を補償し、一定の出力電圧で電流変化量を最小化できるデジタル−アナログ変換器における電流セル回路を提供する。

【解決手段】電源電圧端に連結されて一定の大きさの電流を生成する電流源と、前記電流源から提供される電流を第1出力端に伝達する第1電流スイッチと、前記第1出力端の出力電圧を検出し、検出された電圧から減少する電流量を生成する第1電流生成部と、前記第1電流生成部から生成された前記電流量を前記第1電流スイッチに供給する第1電流供給部とを含んでデジタル−アナログ変換器における電流セル回路を構成する。

(もっと読む)

差動増幅器

【課題】 負荷側に出力を電流で受け渡すカレントミラー回路を備える差動増幅器の動作を高速化する。

【解決手段】 差動増幅器を構成し、差動増幅器に対する2つの入力の内のそれぞれ1つが与えられる各トランジスタの端子の内で、差動増幅器の出力点となりうるそれぞれの端子の間に接続される回路素子を備える差動増幅器は、カレントミラー回路においてモニタ電流が流れるトランジスタに接続されるとともに、カレントミラー回路においてコピー電流が流れる第1のトランジスタと、前記出力が受け渡される負荷としての抵抗との間に接続される前記2つの入力のうちいずれか1つが与えられるトランジスタへの入力がLの時にオフとなる第2のトランジスタと、第1のトランジスタと第2のトランジスタとの接続点とアースとの間に接続される電流源とをさらに備えることにより、上記課題の解決を図る。

(もっと読む)

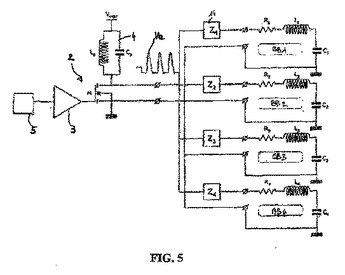

単一の電力段による複数のプラグコイルの制御

本発明は、高周波プラズマ生成装置に関し、本装置は、制御信号(V1)により制御されるスイッチ(M)を含む電源回路(2)であって、当該スイッチが、制御周波数で電源回路の出力に電圧(Vinter)を印加する電源回路(2)と;電源回路の出力に並列に配置された少なくとも2つのプラズマ生成回路(BB1、BB2、BB3、BB4)であって、各々がそれ自体の共振周波数を有し、プラズマ生成回路の共振周波数に相当する周波数で電源回路の出力に高レベルの電圧が印加されるとプラズマを生成することができるプラズマ生成回路と;プラズマ生成回路の共振周波数(F1、F2、F3、F4)に基づいて制御周波数を決定し、使用される制御周波数に従って各回路を選択的に制御する制御装置(5)とを備える。  (もっと読む)

(もっと読む)

光受信回路および光結合装置

【課題】広いダイナミックレンジを有する光受信回路および光結合装置を提供する。

【解決手段】入力光11に応じて電流Ipを出力する受光素子12と、入力端子13aに受光素子12が接続された反転増幅器13と、トランスインピーダンスが低周波数側で小さくなり、且つ高周波数側で大きくなる周波数特性を有し、反転増幅器13の出力電圧Voを入力端子13aに帰還する帰還回路14とを具備する。帰還回路14が、反転増幅器13の入力端子13aと出力端子13bとの間に直列接続された第1抵抗R1および第2抵抗R2と、第1抵抗R1と第2抵抗R2との接続点14aと接地電位線GNDとの間に直列接続された第3抵抗R3およびキャパシタCとを具備する。

(もっと読む)

インバータアンプ

【課題】パワーダウン時のリーク電流が抑制されるインバータアンプの提供。

【解決手段】入力端子とバイアス供給回路との間にパワーダウン時リーク電流抑制用トランジスタを設ける。

(もっと読む)

1 - 20 / 38

[ Back to top ]