Fターム[5J500NM02]の内容

Fターム[5J500NM02]に分類される特許

1 - 20 / 162

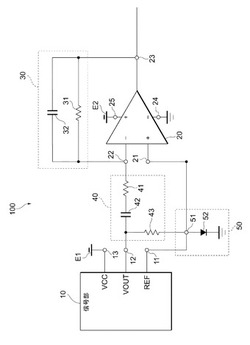

受信回路

【課題】正の単一電源で作動(動作)するオペアンプを用いて負の信号レベルの信号を含む受信信号を増幅することのできる受信回路を提供する。

【解決手段】受信回路100は、基準端子11と基準端子11の電圧を基準とする受信信号を出力する信号端子12とを有する信号部10と、正の入力端子21と負の入力端子22と出力端子23とを有し、正の単一電源E2から電圧が印加されて作動するオペアンプ20と、出力端子23と負の入力端子22との間に接続される第1負荷部30と、信号端子12と負の入力端子22との間に接続される第2負荷部40と、カソード側が接地され、アノード側が基準端子11と正の入力端子21とに接続されるダイオード52を含む基準電圧部50と、を備える。

(もっと読む)

増幅器における可変フィードバック

【課題】線形性の改善されたノイズ指数および低ノイズ増幅器を提供する。

【解決手段】受信信号強度インジケータ201の出力に基づく可変ネガティブフィードバック203を含む増幅器M1が開示されている。フィードバックは、高受信信号レベルについて増加され、低受信信号レベルについて減少されるとしてもよい。実施形態において、可変フィードバック203は、複数の離散的なインピーダンス設定を含むとしてもよい。振幅および/または時間ヒステリシスは、組み込まれていてもよい。

(もっと読む)

定電圧発生回路

【課題】定電圧発生回路の回路面積及び消費電流を削減しながら、負荷の直流的及び過渡的な変化に対する出力電圧の変化を小さくする。

【解決手段】FET4は、電圧源端子に接続されたドレインと出力端子に接続されたソースとを備える。FET2は、FET4のソースに接続されたゲートと、FET4のゲートに接続されたドレインとを有する。FET1は、FET2のソースと接地端子との間に設けられ、ダイオード接続されている。FET3は、電圧源端子とFET2のドレインとの間に接続され、そのドレインとソースとの間に所定の電位差を有し、第1の定電流源として機能する。FET5は、出力端子と接地端子との間に接続される。FET1及びFET5によりカレントミラー回路を構成することにより、FET5は第2の定電流源として機能する。

(もっと読む)

感度温度特性調整回路

【課題】感度温度特性調整回路において、センサの感度温度特性を調整した後にゲインを再調整する必要をなくす。

【解決手段】並列に接続された、複数の異なる温度特性を有する同値抵抗5、6のうち、オペアンプ2の帰還抵抗として用いる同値抵抗を切換スイッチSa、Sbで選択的に切り換えることにより、感度温度特性調整回路1のゲイン温度特性を調整して、センサの感度温度特性を調整するようにした。これにより、センサの感度温度特性を調整した場合でも、この調整回路1内のオペアンプ2の基準温度における入力抵抗値R0と帰還抵抗値Rが変化しないので、基準温度における感度温度特性調整回路1のゲインの値が変化しない。従って、センサの感度温度特性の調整後に、感度温度特性調整回路1のゲインを調整する必要性を減じることができる。

(もっと読む)

トランスインピーダンスアンプ

【課題】利得周波数特性の広帯域化と群遅延平坦特性とを両立させる。

【解決手段】ソース接地トランジスタM1、ゲート接地トランジスタM2、および負荷抵抗RLからカスコード接続回路11を構成し、ソース接地トランジスタM1のドレイン端子とゲート接地トランジスタM2のソース端子と間に第1のインダクタL1を設ける。

(もっと読む)

電圧レギュレータ回路

【課題】複雑な制御を必要とせず、集積回路のトランジスタの閾値電圧バラツキに応じて所望の動作速度に適した電源電圧を提供することができる。

【解決手段】被安定電圧が入力される入力端子1と、安定化された電圧が出力される出力端子2と、入力端子1および出力端子2と電位差を有する一定電圧に設定される共通端子3と、正入力端子および負入力端子を有する差動増幅器4と、差動増幅器4の出力に基づいて入力端子1から出力端子2に流れる電流を制御する電流制御素子5と、出力端子2と共通端子3との間の電位差を分圧し、差動増幅器4の正入力端子に帰還させる分圧回路6と、出力端子2から電力を供給されるが出力端子2の電圧に依存せず、共通端子3の電圧を基準とする当該集積回路のトランジスタの閾値電圧に比例した電圧を差動増幅器4の負入力端子に出力する閾値参照電圧源7とを備える。

(もっと読む)

増幅回路

【課題】 動作が制限されることのない増幅回路を提供する。

【解決手段】 増幅回路1において、初段増幅回路10は、反転入力端子41に入力される入力信号61と、非反転入力端子42に入力される入力信号62とを増幅して初段増幅信号を出力する。第5トランジスタのコレクタ電流は、正電源の電位と第1コレクタ抵抗の抵抗値とに基づいて決定される。第6トランジスタのコレクタ電流は、負電源の電位と第2コレクタ抵抗の抵抗値とに基づいて決定される。このため、従来の差動増幅回路に比べて、第5トランジスタ及び第6トランジスタのコレクタ電流の上限値が大幅に緩和される。第5トランジスタ及び第6トランジスタのコレクタ電流が第1入力信号及び第2入力信号に応じて変化するときに、各コレクタ電流の波形が歪むことを防止できる。

(もっと読む)

電流/電圧変換回路

【課題】低ノイズ電流、多レンジ、高速応答、低回路電源電圧、バイポーラ動作、小規模回路の要件を満足する自動レンジ切り替え可能な電流/電圧変換回路及び集積回路、及びそれらを用いた電子回路基板又は電子機器を得る。

【解決手段】電流入力端子とグランド端子間に入力される入力電流に対し、レンジを複数レンジグループに分けてI/V変換する為に、第1の演算増幅器と各レンジグループ毎のI/V変換部を設け、各I/V変換部毎にI/V変換用演算増幅器を設けてレンジグループ内の自動レンジ切り替えを行なうと同時に、レンジグループ間でも自動レンジ切り替え動作を行なう様にして、全体として低ノイズ電流、多レンジ、高速応答、低回路電源電圧、バイポーラ動作、小規模回路の要件を満足する自動レンジ切り替え可能な電流/電圧変換回路を実現する。

(もっと読む)

演算増幅回路

【課題】 入力電圧の変化による増幅率の変化を抑制した、温度依存性を調整可能な演算増幅器を提供する。

【解決手段】 入力端子及び出力端子と、反転入力端子と非反転入力端子とを有する演算増幅器10と、入力抵抗回路20と、帰還抵抗回路30とを有する演算増幅回路において、入力/帰還抵抗回路は、それぞれ互いに温度係数の異なる抵抗Rとトリミング抵抗TRとを直列接続して形成し、トリミング抵抗を形成するMOSトランジスタはそのソース・ドレイン経路が抵抗Rと演算増幅器の反転入力端子との間に設けられ、その基板電位は演算増幅器の反転入力端子の電位とする。

(もっと読む)

増幅装置及び信号の増幅方法

【課題】増幅装置及び信号の増幅方法を提供する。

【解決手段】増幅装置は、信号入力(31)と、帰還入力(32)と、信号出力(33)とを備えた増幅器(3)を有する。第1の結合路(FB1)は、第1のインピーダンス素子(R1)を備え、帰還入力(32)を信号出力(33)に接続する。第2の結合路(FB2)は、直列に接続したフィルタ装置(4)と、バッファ回路(5)と、第2のインピーダンス素子(R2)を有し、帰還入力(32)を信号出力(33)または信号入力(31)に接続する。

(もっと読む)

D級増幅回路

【課題】入力信号を適切に減衰させるとともに減衰時にも音量を変化させる

【解決手段】増幅部20は、入力端12pおよび12nの各々に互いに逆相で供給される入力信号SpおよびSnに応じてパルス幅変調された出力信号QpおよびQnを生成する。第1減衰部30は、トランジスタTR1と電圧印加回路32とを含む。トランジスタTR1は、入力端12pから増幅部20に至る入力経路16aと入力端12nから増幅部20に至る入力経路16bとの間に介挿される。電圧印加回路32は、入力信号SpおよびSnのレベルが所定値を上回る範囲で増加するほどトランジスタTR1の両端間に流れる電流が増加するように、所定値に対応する制御電圧VCをトランジスタTR1の制御端子に印加する。

(もっと読む)

広帯域増幅器

【課題】RFで動作するシングルエンド出力であるフィードバック型の広帯域増幅器における二次歪み耐性を向上させる。

【解決手段】主増幅MOSトランジスタQ1を含むシングルエンド出力であるフィードバック型の主増幅器310における電圧−電流変換抵抗素子R1と並列に主増幅器310とは逆極性のMOSトランジスタで構成されたバイパス回路320を設け、このバイパス回路320の副増幅MOSトランジスタQ3へのバイアス値を所定値に合わせ込むことによって、主増幅器310に生じる二次歪成分のみに対し逆極性で且つ相似な特性を呈するバイパス作用信号を生成し、該バイパス作用信号で主増幅器310に生じる二次歪成分をバイパス回路320側に引き込むことによって、主増幅器310とバイパス回路320とを含む広帯域増幅器300の二次歪み耐性を向上させる。

(もっと読む)

半導体装置

【課題】電流検出精度が低下することを抑制することができる半導体装置を提供する。

【解決手段】メインTr2のゲート電極およびセンスTrのゲート電極をゲート電圧を印加する共通のゲート端子と接続する。そして、センスTr3にはゲート端子からそのままゲート電位が印加されると共に、メインTr2にはセンスTr3に印加されるゲート電位が第1、第2抵抗31、32によって抵抗分割された電位が印加され、メインTr2のゲート−ソース間電圧と、センスTr3のゲート−ソース間電圧とが等しくなるようにする。

(もっと読む)

電流電圧変換回路

【課題】回路構成を簡素化した電流電圧変換回路を提供することである。

【解決手段】NPNトランジスタQ1のエミッタとPNPトランジスタQ2のエミッタとが入力端子INに接続される。NPNトランジスタQ1のコレクタが定電源V1ラインに接続され、PNPトランジスタQ2のコレクタが電源C2ラインにされる。NPNトランジスタQ1のベースと、PNPトランジスタQ2のベースとの間に、バイアス回路20が接続され、フローティング状態とされる。

(もっと読む)

信号増幅装置、ブリッジ接続型信号増幅装置、信号出力装置、ラッチアップ阻止方法、及びプログラム

【課題】ラッチアップを阻止することができる信号増幅装置、ブリッジ接続型信号増幅装置、信号出力装置、ラッチアップ阻止方法、及びプログラムを提供する。

【解決手段】電源配線VDDに過電流が流れた場合、PMOSトランジスタ12を導通状態にすると共にNMOSトランジスタ14を非導通状態にするように制御してから反転増幅回路102をパワーダウンさせるように制御し、接地配線GNDに過電流が流れた場合、PMOSトランジスタ12を非導通状態にすると共にNMOSトランジスタ14を導通状態にするように制御してから反転増幅回路102をパワーダウンさせるように制御する。

(もっと読む)

高周波差動増幅回路

【課題】安定性が高く、かつ高い利得を有する高周波差動増幅回路を提供する。

【解決手段】本発明の一実施形態としての高周波差増増幅回路は、第1MOSトランジスタ、第2MOSトランジスタ、第1正帰還素子および第2正帰還素子を備える。前記第1MOSトランジスタおよび第2MOSトランジスタは、ソースがそれぞれ第1電源に接続され、ドレインがそれぞれ負荷を介して第2電源に接続され、互いに反転した位相関係にある第1および第2入力信号をゲートで受ける。前記第1正帰還素子は、前記第1MOSトランジスタのゲートと、前記第2MOSトランジスタのドレインとの間に直列接続された第1キャパシタおよび第1可変抵抗を含む。前記第2正帰還素子は、前記第2MOSトランジスタのゲートと、前記第1MOSトランジスタのドレインとの間に直列接続された第2キャパシタおよび第2可変抵抗を含む。

(もっと読む)

広帯域増幅器

【課題】RF(Radio Frequency)で動作する、シングルエンド出力であるフィードバック型の広帯域増幅器において、特に二次歪み耐性に優れたフィードバック型の広帯域増幅器を実現する。

【解決手段】入力信号を電圧−電流変換して出力するMOSトランジスタQ1の出力電流を第1の抵抗素子R1によって出力電圧に変換し、該出力電圧をMOSトランジスタQ1の入力に第2の抵抗素子R2によってフィードバックする。さらに、第1のバイアス回路(VG1+R3)からMOSトランジスタQ1の入力へバイアスを供給する。そして、このバイアス値を、MOSトランジスタQ1のドレイン電流が流れるように、且つ、MOSトランジスタQ1のドレイン電流をゲート電圧で二回微分した成分の絶対値が極小となるように設定する。

(もっと読む)

スイッチドキャパシター回路、検出装置及び電子機器

【課題】負荷電流による電圧ドロップを抑制するスイッチドキャパシター回路、検出装置及び電子機器等を提供すること。

【解決手段】スイッチドキャパシター回路は、出力用の演算増幅器OPBと、スイッチドキャパシター動作を行うための複数のスイッチ素子SB1〜SB8と、スイッチドキャパシター動作を行うための複数のキャパシターCB1,CB2と、スイッチドキャパシター回路の出力端子ノードNTと第1のスイッチ素子SB6との間に設けられる静電保護用の抵抗素子RB1と、を含む。

(もっと読む)

電荷検出回路

【課題】差動アンプの入力側のゲイン調整を容易に行うことができる電荷検出回路を提供する。

【解決手段】電荷発生型センサ及び容量変化型センサの何れかで構成される物理量検出センサ1A,1Bの一端が差動アンプ3の負極入力端子に接続され、他端が前記差動アンプ3の正極入力端子に接続され、前記差動アンプ3の出力端子と前記負極入力端子との間にフィードバック抵抗Rf及びフィードバック容量Cfが並列に接続され、且つ前記差動アンプの正極入力端子と基準電圧との間にキャンセル抵抗Rc及びキャンセル容量Ccが並列に接続された差動型の電荷検出回路であって、前記差動アンプの負極入力端子及び正極入力端子の少なくとも一方に逆バイアス電源7,9によって逆バイアス電位が与えられた可変容量ダイオードD1,D2を接続してゲイン調整を可能とした。

(もっと読む)

位相可変増幅器

【課題】回路規模が小型で低消費電流、出力信号の線形性に優れ、周波数特性が平坦であって、その上低ノイズの位相可変増幅器を提供する。

【解決手段】入力信号の位相を調整する移相部1、位相が調整された後の信号のゲインを増幅するゲイン可変増幅部2によって位相可変増幅器を構成する。そして、移相部1は、全域通過フィルタで構成される可変容量の容量素子103、容量素子103がエミッタとベースとの間に接続され、調整された入力信号の位相に対応する位相電流を生成するトランジスタ101を含み、可変ゲイン増幅部2は、移相電流がテール電流として供給されるトランジスタ108、トランジスタ109を含む差動対、トランジスタ109に流れる電流を電圧に変換する抵抗素子107、トランジスタ108、トランジスタ109に流れる電流を制御する制御信号を出力する制御回路106を含む。

(もっと読む)

1 - 20 / 162

[ Back to top ]