Fターム[5K029AA03]の内容

直流方式デジタル伝送 (8,390) | 目的、効果 (1,587) | 誤動作防止;誤り率の低減 (907) | 波形劣化、符号間干渉対策 (407)

Fターム[5K029AA03]の下位に属するFターム

直流変動、バイアス歪対策 (38)

Fターム[5K029AA03]に分類される特許

361 - 369 / 369

デターミニスティックジッターイコライザ

シリアルデータ通信のためのイコライザは、デターミニスティックジッターの効果を補うために設定できる。イコライザは、負荷サイクルひずみジッターと同様、受信したシリアルデータストリームに、データ依存ジッターの効果を補うために設定できる。イコライザは、以前に受信した一つ以上のシンボルの値を判断し、回復したシンボルと比較するために設定することが出来る。イコライザは、受信データストリームの一部に基づく、データ経路に遅延を取り込むために、シリアルデータ経路に位置する可変遅延器を調整することが出来る。イコライザは、回復したシンボルと、一つ以上の以前に受信したシンボルのいずれかと異なる場合に、遅延を変化するように設定することができ、回復したシンボルと、一つ以上前に受信したシンボルのいずれかと同じ場合に、遅延を一定に維持するように設定することができる。  (もっと読む)

(もっと読む)

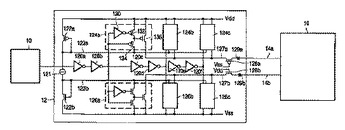

シリアルリンクトランスミッタにおける節電

シリアルリンクトランスミッタにおける節電の局面を説明する。局面は、セグメントのパラレル配列を設けることを含み、各セグメントは、シリアルリンクトランスミッタのプレバッファと出力段回路とを備え、各セグメントは、独立にイネーブルされて、シリアルリンクトランスミッタの信号路における実質的に一定の伝搬遅延を維持しながら、複数の電力レベルと、プリエンファシスの複数のレベルとを実現する。さらなる局面は、セグメントにおける制御可能なアイドル状態を実施するためのプレバッファ段回路におけるバイパス路と、スルーレート制御機能のためのセクション化された部分として、プレバッファ回路における末尾電流および抵抗負荷要素とを設けることを含む。トランスミッタ信号路におけるプリエンファシス遅延回路を有する制御要素を設けて、プリエンファシス遅延回路の最終遅延化ビットの反転を可能にして、プリエンファシスの重みの極性変更を実現することも含まれる。

(もっと読む)

(もっと読む)

選択可能なプリエンファシス信号レベルを有する、DACに基づくラインドライバ

選択可能なプリエンファシスおよびドライバ信号の大きさを有する送信ラインドライバは、1次電流レベルを設定するための1次電流ドライバと、1次電流ドライバによって生成される1次電流レベルに重ね合わされるかまたは加えられる付加的な量の電流を与えるプリエンファシス電流ドライバとを含む。プリエンファシス電流は、プリエンファシス信号論理状態に基づいて、負または正の大きさを有する。第1の電流選択モジュールは、第1のカレントミラーにおける1次電流ドライバ出力信号の大きさを選択するために用いられる基準信号を定め、第2の電流選択モジュールは、第2のカレントミラーにおけるプリエンファシス電流ドライバ信号の大きさを選択する第2の基準信号を定めるために用いられる。論理は第1および第2の電流選択モジュールの両方に対する2値信号を生成することによって、電流レベルおよびプリエンファシス信号を選択する。  (もっと読む)

(もっと読む)

デジタルデータ伝送装置

送信データは送信回路10によって伝送に適した多値のアナログ信号に変換され、増幅器及びハイブリッド回路12を介してケーブル21に出力される。送信回路10では、ケーブル21での波形の劣化を補償する特性の波形を生成する。ケーブル21からの受信信号は、ハイブリッド回路12及び増幅器13を介して、合成器14に入力され、ここで、キャンセル信号生成回路17の出力のキャンセル信号と合成され、不要信号が除去される。その出力信号は、受信回路15において、複数のサンプルホールド回路によってサンプリングされ、歪みを補正するためにマトリクス回路によってアナログ積和演算が行われ、デジタル信号に変換される。デジタル信号は一括して並列直列変換等の処理が行われ、受信データおよび評価信号が得られる。調整制御回路18はCPUを内蔵し、評価信号に基づいてデータを正しく送受信できるように各回路を調整する。 (もっと読む)

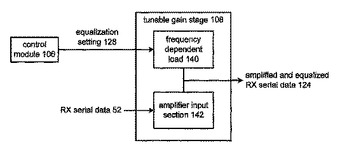

組込型等化を有するアナログフロントエンドおよびその適用

アナログフロントエンドは、制御モジュールおよび可変利得ステージを含む。制御モジュールは、アナログフロントエンドに高速シリアルデータを与えるチャネルのチャンネル応答に基づいて周波数応答設定を与えるために動作可能に結合される。可変利得ステージは周波数依存負荷および増幅器入力部を含む。周波数依存負荷は周波数応答設定に基づいて調整される。増幅器入力部は動作可能に周波数依存負荷に結合され、高速シリアルデータを受取る。増幅器入力部は周波数依存負荷と連動し、増幅され等化されたシリアルデータを生じるために、高速シリアルデータを増幅して等化する。  (もっと読む)

(もっと読む)

複数のシリアルバイトレーンの自動再整列

パラレルデータワード(102)を複数のシリアルデータストリーム(122,124,126,128)へ変換するようになされる送信モジュールを備えるデータ通信装置(100)が説明される。送信モジュールは、複数のグループに配置され、各グループは、データキャリング線(122,124,126,128)を含む。受信モジュール(200)は、送信モジュール(100)から伝えられるデジタルデータを、複数のデータキャリング線(122,124,126,128)を介して集めるようになされる。受信モジュール(200)は、頻度補償コードを検出し、かつ、それに応じて、パラレルワードに戻されるデータを整列し、並びにスキューが原因の再トレーニングシーケンス及び構成シーケンスを軽減するのに使用されるコード検出信号を与える。受信モジュール(200)は、連続的に、グループ間の整列をチェックし、複数のデータグループの整列を自発的に訂正する。  (もっと読む)

(もっと読む)

任意のテスト信号を使用するデジタルデータ信号のテスト

デジタルデータ信号(20)をテストするために、サンプリングポイントにおいてデジタルデータ信号(20)から導出された値(60A)が、分析ユニット(80)内で任意のテスト信号の対応する値と比較される。この比較は、導出された値が任意のテスト信号の対応する値と実質的に一致しない場合はエラーと解釈され(80)、デジタルデータ信号のビットエラーレートが決定される。  (もっと読む)

(もっと読む)

低干渉ラインドライバ

バス通信システムは、通信導電体及びドライバの対を含む。このドライバは、複数の対の被制御型電流源回路を含み、各対は、互いに逆極性の第1及び第2の電流源回路と、各対における電流源により引き寄せられる電流を整合させるための制御回路とを有する。第1の極性の電流源回路は、通信導電体の一方に結合された出力を有し、第2の極性の電流源回路は、通信導電体の他方に結合された出力を有する。遅延線には、各対が、遅延線によって決まるように、連続する対の間の相互遅延をもって連続的にオンに切り換えられるよう、第1及び第2の極性の電流源の制御入力に結合されたタップが設けられる。  (もっと読む)

(もっと読む)

高速信号伝送配線実装構造

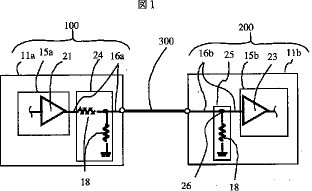

【課題】特に送信側と受信側からなる信号伝送系に関して、送信側半導体装置と受信側半導体装置とを接続する伝送用配線を往復する反射波に起因する信号の時間的揺らぎを抑え、ジッタを低減するための高速信号伝送配線実装構造を提供する。

【解決手段】送信基板100のインピーダンス不整合個所である半導体装置15aの出力回路と出力配線16aとの接続点と、受信基板200のインピーダンス不整合個所である接続点26との間の距離を、信号伝送時間が信号切替周期の半分の時間の整数倍となるように定める。これにより、送信基板100及び受信基板200のそれぞれのインピーダンス不整合個所で反射する信号によるジッタの影響を抑えることができ、その結果高速で信号切替周期の短い信号伝送に耐えうる高速信号伝送配線実装構造を提供できる効果がある。

(もっと読む)

361 - 369 / 369

[ Back to top ]