Fターム[5K029GG05]の内容

直流方式デジタル伝送 (8,390) | 送信部 (677) | 予等化、予歪 (105)

Fターム[5K029GG05]に分類される特許

61 - 80 / 105

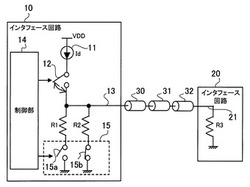

インタフェース回路及び送受信システム

【課題】伝送線路が規格を満たさない場合においても、伝送波形の規格を満足させることが可能なインタフェース回路及び送受信システムを提供する。

【解決手段】フレキシブル配線板のように、インピーダンスの大きな伝送線路がある場合、制御部14は信号送信時に、終端抵抗を信号受信時よりも大きくなるようにする(たとえば、抵抗R1<R2の場合、抵抗R2を選択する)。これにより、初期電圧が大きくなり、伝送波形の規格を満たすことが可能になる。

(もっと読む)

出力バッファ回路、信号伝送インタフェース回路および装置

【課題】プリエンファシス機能を有する出力バッファ回路の、調整可能なプリエンファシス量を調整して、実使用状態の擬似的な伝送損失を実現して、LSI単体または短い配線を接続した状態で、受信回路の性能テストを実施する出力バッファ回路を提供する。

【解決手段】伝送線路に論理信号を送信する出力バッファ回路であって、送信プリエンファシス出力回路3と、送信プリエンファシス量決定回路4を有する。送信プリエンファシス出力回路3は、送信プリエンファシス量決定回路4の出力信号によりプリエンファシス量を制御している。送信プリエンファシス量決定回路4は、擬似損失制御信号により、プリエンファシス量とプリエンファシスタップ数を調整し、送信信号のプリエンファシス量が、低い周波数の信号成分より高い周波数の信号成分ほど信号振幅が小さくなるように制御し、受信波形に信号劣化を与えて擬似的に伝送損失を実現する。

(もっと読む)

プリエンファシス自動調整システム及びその調整方法並びにエンファシス設定信号発生回路

【課題】スルーホールでの減衰に対する最適なエンファシスの付与等を図る。

【解決手段】受信回路16の終端を解除した状態で、送信回路12からステップ信号を信号伝送路14を介して受信回路16へ送信する。その反射信号の信号レベルと第1の参照電圧源18dの第1の参照電圧Vref1とを比較する。反射信号の信号レベルが第1の参照電圧Vref1未満の容量性反射区間内の比較結果に基づいて該容量性反射区間内の区間検出信号を反射波検出回路18eから出力する。

(もっと読む)

シリアル伝送回路

【課題】同一データが連続した場合でもデータの受信を正常に行うことができ、高速なデータ転送と高密度実装および低消費電力化が期待できるシリアル伝送回路を提供する。

【解決手段】シリアル伝送回路において、出力ドライバは、送信するデータの振幅を補正する振幅補正回路11と、送信するデータの変化を検出する検出回路12と、検出回路12による検出の結果、送信するデータに変化がない場合は振幅補正回路11で補正されたデータの振幅を絞る方向に調整する振幅調整回路13などを有する。これにより、送信側の出力ドライバで、送信するデータを検出し、同一データが連続した場合には振幅調整回路13で出力振幅を絞っていき、受信側の入力回路で、波形の浮き上がりを抑止してクロスポイントが消えることがないようにする。

(もっと読む)

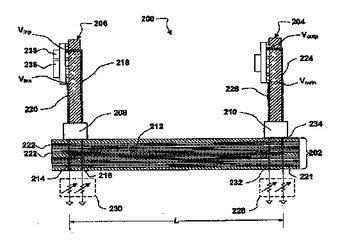

インピーダンス調整回路およびインピーダンス調整方法

【課題】半導体装置と外部抵抗の間の線路に存在する寄生抵抗分を特別の回路を設けることなく補正することのできるインピーダンス調整回路およびインピーダンス調整方法を得ること。

【解決手段】LSIケース201の外部には、ケースピンを介してインピーダンス設定用のクランプ抵抗208と、これと電位を比較するための第1および第2の参照電圧生成抵抗221、222が接続されている。第1および第2の参照電圧生成抵抗221、222の間には、LSI202内の折り返し線225を経由する形で他の線路と同一幅の2本ずつの線路の寄生抵抗分からなる抵抗回路224が設けられており、調整に悪影響となる他の線路の寄生抵抗分をキャンセルする。このため、コンパレータ211の比較結果を使用して制御回路205はインピーダンス調整用出力バッファ203を高精度に調整可能である。

(もっと読む)

ドライバ回路

【課題】複雑な回路構成を必要とすることなく、伝送損失を受けた信号を模擬した模擬信号を可変的に生成し、DUTに内蔵された高域強調回路の正確な試験を実現することができるドライバ回路を提供する。

【解決手段】入力信号に応じて、伝送損失を受けた信号を模擬した模擬信号を出力するドライバ回路10において、入力信号が入力され、入力信号と同一波形の信号を出力信号として出力するメインドライバ18と、入力信号が入力され、入力信号を反転した波形の信号を出力信号として出力するサブドライバ20と、サブドライバ20の出力信号が入力され、サブドライバ20の出力信号の高域を強調した信号を出力信号として出力する高域強調回路22と、メインドライバ18の出力信号と高域強調回路22の出力信号とを加算した模擬信号を出力する加算回路24とを有している。

(もっと読む)

ドライバ回路

【課題】複雑、大規模な回路構成を必要とすることなく簡単な回路構成で、所望の高域強調信号及び低域強調信号を生成することができ、任意の伝送損失を模擬することができるドライバ回路を提供する。

【解決手段】入力信号に応じた波形の出力信号を出力するドライバ回路10において、入力信号が入力され、入力信号と同一波形の信号を出力信号として出力するメインドライバ14と、入力信号が入力され、入力信号と同一波形の非反転信号と、入力信号を反転した波形の反転信号とからなる差動信号を出力するサブドライバ16と、抵抗28、32(34、38)及び可変容量コンデンサ32(38)により構成され、非反転信号を微分した信号を出力し、反転信号を微分した信号を出力する微分回路と、メインドライバ14の出力信号と非反転信号を微分した信号とを加算した高域強調信号又はメインドライバ14の出力信号と反転信号を微分した信号とを加算した低域強調信号を出力信号として出力する加算部26とを有している。

(もっと読む)

伝送エンベロープ検出器のスレショルド電圧調節方法と該方法を利用した装置

【課題】伝送エンベロープ検出器のスレショルド電圧調節方法と該方法を利用した装置を提供する。

【解決手段】伝送エンベロープ検出器(111,131)のスレショルド電圧調節方法が開示される。方法は、シリアル通信が始まった後、最初に入力された入力信号の電圧と伝送エンベロープ検出器(111,131)のスレショルド電圧とを比べて、入力信号の電圧がスレショルド電圧より高い場合、スレショルド電圧を増加させる。

(もっと読む)

高速デジタルデータ伝送装置

【課題】システムLSI1とメモリ2、3間に波形整形回路5、15を配置し、波形整形回路5、15で入力デジタルデータを自動波形整形してその波形歪成分を適確に除去可能な高速デジタルデータ伝送装置を提供する。

【解決手段】システムLSI1と外部接続された1つ以上のメモリ2、3を備え、システムLSI1と1つ以上のメモリ2、3間でデジタルデータを伝送するもので、システムLSI1は、1つ以上のメモリ2、3に接続されたデジタルデータラインに波形整形回路9、15を配置し、波形整形回路9、15は、1つ以上のメモリ2、3から供給されるデジタルデータを微分して微分パルスを形成する微分回路20と、形成した微分パルスとデジタルデータとを重畳処理する歪除去回路手段21からなり、歪除去回路手段21における微分パルスとデジタルデータとの重畳処理は、デジタルデータに微分パルスを重畳し、波形整形によりその波形歪成分の除去処理を行うものである。

(もっと読む)

波形等化係数調整方法および回路、レシーバ回路、ならびに伝送装置

【課題】波形等化係数の調整時間を短縮することが可能な波形等化係数調整技術を提供する。

【解決手段】波形等化係数調整方法において、任意の信号列の場合のみジッタまたは振幅を測定し、波形等化係数を調整する。特に、受信信号の内、010または101信号以外の信号を用いて、符号反転時間を測定する。このような信号を用いた場合の符号反転時間は、従来の技術に比べてより急峻になるため、波形等化係数の調整時間を短縮することができる。

(もっと読む)

シリアル伝送出力装置

【課題】スイッチサイズを小さくするとともに、電源電圧変動を抑制することが可能なシリアル伝送出力装置を提供することを目的とする。

【解決手段】インピーダンス制御電圧を生成するインピーダンス制御電圧生成手段100と、入力される2値のデータと前記インピーダンス制御電圧とに基づいて、インピーダンス制御データを生成するアッテネート手段200と、インピーダンス制御データが入力され、出力インピーダンスを伝送路の特性インピーダンスに整合してデータを出力する出力回路300と、を備え、インピーダンス制御データは、そのハイレベルの電圧値が電源電圧レベルよりも低く、かつ、そのローレベルの電圧値がグランドレベルより高く設定される。

(もっと読む)

信号伝送回路

【課題】複数のレーンを有し、各レーンからの出力振幅が可変する信号伝送回路において、回路規模の増大を抑制し、マージンテストの実施を容易にする。

【解決手段】4つのレーンを有する信号伝送回路100は、定電圧を生成する定電圧回路110と、電流供給回路120と、レーン毎に設けられた差動ドライバ回路130A〜130Dを備える。定電圧回路110は、定電圧回路110からの定電圧を受けて、所定の電圧電流変換率に応じた大きさの電流を4つ生成して並列に出力する。差動ドライバ回路130A〜130Dは、電流供給回路120から出力された電流をそれぞれ受けて、所定の電流電圧変換率に応じた振幅の電圧を出力する。電流供給回路120は、分圧回路115とアナログセレクタ126を備え、それらにより電圧電流変換率を変更可能な電流供給制御回路を構成する。

(もっと読む)

半導体装置の出力回路及びこれを備える半導体装置

【課題】ODTインピーダンスを動的に変更可能な出力回路において、同期回路とデータピンとの間の回路段数を抑制する。

【解決手段】ODT制御信号ODTaを生成するカウンタ回路152,153,162,163と、ODT機能を有する複数のドライバ回路111〜11nと、カウンタ回路からドライバ回路へ伝達される信号を内部クロックDLLに同期させる同期回路180と、ODT制御信号ODTaに基づいて複数のODT選択信号ODTb,ODTcのいずれか一つを活性化させる第1の選択回路170と、活性化されたODT選択信号に基づいて複数のドライバ回路のうち使用するドライバ回路を選択する第2の選択回路180とを備える。第1の選択回路170はカウンタ回路と同期回路との間に配置され、第2の選択回路180は同期回路とドライバ回路との間に配置されている。

(もっと読む)

信号品質最適化装置及び信号品質最適化システム

【課題】高速なシリアル伝送における信号の品質を最適化する装置及びシステムを提供する。

【解決手段】受信部1は、受信データを入力するとともに、前記受信データの補正を指示する調整制御信号を入力した場合には前記調整制御信号に従って前記受信データを補正して出力し、前記調整制御信号を入力しない場合には前記受信データを補正せずに出力するイコライザ11と、

イコライザ11が出力したイコライザ出力データを入力し、入力したイコライザ出力データのBERを計測し、計測したBERの計測結果に基づき前記調整制御信号を生成し、生成した前記調整制御信号をイコライザ11に出力する一連の動作を、イコライザ11から入力するイコライザ出力データのBERが最低になるまで繰り返すBER計測機能部13とを備えた。

(もっと読む)

出力バッファ回路と差動出力バッファ回路並びに伝送方法

【課題】プリエンファシス機能を有する出力バッファ回路の出力インピーダンスを、調整可能なプリエンファシス量とプリエンファシスタップ数、及び動作タイミングに依らず一定で、伝送線路の特性インピーダンスと整合して出力バッファの出力端子で再反射することなく、高速動作可能な出力バッファ回路を提供する。

【解決手段】インバータ1〜3と、一定の時間遅延させる遅延回路1〜3と、バッファ1〜3とを備え、伝送径路に論理信号を送信し、伝送径路の信号減衰量に応じて、送信側で4種以上の信号電圧を有する波形を生成する機能を有する出力バッファ回路で、プリエンファシス量を可変とし、バッファのオン抵抗Rsを一定とする。バッファの前段にセクレタ回路1〜3を有し、インバータは、セレクタ論理によりバッファに入力する信号を選択可能で、データ信号を反転し、セレクタ論理のセレクト信号により、プリエンファシス量とプリエンファシスタップ数を調整する。

(もっと読む)

ドライバ回路装置及びドライバ駆動方法

【課題】ドライバの駆動能力を増大させるとともに波形の乱れを抑制すること。

【解決手段】ドライバ手段30及び入力信号の現在のデータと過去のデータとを比較してドライバを制御するドライバ制御手段20を備えるドライバ回路10であって、ドライバ手段30は複数の並列ドライバを有し、ドライバ制御手段20は、入力信号の現在のデータと1サイクル前のデータとを比較して、異なる場合に複数の並列ドライバを動作させ、ドライバの駆動能力を増大させる。ドライバ制御手段20は、さらに現在のデータを2サイクル前のデータと比較して、同じであるなら複数の並列ドライバの一部を動作させずに、駆動能力の増大の割合を低くすることができる。

(もっと読む)

バックプレーン信号チャネルにおけるインピーダンス整合のための装置及び方法

前面及び裏面を有し、その中で複数の導電層を有し、各導電層は1又はそれ以上の信号チャネルを有するプリント回路基板と、前面から裏面へ延在し、少なくとも1つの信号チャネルへ電気的に結合されるスタブと、スタブ及び接地へ電気的に結合されるインピーダンス整合端子とを有する装置を開示する。前面及び裏面を有し、且つ、1又はそれ以上の信号チャネルを各々有する複数の導電層と、前面から裏面へ延在し、少なくとも1つの信号チャネルへ電気的に結合され、当該プリント回路基板へ取り付けられる部品から信号を受信するよう設計されるスタブとを有するプリント回路基板を設ける段階と、スタブ及び接地へインピーダンス整合端子を結合する段階とを有する処理を開示する。  (もっと読む)

(もっと読む)

タイミングで出力データを初期強化する出力ドライバー及び出力ドライブ方法

【課題】ドライブされる電圧レベルの強化が要求されない出力ドライバー及び出力ドライブ方法の提供。

【解決手段】タイミングで出力データを初期強化する出力ドライバー及び出力ドライブ方法を開示する。本発明の出力ドライバーは、選択信号を発生する選択信号発生部、基準データとして発生する基準データ発生部、及び選択部を備える。前記選択信号は、所定の持続数以上のビット区間の間に同一の論理状態を持続した後に発生する前記入力データの遷移時点で活性化状態である。そして、前記基準データは、前記入力データに対して、前記ビット区間より短い遅延時間だけ遅延する。前記選択部は、前記選択信号に基づいて、前記入力データ及び前記基準データのいずれか一つの論理状態の遷移に応答して前記出力データの論理状態を遷移させるように駆動される。

(もっと読む)

電子回路、該電子回路として構成された差分送信機、及び、自己直列終端送信機を形成する方法(振幅制御、プリ・エンファシス制御及びスルー・レート制御のためのセグメント化と振幅精度及び高電圧保護のための電圧調整とを有する自己直列終端シリアル・リンク送信機)

【課題】本発明は、デュアル・プル・アップ及びプル・ダウン・トランジスタの複数の個々に制御できるセグメントのパラレル構成を有するセグメント化自己直列終端(SSST)送信機の設計を用いて振幅、プリ・エンファシス及びスルー・レートの柔軟な制御を可能にする回路設計方法及び送信機を提供する。本発明は、供給電圧を調整することにより、自己直列終端(SST)送信機の全体にわたって正確な出力を供給/維持する機構をも提供する。

【解決手段】振幅制御、スルー・レート制御及びプリ・エンファシス制御は、様々なセグメントに対する通常入力または反転入力の操作/選択により可能になる。供給電圧の調整は従来のシリアル・リンク受信機ターミネーション電圧との互換性を可能にし、これら電圧が装置への通常の供給よりも大きければ送信機出力装置を保護する。

(もっと読む)

制御システム

【課題】線間の容量及びデバイスの容量により信号波形のレベルの低下及び積分値が低下しても正しく通信を行うことができ、コントローラから1対多の通信で複数のデバイスを制御する場合にも制御線の数を増やす必要がない。

【解決手段】本発明の制御システムは、複数のモジュール2−1、2−2、・・・2−nを同一の状態に制御するためのデバイス1の制御に関する信号を予め設定された閾値に基づいて整形する波形整形ブロックを、複数のモジュール2−1、2−2、・・・2−nのうちのいずれかに設け、波形整形ブロックにより整形されたデバイス1の制御に関する信号を順次次段に送出するものである。

(もっと読む)

61 - 80 / 105

[ Back to top ]