Fターム[5K029GG05]の内容

直流方式デジタル伝送 (8,390) | 送信部 (677) | 予等化、予歪 (105)

Fターム[5K029GG05]に分類される特許

81 - 100 / 105

出力バッファ回路

【課題】

ジッタを低減し、消費電流の低減を図るプリエンファシス機能を備えた出力バッファ回路の提供。

【解決手段】

差動入力対(INT、INB)よりデータ信号を差動入力する第1の差動対トランジスタ(N1、N2)と、差動入力対(EMT、EMB)よりエンファシスデータ信号を差動入力する第2の差動対トランジスタ(N3、N4)を備え、第1、第2の差動対トランジスタのドレインはそれぞれ共通接続され、トランジスタ(P1)を含む出力抵抗回路と、トランジスタ(P2)を含む出力抵抗回路を介して電源(VDD)に接続され、データ信号とエンファシスデータ信号を入力し、プリエンファシス時とそれ以外とで異なる値の出力信号を出力し、該出力信号がトランジスタ(P1、P2)に入力される論理回路(EX-NOR)を備え、プリエンファシス時に、出力抵抗の値を相対的に大とし、デエンファシス時には、出力抵抗の値を相対的に小とする。

(もっと読む)

デエンファシス機能を有する出力バッファ回路

【課題】

プリバッファを含めた回路全体の最適化をはかり、回路素子数を削減すると共に、低消費電力化を可能とする回路の提供。

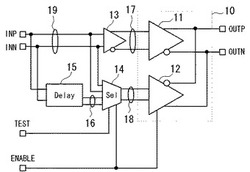

【解決手段】

メインデータ用出力バッファ(13、11)と、デエンファシス用出力バッファ(12)と、デエンファシス設定とデエンファシス非設定を指示する制御信号(SELECT)を入力し、前記制御信号がデエンファシス非設定を示す時には、前記デエンファシス用出力バッファ(12)にメインデータを入力してメインデータ用出力バッファとして動作させ、前記制御信号がデエンファシス設定を示す時には、前記デエンファシス用出力バッファ(12)に、前記メインデータを遅延回路(15)で遅延させたエンファシスデータを入力してデエンファシス用出力バッファとして動作させるように切替制御するセレクタ(14)と、を備えている。

(もっと読む)

出力バッファ回路

【課題】通常動作モードに影響することなく、簡単な構成で振幅マージンテストのモードを搭載することを可能とする回路の提供。

【解決手段】データ信号を入力し出力端子から出力するデータ用の第1の出力バッファ11と、出力端子に出力端が接続された第2の出力バッファ12と、デエンファシス設定とデエンファシス非設定を指示する制御信号ENABLEを入力し、制御信号がデエンファシス非設定を示す時には、第2の出力バッファ12を非活性状態とし、前記制御信号ENABLEがデエンファシス設定を示す時には、第2の出力バッファの入力端に、前記データ信号19を遅延回路15で遅延させたエンファシスデータを入力してデエンファシス用のバッファとして動作させ、テスト制御信号TESTが振幅マージンテストを示すとき、データ信号19を選択して第2の出力バッファの入力端に供給するように切替制御する選択回路14と、を備えている。

(もっと読む)

遅延時間検出方法

【課題】プリディストーション歪補償を行うためのフィードバック信号の遅延時間検出を、経年変化等による大きな遅延時間変化が生じたときでも、オンライン状態のままで効率よく行えるようにする。

【解決手段】粗遅延検出部102による1サンプル単位での粗遅延検出と、微遅延生成器104、遅延器105、106、相関器107、108、加算器109及び遅延検出制御部103による微遅延検出をともにオンラインで行えるようにし、常時は微遅延検出とその検出値による微遅延補正のみを繰り返し実行し、微遅延検出ができないときだけ粗遅延検出を行って粗遅延補正の更新を行う。こうして、大きな遅延時間変化のため粗遅延検出が必要となったとき、粗遅延検出精度は微遅延検出のそれよりも低いので少ない処理時間で検出、補正の更新がオンラインで可能になる。

(もっと読む)

パーシャル・レスポンス伝送システムおよびそのイコライズ回路

【課題】 イコライズ回路における信号振幅の低下を抑制したパーシャル・レスポンス伝送システムを提供する。

【解決手段】 イコライズ回路602は、パーシャル・レスポンス伝送の所望伝達関数による単一ビット応答波形の遷移時間に等しい時間単位でデータ入力を複数段に遅延させた各段のデータを重み付け加算する。これにより、伝送媒体603を含むシステム全体の伝達関数が所望伝達関数に調整される。判別回路606は、送信側から伝送媒体603を介して受信側に送られた信号から、所望伝達関数を考慮した処理によりデータを判別する。

(もっと読む)

プリエンファシス回路

【課題】

消費電流の削減、回路規模の削減、高速動作を可能とするプリエンファシス回路の提供。

【解決手段】

パラレルデータを第1のシリアルデータに変換する第1のパラレルシリアル変換回路1011と、該パラレルデータを第2のシリアルデータに変換する第2のパラレルシリアル変換回路1012と、前記第1及び第2のパラレルシリアル変換回路の第1及び第2のシリアルデータを入力して前記第1のシリアルデータの変化点を強調した信号を出力する混合回路103と、前記第1及び第2のパラレルシリアル変換回路に、互いに相の異なるクロック群よりなる第1のクロック群と、互いに相の異なるクロック群よりなる第2のクロック群をそれぞれ供給するクロック生成回路102とを備え、前記第2のクロック群の第1相のクロックは、前記第1のクロック群の第2相のクロックに対応している。

(もっと読む)

通信システム、相互接続ネットワークケーブル及びネットワーク要素

【課題】ケーブルを伝搬する信号の減衰に起因するシンボル間干渉及び近端クロストークのような様々なタイプの干渉の影響を低減すること。

【解決手段】ネットワークシステムは2以上のネットワーク要素を相互接続する交差接続ケーブル組立部材を含む。交差接続ケーブル組立部材は近端クロストークの影響を低減可能にする。ネットワーク要素は個々のポートについて別々のゲイン調整機能をサポートし、交差接続ポートの実効性を更に増進させる。

(もっと読む)

伝送経路内の損失補償

伝送経路内の損失を補償するための装置は、伝送経路を介して伝送される信号内に時定数を導入する回路ブロックを備える。時定数は、伝送経路内の損失に寄与する固有の時定数の少なくとも一部を相殺する。回路ブロックは、抵抗性回路と、容量性回路とを備える。容量性回路及び抵抗性回路は共に時定数に寄与する。容量性回路は、回路ブロックを介して個々に切り替えることができる複数のコンデンサを備える。上記装置によって与えられる補償の量は、伝送経路内の損失に少なくとも部分的に対応する。  (もっと読む)

(もっと読む)

送信装置

【課題】 コモンモード電位の変動を抑制して高速・長距離の信号伝送をすることができる送信装置を提供する。

【解決手段】 送信装置はメインバッファ回路およびプリエンファシスバッファ回路20を備える。プリエンファシスバッファ回路20は、スイッチ回路21,第1電流源22および第2電流源23を備え、スイッチ回路21により、送信すべきデータのレベルが変化した時刻からの一定期間では、メインバッファ回路10の出力電流と同方向の電流信号を出力する一方、その一定期間が経過した後のレベル一定期間では、出力端子201,202をHigh-Z状態とする。プリエンファシスバッファ回路20の出力は、メインバッファ回路の出力のコモンモード電位に影響を与えず、差動伝送線路へ出力される電流信号の振幅のみに影響を与える。これにより、送信装置はコモンモード電位の変動を抑制して高速・長距離の信号伝送をすることができる。

(もっと読む)

出力バッファ回路

【課題】 ディエンファシスが連続する場合でも消費電力の小さい出力バッファ回路を提供する。

【解決手段】 プレエンファシス機能を有し、分布定数回路として振る舞う伝送線路に論理信号を送出するための出力バッファ回路であって、論理信号に論理値を与える第1の信号を入力して伝送線路を駆動するメインバッファ8と、第1の信号と所定の論理関係を有する第2の信号を入力し、第1のバッファと協働して伝送線路を駆動するプリバッファ9と、論理信号の論理値の変化を検出する手段とを備え、第2のバッファの出力インピーダンスは、伝送線路での信号の減衰量が改善される限度において第1のバッファの出力インピーダンスよりも高く設定されており、ディエンファシス状態が連続する場合には、第2のバッファを第1のバッファと協働させて伝送線路を駆動するようにデータ生成部1で制御信号を生成する。

(もっと読む)

オフチップ高速通信のための電流モードインターフェイス

2つの集積回路(ICまたは“チップ”)の間でデータを転送するためのトランシーバインターフェイスは、従来の電圧モード差動シグナリング技術ではなく、電流モード技術を利用する。送信チップ上のドライバによって送られることになる(ロジック“0”または“1”のような)信号値に基づいて2つの送信ワイヤのうちの1つに電流パルスが注入される。受信チップ中の受信ブロックにおいて、差動電流信号として電流パルスが受け取られる。差動電流信号は電流比較器によって低振幅差動電圧信号に変換される。適切な信号値を出力する演算増幅受信機によって差動電圧信号を検出してもよい。 (もっと読む)

低電圧差動信号の送受信システム

【課題】低電圧差動信号の送受信システムを提供する。

【解決手段】低電圧差動信号の送信回路及び受信回路をそれぞれ備える送受信システムであって、伝送線と接続されて信号を伝達する第1の端子と、第1の端子と接続され、伝送線に信号を伝達するための第1の端子と、第1の端子に信号を伝達するためのソース抵抗と、ソース抵抗に入力電圧と接地との間をスイッチングしてソース抵抗に信号を伝達するスイッチと、スイッチに入力電圧を供給して信号を伝送するための電圧を提供する電圧レギュレーターと、第1の端子の電圧を感知して電圧レギュレーターが受信回路に調整された入力電圧を供給するように制御する電圧制御器と、を含む。これにより、パッケージ抵抗の変化にも受信端の信号レベルには影響を受けないインターフェーシング手段を提供できる。

(もっと読む)

通信装置及びその制御方法

【課題】 プリエンファシスは、信号の立ち上がりや立下りといった高周波成分を増幅するものであるため、放射ノイズが発生したり、電力増幅による消費電力の増大という問題が発生する。

【解決手段】 伝送信号の立下り及び/或は立上がり数を計数するトグルカウンタ302により計数されたカウント値に応じて、伝送信号の立下り及び/或は立上がりを強調する信号処理を行うプリエンファシス回路303により信号処理された信号、或は信号処理されていない信号を、スイッチ304により切り替えて伝送する。

(もっと読む)

伝送線路損失の補償手段を有するドライバ回路

【目的】方形波または三角波を元の波形に加算することにより、任意の伝送線路に対して

損失の補償を行なうことが可能なドライバ回路を提供する。

【構成】信号発生器1と、方形波のパルス幅データ、振幅データを格納するレジスタ2と

、レジスタ2に格納したパルス幅データ、振幅データに従って方形波を生成する方形波発

生器3、方形波発生器4および方形波発生器5と、信号発生器1の出力1aと方形波発生

器3の出力3aと方形波発生器4の出力4aと方形波発生器5の出力5aとを加算する加

算器6と、加算器6の出力6aを増幅する増幅回路7とを有し、方形波パルスを信号波形

に加算することにより伝送線路の損失を補償する。

(もっと読む)

通信方法、通信システム及び通信装置

【課題】 車両に搭載されるDVD読取装置、液晶タッチパネル等の通信装置において、一方の通信装置から他方の通信装置へ送信する信号の振幅を自動的に適切な値に設定して、設定に要する作業量を軽減させる通信方法、通信システム及び通信装置を提供する。

【解決手段】 第1通信装置20は、初期信号パターンを示す初期信号の信号波を第2通信装置30へ送信する処理を開始し、同時にエンファシス強度設定回路209により、初期信号パターンを示す初期信号の信号波の振幅を経時的に変化させる。また第2通信装置30では、第1通信装置20から送信される初期信号パターンの信号波の受信を開始し、誤り率判定回路314にて、受信した初期信号パターンの誤り率を判定し、最も誤り率が低いと判定した振幅に、第1通信装置20へ送信する信号波の振幅を決定する。

(もっと読む)

受信機におけるビット誤りを最小限に抑えるように通信システムや通信方法で使用する選択的スクランブラ

【課題】ビット・シーケンスを送受信するための通信システムとそのビット・シーケンスを転送するための方法を提供する。

【解決手段】送信回路内部には、シフト・レジスタ、イネーブル回路、出力回路を含むスクランブラが存在する。シフト・レジスタはビット・シーケンス内のnビットを一時的に格納し、イネーブル回路はシフト・レジスタが、フレームのペイロード・セクション内だけに出現するビットを格納させる。出力回路は、フィードバックと、n個のステージ内のいくつかのタップを含み、シフト・レジスタから出力されたnビットのシーケンス内の論理値にスクランブルをかけて、ビット・シーケンスがn個の同一論理値を超えるのを有効に防止する。受信回路内部には、シフト・レジスタ、イネーブル回路、出力回路を有するデスクランブラが存在する。デスクランブラはスクランブルがかけられたデータを元の形態に戻す。

(もっと読む)

出力バッファ回路及び半導体装置

【課題】プリエンファシス機能を有し、ジッタを低減する出力バッファ回路の提供。

【解決手段】第1の論理信号を入力して伝送線路(L)を駆動する第1のバッファ回路(M1)と、反転バッファ(T4,T5)と、反転バッファ(T4,T5)と第1の電源(VDD)間に接続され、第1のスイッチ(T3)と、反転バッファ(T4,T5)と第2の電源(VSS)間に接続され、第1のスイッチ(T3)と連動してオン・オフ制御される第2のスイッチ(T6)と、を備えたプリエンファシス制御用の第2のバッファ回路(M2)を備え、第1のバッファ回路(M1)の入力端(AA)と第2のバッファ回路(M2)の反転バッファ(T4,T5)と第1のスイッチ(T3)の接続点(AC)の間、第1のバッファ回路の入力端(AA)と反転バッファと第2のスイッチ(AD)の接続点の間に第1、第2の容量(Z1,Z2)を備える。

(もっと読む)

高速シリアル伝送リンク用の自動適応型等化方法及びシステム

【課題】シリアル・データ通信用の、特に高速シリアル・データ通信用の自動適応型等化方法及びシステムを提供する。

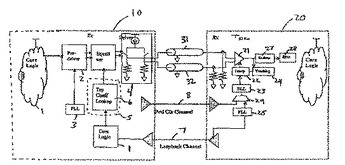

【解決手段】

データ通信システム(900)は、送信機ユニット(100)と、受信機ユニット(200)とを含む。送信機ユニット(100)は、等化情報に従って調整可能な送信特性を有する。送信機ユニット(100)は、所定の信号を送信するように動作可能であり、受信機ユニット(200)は、所定の信号を受信するように動作可能である。受信機ユニット(200)はさらに、受信された信号のアイ開口を検査することによって等化情報を生成し、等化情報を送信機ユニット(100)に送信するように動作可能である。

(もっと読む)

異なる作動電圧範囲及びリセット電圧範囲を有するリピータ回路及びその方法

ワイヤ上の信号遷移を支援する回路及びその方法。第1のサブ回路(15〜22、65)は、回路の出力(34)に結合されている第1のトランジスタ(16)を、立ち上がり遷移の間、ターンオンさせ、出力(34)を高状態に駆動して、該立ち上がり遷移を支援する。第2のサブ回路(24〜30、66)は、回路の出力(34)に結合されている第2のトランジスタ(25)を、立ち下がり遷移の間、ターンオンさせ、出力(34)を低状態に駆動して、該立ち下がり遷移を支援する。第3のサブ回路(61、62)は、第1のサブ回路(15〜22、65)の構成要素をリセットする。該第1のサブ回路は、第1の閾電圧超で作動し、該第3のサブ回路(61、62)は、該第1の閾電圧未満で作動する。第4のサブ回路(63、64)は、第2のサブ回路(24〜30、66)の構成要素をリセットする。該第2のサブ回路は、第2の閾電圧未満で作動し、第4のサブ回路(63、64)は、該第2の閾電圧超で作動する。 (もっと読む)

通信リンクのための2つのタップおよびマルチタップのイコライゼーションを自動的にキャリブレートするシステムおよび方法

リンクにおける測定損失を含むトランスミッタとレシーバとの間のデータリンク上で複数の信号を通信すること、および測定された損失に基づいてトランスミッタのためにマルチタップのイコライゼーション設定を自動的に決定すること、のためにイコライザをキャリブレートする方法。マルチタップのイコライゼーション設定は、複数のリンク損失値のそれぞれの数のための複数のイコライゼーション設定を記憶するルックアップテーブルを用いて決定される。一旦測定されたリンク損失に適合するイコライゼーション設定がテーブル内に見つかると、イコライザは、干渉のシンボル間および他の複数のタイプを低減または除去するために最適にセットされることができる。

(もっと読む)

(もっと読む)

81 - 100 / 105

[ Back to top ]