Fターム[5K047GG45]の内容

デジタル伝送方式における同期 (12,489) | 網同期;クロック、ビット同期 (2,470) | 信号位相の調整 (381) | 同一速度の他のクロックへの乗り換え (309) | 局内基準位相への同期化 (228) | クロック位相同期 (120)

Fターム[5K047GG45]に分類される特許

1 - 20 / 120

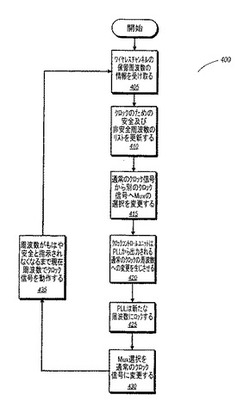

受信器PLL管理を伴う機敏なクロッキング

【課題】干渉を回避するためにクロック信号の周波数を変更する方法及び装置を提供する。

【解決手段】一実施形態において、第1のインターフェイスに搬送されるデータは、第1の周波数のクロック信号に同期される。信号は、別の周波数で第2のインターフェイスに搬送される。第2のインターフェイスに信号が搬送される周波数の変更に応答して、第1のインターフェイスに関連したクロックコントロールユニットが、第2の周波数へのクロック信号の変更を開始する。第2の周波数は、第2のインターフェイスに信号が搬送される周波数との干渉を生じないように選択される。クロック周波数の変更は、インターフェイスのクロックラインにおける擬似的アクティビティを防止するように遂行される。

(もっと読む)

オーバーサンプリング回路及びそれを備えた通信装置

【課題】多相シリアルデータを多相クロックでサンプリングするオーバーサンプリング回路において、遅延量制御動作に伴う消費電流を低減する。

【解決手段】シリアルデータSDATAは、データ遅延部102により多相シリアルデータsdata0〜sdata3とされ、オーバーサンプリング部103において、多相クロックck0〜ck3により、オーバーサンプリングされる。データ遅延部102のデータ遅延素子107の遅延時間は、キャリブレーションデータ発生部101で生成されたデータのオーバーサンプリング出力の位相差をオーバーサンプリング位相検出部105により検出し、その位相差が所望の値となるように、遅延量制御デジタル信号dd_cntを調整する。遅延量制御デジタル信号dd_cntをデジタルアナログ変換部106によりアナログの遅延量発生信号d_cntに変換し、データ遅延素子107に供給する。

(もっと読む)

CDR回路

【課題】前段の光受信装置のスケルチ機能の有無に関係なく汎用的に使用可能なCDR回路を提供する。

【解決手段】CDR回路は、入力データ1に同期した再生クロック2を出力するG−VCO14と、入力データ1の識別再生を再生クロック2に基づいて行うフリップフロップ回路12と、G−VCO14と同一周波数のクロックを出力するサブVCO15と、再生クロック2とサブVCO15の出力クロック4のいずれかを選択する選択回路17と、選択回路17の出力クロック8と参照クロック6とを周波数比較しその周波数差に応じた周波数制御信号5を出力する周波数比較器16とを備える。選択回路17は、少なくとも入力データ1が無信号である期間においてサブVCO15の出力クロック4を選択し、残りの期間において再生クロック2を選択する。

(もっと読む)

判定帰還型等化器を用いた受信機のためのクロック回復回路

【課題】 本発明は、判定帰還型等化器を用いた受信機のためのクロック回復回路を提供する。

【解決手段】 特定の実施形態では、方法は、判定帰還型等化器(DFE)により、送信データを有する第1の信号を受信し、前記DFEにより、前記送信データを有する等化信号に前記第1の信号を調整し、位相誤り検出器により、前記送信データの4分の1のデータ・レート以下のデータ・レートで位相誤りを検出し、前記位相誤り検出器により、前記検出された位相誤りに基づき位相誤りレベルを生成し、前記DFE及び前記位相誤り検出器のためのクロック回復回路により、前記位相誤りレベルに基づき前記送信データに関連するクロック信号を回復する。

(もっと読む)

位相同期装置および位相同期方法

【課題】無線回線を介して接続された装置間の位相同期を行うことが可能な位相同期装置を得ること。

【解決手段】マスタ側無線装置3は、マスタ装置1からの受信パケットから、位相同期の基準となるタイミングを抽出し、基準となるタイミングに同期して、スレーブ側無線装置4へパケットを送信するタイミングを決定し、受信パケットをスレーブ側無線装置4へ送信し、スレーブ側無線装置4は、マスタ側無線装置3からの受信パケットから、位相同期の基準となるタイミングを抽出し、抽出したタイミングと自装置内の動作タイミングとを比較して検出した位相差に基づいて、周波数偏差を検出し、位相差および周波数偏差に基づいて、自装置内の動作クロックの周波数を制御し、基準となるタイミングに同期してスレーブ装置2へパケットを送信するタイミングを決定し、受信パケットをスレーブ装置2へ送信する。

(もっと読む)

位相調整回路、受信装置、および通信システム

【課題】回路構成の複雑化、消費電力の増大を抑止しつつ、複数チャネル間の同期化が可能となり、高速シリアル通信に適用することが可能な位相調整回路、受信装置、および通信システムを提供する。

【解決手段】位相調整回路310は、クロックに応答して所定の位置に同期パターンが挿入されているシリアルデータをパラレルデータに変換するシリアルパラレル変換部313と、シリアルパラレル変換部313によるパラレルデータの同期パターンの位置を検出する同期パターン位置検出部316と、同期パターン位置検出部316で検出された同期パターン位置情報により、同期パターン位置に合わせてパラレルデータおよびクロックの位相を調整する調整部315とを有する。

(もっと読む)

DLLを共用してサンプリング位相設定を行うホストコントローラ

【課題】VDSモード及びFDSモードにて、受信データのサンプリングを行うホストコントローラにおいて、ピン数・消費電力を減らす。

【解決手段】ホストコントローラは、VDSモード及びFDSモードにて、受信データのサンプリングを行うホストコントローラであって、VDS時の位相シフト量を保持するVDS位相レジスタと、FDS時の位相シフト量を保持するFDS位相レジスタと、VDSとFDSのどちらのモードでデータサンプリングを行うかを示すモード設定部と、前記モード設定部の設定値に応じて、前記VDS位相設定レジスタ及びFDS位相設定レジスタの一方に設定されている位相シフト量を選択し、サンプリング位置として提供するサンプリング位置選択部と、前記サンプリング位置設定部から提供されるシフト量に応じて、入力クロック信号の位相をシフトしサンプリングクロックとして提供するクロック位相シフト部とを具備する。

(もっと読む)

サンプリング位相を補正するホストコントローラ及び方法

【課題】 転送データの信頼性向上ならびにエラー対処性能の向上を実現する。

【解決手段】 一実施形態は、外部機器から受信した信号をサンプリングする際のサンプリングクロックの位相シフト補正を行うホストコントローラ10であって、前記サンプリングクロックの位相シフトが必要か判定し、位相シフトが必要な場合は、シフト方向に応じてカウンタ108をアップ/ダウンカウントする位相シフト判定部107と、前記位相シフトの変動範囲制限値を格納する制限値格納部109と、前記カウンタ値が前記位相シフトの制限値を超えているか判定し、超えている場合にエラーの通知を可能とし、超えていない場合に、前記カウンタ108のカウンタ値に応じて、前記サンプリングクロックの位相をシフトするシフト制限判定部110とを具備する。

(もっと読む)

位相同期回路、CDR回路及び受信回路

【課題】基準クロックの周波数を低くして消費電力を抑制することのできる位相同期回路を提供する。

【解決手段】第1の位相比較器と第2の位相比較器とに、それぞれ帰還クロックの少なくとも1周期分異なる位相差をつけた分周クロックを入力して基準クロックとの位相比較を行い、受信信号と帰還クロックとの位相比較の結果で第1と第2の位相比較器の出力の重みづけを行い、重みづけされた出力により帰還クロックの位相調節を行う。

(もっと読む)

通信インタフェース装置及び該通信インタフェースを備えた半導体装置

【課題】複数のレーンを有する通信インタフェースにおいて消費電流の増大を抑制し各レーン間でパラレルクロック信号を同期させる装置の提供。

【解決手段】シリアルクロック線21にシリアルクロック信号が供給され、レーン1はシリアルクロック線からシリアルクロック信号を入力して第1のレーン内に分配し、該シリアルクロック信号サンプリングクロック信号とするカスケード接続されたフリップフロップ(FF)12、13を有し、FF13の出力の反転信号がFF12に帰還入力される分周回路を備え、FF13の出力信号がパラレルクロック信号としてレーン1内に分配され、レーン2ではシリアルクロック信号を入力してレーン内に分配し、レーン1のFF12の出力を受け、レーン2の前記シリアルクロック信号でサンプルするFF13を備え、FF13の出力がパラレルクロック信号としてレーン2内に分配されると共にレーン2のFF12に帰還入力される。

(もっと読む)

ホストコントローラ、情報処理装置、およびサンプリング方法

【課題】 メモリカードからのデータを正しく得ることができ且つデータの転送効率を向上させることができるようにすること。

【解決手段】 実施形態によれば、ライトデータに対して返されるCRCステータスを対象に、位相が異なる複数のクロックに従ってサンプリングを行うことによって複数の値を取得する動作を繰り返す複数のデータ入力手段(25〜27)と、前記複数のデータ入力手段により取得された複数の値の中から、前記CRCステータスの値として正しく取得された値を識別し、データ転送が成功したか否かを示す判定結果を所定のデバイスに通知する制御手段(21)とを具備するホストコントローラが提供される。

(もっと読む)

受信回路及びサンプリングクロック制御方法

【課題】1ユニットインターバルに対するサンプリング数を一定に保つことができる受信回路を提供することを課題とする。

【解決手段】1サイクル内で複数の異なる位相のクロック信号を生成するクロック発生回路(301)と、複数の異なる位相のクロック信号により入力データをオーバーサンプリングするオーバーサンプリング回路(303)と、オーバーサンプリング回路により出力されたデジタルデータの時系列の変化点を検出し、1ユニットインターバルの両端の2個のデータバウンダリを判定するデータバウンダリ判定回路(305)と、判定された2個のデータバウンダリの間の1ユニットインターバルのサンプリング数が閾値より多いときには、隣接する1ユニットインターバルのサンプリング数が一定となるようにクロック発生回路で生成するクロック信号の位相を制御するクロック位相制御回路(306)とを有する受信回路が提供される。

(もっと読む)

クロック乗せ換え回路、及びクロック乗せ換え方法

【課題】データ飛び、および同一データの重複出力を確実に防止しつつ、非同期クロック間で信号波を乗せ換える。

【解決手段】クロック乗せ換え回路は、第1のクロック信号に同期した信号波の値を示す時系列の複数の入力データをタップにて保持し、タップ係数指定手段により指定された複数のタップ係数をタップに保持している該複数の入力データのそれぞれに乗算し、各タップの乗算の結果を加算して得られたデータを出力データとして第2のクロック信号に同期して複数の出力データを出力する複数段のタップと、第1のクロック信号に対する第2のクロック信号の位相遅れを位相差として第2のクロック信号に同期して取得し、第2のクロック信号の該位相差を取得したタイミングにおける信号波の値を前記タップに保持されている入力データに基づいて算出するためのタップ係数を、位相差に応じて第2のクロック信号に同期して指定するタップ係数指定手段と、を有する。

(もっと読む)

受信装置及びゲイン設定方法

【課題】受信特性を向上させることのできる受信装置を提供する。

【解決手段】受信装置は、受信データD1に基づいて抽出クロックCLKを生成するクロックデータリカバリ回路2と、受信データD1のジッタ量に応じて、上記クロックデータリカバリ回路2内のフィルタ回路11のゲインパラメータG1を設定するゲイン設定部3とを有する。

(もっと読む)

動作制御装置、無線受信装置及び動作制御方法

【課題】無線信号を受信して復調する無線受信装置の消費電力を低減するのに好適な動作制御装置、無線受信装置及び動作制御方法を提供する。

【解決手段】無線受信装置1を、アンテナ101と、LNA102と、検波回路103と、LPF104と、アンプ105と、判定部106と、動作制御部107と、ベースバンド処理部108とを含んだ構成とし、動作制御部107を、第1の検波窓信号発生部107aと、判定信号検出部107bと、第2の検波窓信号発生部107cと、同期信号生成部107dと、第3の検波窓信号発生部107eと、同期信号判定部107fと、セレクター107gとを含んだ構成とした。そして、同期信号生成部107dで同期をとっている間に、第2の検波窓信号発生部107cで発生した、予め解っているパルス受信周期に応じた周期の第2の検波窓信号によってLNA102の動作をON−OFF制御する。

(もっと読む)

クロック切り替え回路

【課題】クロック切り替えの時間を短縮すること。

【解決手段】本発明は、光ケーブルを介して入力された光信号から抽出したクロック信号と、自回路内部のクロック源からのクロック信号との切り替えを行うクロック切り替え回路に適用される。本発明のクロック切り替え回路は、光信号からクロック信号を抽出するクロック抽出部と、前記クロック抽出部にて抽出されたクロック信号を、互いに異なる分周数で分周する複数の分周器と、前記複数の分周器にそれぞれ対応して設けられ、対応する分周器にて分周されたクロック信号のクロック周波数が所定のクロック周波数と一致する場合に同期信号を出力する複数の同期検出部と、光ケーブル接続が切断された場合、同期信号を出力した同期検出部に対応する分周器にて分周されたクロック信号から、当該クロック信号と同じクロック周波数成分を持ったクロック源からのクロック信号への切り替えを行うスイッチと、を有する。

(もっと読む)

半導体装置、及びそのテスト方法

【課題】シリアルインタフェース回路におけるCDR回路の位相追従機能を、ループバックテストによって検査する。

【解決手段】本発明による半導体装置において、PLL回路2は、周波数変調された参照クロック1に基づいて、受信用クロック21及び送信用クロック22を生成する。シリアライザ3は、送信用クロック22に応じたタイミングでパラレルデータ33をシリアル化して出力する。CDR回路8は、受信用クロック21に基づいて、受信データ20に対するクロックデータリカバリを実行し、再生データ24を生成する。デシリアライザ14は、再生データ24をパラレル化する。ループバック回線19は、シリアライザ7から出力されたシリアルデータ18を、受信データ20としてCDR回路8に入力する。

(もっと読む)

埋め込みクロック・インターフェースを有する送受信機及び送受信機の動作方法

【課題】埋め込みクロック・インターフェースを有する送受信機及び送受信機の動作方法を提供する。

【解決手段】第1クロック信号に応答し、複数のデータ構成要素を直列データに変換する段階、直列データを送受信する段階、受信された直列データから第2クロック信号を生成する段階、及び第2クロック信号に応答し、直列データを複数のデータ構成要素に変換する段階を含み、直列データに変換する段階は、複数のデータ構成要素の種類についての情報を含む少なくとも1ビットのダミービットを、直列データに所定の間隔で追加する段階を含む送受信機の動作方法である。

(もっと読む)

CDR回路

【課題】MACからの制御信号なしでも瞬時に入力データとの同期を確立し、周波数安定度が高くジッタの少ない再生クロックを生成する。

【解決手段】CDR回路は、入力データ4が遷移したときにパルスを出力するゲーティング回路10と、ゲーティング回路10の出力パルスのタイミングに合うように再生クロック7の位相を調整することにより、入力データ4とタイミングの合った再生クロック7を出力するVCO11と、入力データ4のデータ識別を再生クロック7に基づいて行うフリップフロップ3と、ゲーティング回路10とVCO11との間に設けられた、所望のデータレート周波数の信号を通過させるバンドパスフィルタ40とを備える。

(もっと読む)

クロックデータリカバリ回路、表示装置用データ転送装置及び表示装置用データ転送方法

【課題】回路規模、消費電力が小さく、EMI特性に優れるクロックデータリカバリ回路の提供。

【解決手段】2倍オーバーサンプリングにより、入力データをサンプリングするサンプリング回路SCと、サンプリング回路SCによりサンプリングされた入力データとリカバリクロックとの周波数差を検出する周波数検出回路FDと、サンプリング回路SCによりサンプリングされた入力データとリカバリクロックとの位相差を検出する位相検出回路PDと、少なくとも位相検出回路PDにより検出された位相差に基づいて、サンプリング回路SCに対し、リカバリクロックを出力する電圧制御発振回路VCOと、入力データとして表示データを受信している間、周波数検出回路FDの動作を停止する周波数検出制御回路FDCと、を備えるクロックデータリカバリ回路。

(もっと読む)

1 - 20 / 120

[ Back to top ]