Fターム[5K047MM55]の内容

デジタル伝送方式における同期 (12,489) | 装置、回路、機能 (2,875) | 基本回路、機能 (1,980) | パルス回路 (352) | 分周回路 (83)

Fターム[5K047MM55]に分類される特許

1 - 20 / 83

光受信装置

【課題】連続信号対応の汎用的なCDR回路を備えた制御LSIに、応答特性を損なうことなくシリアルデータ信号を入力する。

【解決手段】光受信装置は、データ信号期間/無信号期間を問わず信号を出力し続けるLA回路6と、LA回路6の出力信号からクロックを抽出しデータを再生するバーストCDR回路2とを備える。バーストCDR回路2は、LA回路6の出力信号とタイミングの合った再生クロックを出力する第1の電圧制御発振器と、第1の電圧制御発振器と同一の周波数で発振する第2の電圧制御発振器と、第2の電圧制御発振器の出力と参照クロックとを周波数比較して、第1、第2の電圧制御発振器を所望のデータレート周波数で発振させる周波数制御信号を出力する周波数比較器と、LA回路6の出力信号の識別再生を再生クロックに基づいて行う識別回路とを有する。

(もっと読む)

CDR回路および受信回路

【課題】参照クロックが不要なインタポレータ方式のCDR回路を小面積で実現することができる技術を提供する。

【解決手段】CDR回路101において、再生クロックのエッジの近傍と遠方にある伝送データのエッジの個数を計測するデータエッジ位置計測回路117と、伝送データのエッジの近傍と遠方にある再生クロックのエッジの個数を計測するクロックエッジ位置計測回路118とを含み、データエッジ位置計測回路117の計測結果とクロックエッジ位置計測回路118の計測結果に応じて、再生クロックの周波数を調整する周波数調整回路116を有する。エッジの近傍と遠方の判定には、CCL回路の最小入力振幅を制御することで実現している。

(もっと読む)

信号処理装置、及び信号処理方法

【課題】簡易な回路構成で入出力クロックの誤差を吸収すること。

【解決手段】所定数のデータと、第1のクロックに同期し、データが有効な区間でアクティブな状態をとる第1のイネーブル信号と、が入力される入力部と、第1のクロックよりも高速な第2のクロックを基準に、第1のイネーブル信号が非アクティブな状態をとる区間のクロック数をカウントするカウント部と、第2のクロックを基準に、所定数に等しいクロック数分だけ第2のイネーブル信号をアクティブな状態にし、カウント部によりカウントされたクロック数分だけ第2のイネーブル信号を非アクティブな状態にするイネーブル信号制御部と、第2のイネーブル信号を出力するイネーブル信号出力部と、第2のイネーブル信号がアクティブな状態をとる区間に、第2のクロックに同期して所定数のデータを出力するデータ出力部と、を備える信号処理装置が提供される。

(もっと読む)

DLLを共用してサンプリング位相設定を行うホストコントローラ

【課題】VDSモード及びFDSモードにて、受信データのサンプリングを行うホストコントローラにおいて、ピン数・消費電力を減らす。

【解決手段】ホストコントローラは、VDSモード及びFDSモードにて、受信データのサンプリングを行うホストコントローラであって、VDS時の位相シフト量を保持するVDS位相レジスタと、FDS時の位相シフト量を保持するFDS位相レジスタと、VDSとFDSのどちらのモードでデータサンプリングを行うかを示すモード設定部と、前記モード設定部の設定値に応じて、前記VDS位相設定レジスタ及びFDS位相設定レジスタの一方に設定されている位相シフト量を選択し、サンプリング位置として提供するサンプリング位置選択部と、前記サンプリング位置設定部から提供されるシフト量に応じて、入力クロック信号の位相をシフトしサンプリングクロックとして提供するクロック位相シフト部とを具備する。

(もっと読む)

送信回路および通信システム

【課題】複数送信レーン間の同期を行うために分配する制御信号のタイミング制約を緩和でき、設計工数を削減することが可能な送信回路および通信システムを提供する。

【解決手段】並列に配置され、供給されるパラレルデータをシリアルデータに変換して出力する複数のレーン部330−0〜330−3と、基準クロックに位相同期した駆動クロックを、イネーブル信号CLKENに応じた駆動クロックの複数サイクル分経過してから複数のレーン部に出力するクロックイネーブラ部320とを有し、複数のレーン部330−0〜330−3の各々は、クロックイネーブラによる駆動クロックを分周して分周クロックおよびロード信号を生成する分周器331−0〜33−3と、分周器による分周クロックおよびロード信号、並びに駆動クロックに同期してパラレルデータをシリアルデータに変換するパラレルシリアル変換器332−0〜332−3と、を含む。

(もっと読む)

CDR回路、受信装置、および通信システム

【課題】簡易な回路構成で、高速かつジッタ入力に強く、信号エラーの発生を抑止することが可能なCDR回路、受信装置、および通信システムを提供する。

【解決手段】CDR回路310は、遅延素子312−1〜312−4を含み、定期的に信号遷移の挿入されたデータ入力をトリガとしてクロックを抽出する分周器320と、分周器で抽出されたクロックに同期して入力データ信号をラッチするラッチ315−1〜315−8とを有する。

(もっと読む)

クロック再生成回路およびこれを用いたデジタルオーディオ再生装置

【課題】従来のビデオ共用オーディオ再生装置では、PLLを用いるためにオーディオクロック品質が劣化してしまうという課題があった。

【解決手段】一定時間入力クロックをカウントするカウンタと、前記カウンタの出力値を元にして基準クロックを分周する可変分周器と、非同期サンプリングレートコンバータを持ち、前記可変分周器のクロック出力を前記非同期サンプリングレートコンバータの入力クロックとして、前記非同期サンプリングレートコンバータの出力を出力とするように構成する。

(もっと読む)

受信回路及びサンプリングクロック制御方法

【課題】1ユニットインターバルに対するサンプリング数を一定に保つことができる受信回路を提供することを課題とする。

【解決手段】1サイクル内で複数の異なる位相のクロック信号を生成するクロック発生回路(301)と、複数の異なる位相のクロック信号により入力データをオーバーサンプリングするオーバーサンプリング回路(303)と、オーバーサンプリング回路により出力されたデジタルデータの時系列の変化点を検出し、1ユニットインターバルの両端の2個のデータバウンダリを判定するデータバウンダリ判定回路(305)と、判定された2個のデータバウンダリの間の1ユニットインターバルのサンプリング数が閾値より多いときには、隣接する1ユニットインターバルのサンプリング数が一定となるようにクロック発生回路で生成するクロック信号の位相を制御するクロック位相制御回路(306)とを有する受信回路が提供される。

(もっと読む)

子局およびPONシステム

【課題】 PONシステムのスループットの低下を防ぎつつ、子局およびPONシステムの低消費電力化が実現できる。

【解決手段】 親局と伝送路を介して接続された子局であって、前記親局から送信される下りデータ信号から抽出したクロックに同期し、該クロックよりも低速なアイドル信号を生成するアイドル信号生成部と、前記クロックと親局に送信する上りデータ信号を同期させる上りデータ信号同期部と、前記上りデータ信号同期部から入力された上りデータ信号の波形を整形し、上りデータ信号が入力されていない場合は、前記アイドル信号が入力され、前記クロックと同期状態を保持する波形整形部とを備える。

(もっと読む)

クロック切り替え回路

【課題】クロック切り替えの時間を短縮すること。

【解決手段】本発明は、光ケーブルを介して入力された光信号から抽出したクロック信号と、自回路内部のクロック源からのクロック信号との切り替えを行うクロック切り替え回路に適用される。本発明のクロック切り替え回路は、光信号からクロック信号を抽出するクロック抽出部と、前記クロック抽出部にて抽出されたクロック信号を、互いに異なる分周数で分周する複数の分周器と、前記複数の分周器にそれぞれ対応して設けられ、対応する分周器にて分周されたクロック信号のクロック周波数が所定のクロック周波数と一致する場合に同期信号を出力する複数の同期検出部と、光ケーブル接続が切断された場合、同期信号を出力した同期検出部に対応する分周器にて分周されたクロック信号から、当該クロック信号と同じクロック周波数成分を持ったクロック源からのクロック信号への切り替えを行うスイッチと、を有する。

(もっと読む)

クロック・データリカバリ回路

【課題】デュアルレートPONシステムにおけるクロック・データリカバリ回路を1つのクロック・データリカバリ回路の構成で実現し、かつ、双方のビットレートのシステムにおける上位層との接続インターフェースを備えたマルチレート対応のクロック・データリカバリ回路を提供する。

【解決手段】入力データのタイミングに合うように位相を調整し、入力データとタイミングのあったクロック信号を出力するクロック出力回路と、クロック信号に基づいて入力データを識別し、入力データを再生した再生データを出力する識別回路と、クロック信号を分配し、第1のクロック信号と第2のクロック信号とを出力する第1の分配器と、第2のクロック信号を入力として、この第2のクロック信号をn(nは整数)分周したn分周クロック信号を出力する第1の分周器とを備える。

(もっと読む)

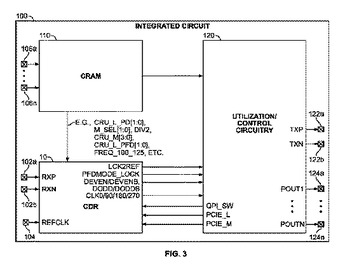

オートスピードネゴシエーションおよび他の可能な特徴を有するクロック・データ再生回路

集積回路(「IC」)は、入力データ信号からデータ情報を再生するためのクロック・データ再生(「CDR」)回路を含んでもよい。CDR回路は、参照クロックループと、データループとを含んでもよい。CDR回路によって出力される時刻変更(再生)データ信号は、その信号に含有される通信変更要求について、IC上の他の制御回路によって監視される。そのような要求に応答して、制御回路は、CDR回路の動作パラメータ(例えば、上述のループのうちのいずれか一方で使用される周波数分割ファクター)を変更することができる。これは、オートスピードネゴシエーションを採用するICサポート通信プロトコルに役立つことができる。  (もっと読む)

(もっと読む)

データ送出装置、データ受信装置、及びデータ送受信システム

【課題】従来のHDMIのオーディオクロック伝送システムでは、サイクルタイムスタンプ値が変動してオーディオクロックの精度が劣化してしまう。

【解決手段】データのサンプルクロックを所定の分周比で分周してクロックを生成するクロック分周手段と、クロック分周手段で生成したクロックをカウントするカウント手段と、カウント生成手段で計測したカウント値を平均化する平均化手段と、平均化手段で取得した平均カウント値のビット数を削減するノイズシェーピング手段と、基本クロック、ノイズシェーピング手段で生成したカウント値及びクロック分周手段で使用した分周比を送出する送出手段を備える。

(もっと読む)

データ転送装置

【課題】複数の回路間のリセットタイミングのずれを小さくし、かつコストを削減する。

【解決手段】クロック生成部100、制御部200、送信部300,400を備えるデータ転送装置において、複数のモジュール内のクロックを同期させるため、複数の送信部の各々において、ビットクロックの連続する立ち上がりエッジを用いてリセット信号を複数回サンプリングすることで、送信部間のリセット信号の位相のずれを低減し、各送信部における分周クロックの位相を揃えることを可能とする。

(もっと読む)

クロックデータリカバリ回路及び表示装置

【課題】クロックデータリカバリにおいて擬似ロック発生の検出に要する時間を短縮すること。

【解決手段】クロックデータリカバリ回路は、レシーバ回路と、PLL回路と、擬似ロック検出回路とを備える。レシーバ回路は、所定のパターンを含むシリアルデータを受け取り、クロック信号に同期してシリアルデータをサンプリングしてサンプルドデータを生成する。PLL回路は、サンプルドデータに基づいてクロックデータリカバリを行い、クロック信号を生成する。ここで、擬似ロックパターンとは、PLL回路の擬似ロックが発生している場合にレシーバ回路が上記所定のパターンをサンプリングする結果得られるパターンである。擬似ロック検出回路は、サンプルドデータに含まれる擬似ロックパターンを検出することによって、PLL回路の擬似ロックを検出する。

(もっと読む)

クロック検出方法及びその装置

【課題】既存のクロック検出方法のリソース占用率が高い問題を解決できるクロック検出方法及びその装置を提供する。

【解決手段】該方法は、プログラマブル部品が、ローカルタイムソースにより生成されたソースクロック信号に周波数分割を行って参照クロック信号を取得し(S101)、プログラマブル部品が、ソースクロック信号をカウント動作クロックとし、検出対象クロック信号の、参照クロック信号の連続するN(Nは正整数である)個のハイ電圧レベルの各ハイ電圧レベル期間における立ち上がりエッジカウント値とハイ電圧レベルカウント値を確定し(S102)、プログラマブル部品が、検出対象クロック信号の、各ハイ電圧レベル期間におけるハイ電圧レベルカウント値と第1の所定値との大きさ関係、及び立ち上がりエッジカウント値と第2の所定値との大きさ関係に基づいて、検出対象クロック信号が有効であるかを確定する(S103)。本発明によると、少ないリソースを占め、クロック検出の信頼性が向上でき、また、検出対象クロック信号の周波数範囲が広くなり、検出対象クロック信号の高周波数グリッチによる影響を避けることができる。

(もっと読む)

ジッタ検出回路およびジッタ検出方法

【課題】

従来のジッタ検出方法は複雑な回路構成でコストが高くなるという問題があった。また、複数のジッタ周波数に対応してアラーム検出を行うことは難しかった。

【解決手段】

本発明のジッタ異常検出回路は、クロック信号のジッタ異常を検出するジッタ異常検出回路において、前記クロック信号を複数の周波数に分周する複数の分周部と、前記クロック信号より周波数の高い高速クロックを発生する高速クロック信号発生部と、前記複数の分周部の出力信号の位相幅を前記高速クロック信号でカウントする複数のカウンタ部と、前記複数のカウンタ部がカウントするカウント値を前記分周部の出力信号の1周期分の時間保持する複数の保持部と、前記複数の保持部に保持された1周期前のカウント値と当該保持部に対応する前記カウンタ部が出力する最新のカウント値との差が予め指定した閾値以上である場合にジッタ異常を検出する検出部とを有することを特徴とする。

(もっと読む)

ネットワーク装置

【課題】イーサネットの同期網をSONET/SDHと同等に構築することのできるネットワーク装置を提供する。

【解決手段】所定の回線種別に対応した複数のインタフェース部と、当該インタフェース部を介して対向装置から受信した信号からクロック品質情報を取得し、品質の最も高いクロックを決定する制御部と、決定されたクロックから網同期に用いるクロックをデジタルPLL回路により生成するクロック処理部とを備えたネットワーク装置であって、前記クロック処理部は、前記制御部により決定されたクロックにつき、該当する前記インタフェース部から受け取る回線抽出クロックの周波数成分を測定し、回線種別を認識する周波数測定部と、認識された回線種別に基づいて前記デジタルPLL回路内のデジタルフィルタの係数を動的に設定するクロック処理制御部とを備える。

(もっと読む)

高周波モジュール

【課題】位相制御誤差を小さくできる高周波モジュールを提供すること。

【解決手段】高速デジタル信号と高速クロックとを入力信号とし、誤りのない信号を出力するように前記デジタル信号に対する前記クロックの位相が移相器により調整された高速ロジック回路を備えた高周波モジュールにおいて、前記デジタル信号とクロックの位相情報は、前記デジタル信号と前記移相器から前記高速ロジック回路に入力されるクロックとの位相差を検出する位相比較器と、この位相比較器の位相差信号に基づき同期検波出力を抽出する同期検波回路を含む位相同期ループを介して、前記移相器に位相制御信号として帰還されることを特徴とするもの。

(もっと読む)

データ転送システム

【課題】互いに異なるクロック周波数に同期して動作する2つの機能回路間でデータを確実に転送することができるデータ転送システムを提供する。

【解決手段】互いに周波数の異なる2つのクロックのエッジが一致するタイミングの直前にデータロード信号を生成し、転送データ受信側の機能回路が当該データロード信号の存在期間内に受信した情報データのみを有効と判定する。

(もっと読む)

1 - 20 / 83

[ Back to top ]