Fターム[5K047MM60]の内容

デジタル伝送方式における同期 (12,489) | 装置、回路、機能 (2,875) | 基本回路、機能 (1,980) | 位相検出回路 (114)

Fターム[5K047MM60]に分類される特許

1 - 20 / 114

クロックデータ再生回路

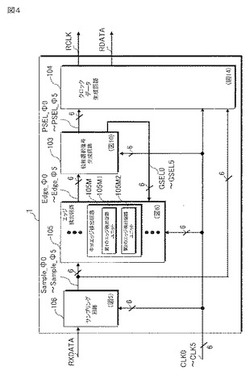

クロックデータリカバリ回路およびそれを内蔵する送受信半導体集積回路

【課題】高いジッタ耐性を有して多相クロックの位相数と消費電力と半導体チップ面積との増大を軽減する。

【解決手段】クロックデータリカバリ回路1のエッジ検出器105の複数のエッジ検出回路105Mの各回路は、第1と第2のエッジ検出回路105M1、2を含む。第1の検出回路105M1は受信データ信号のデータエッジがエッジ検出位相から−1位相よりも進相なことを検出して第1出力信号を生成して、第2の検出回路105M2は受信データ信号のデータエッジがエッジ検出位相から+1位相よりも遅相なことを検出して第2出力信号を生成する。第1または第2の出力信号に応答して、エッジ検出位相が−1位相分または+1位相分変更される。受信データ信号のデータエッジの±1位相の範囲内の存在が検出された場合には、次回のエッジ検出位相は現在の状態に維持される。

(もっと読む)

受信装置、周波数偏差算出方法及びコンピュータプログラム

【課題】異なるタイミングで受信されるリファレンス信号間の相関から推定できる周波数偏差の範囲を拡大する。

【解決手段】受信装置12は、異なる複数の受信間隔で受信されるリファレンス信号に基づいて、複数の受信間隔毎に各受信間隔において生じる受信信号の位相差を推定する処理と、推定された位相差に基づいて、複数の受信間隔毎に複数の位相差候補を決定する候補決定処理と、複数の受信間隔毎に選択される位相差候補同士を組み合わせて形成される位相差候補の複数の組合せの中から、複数の受信間隔における受信信号の位相差を示す組合せを選択する選択処理と、選択された組合せに含まれる位相差候補に基づいて受信信号の周波数偏差を推定する推定処理を実行する制御部17を備える。

(もっと読む)

位相平均化に基づくクロック及びデータ回復の方法、回路及びシステム

【課題】入力データビットストリームとともに伝達される周波数ジッタ及びクロック信号発生器によって生成される周波ジッタを減衰させることができる、位相平均化に基づくクロック及びデータ回復の方法等を提供する。

【解決手段】一実施形態で、方法は、第1のクロック信号の第1の周波数を第1の周波数と基準クロック周波数の基準クロック周波数との間の周波数差に基づき調整するステップ(603)と、第1のクロック信号の第1の周波数及び第1の位相を第1のクロック信号と入力データビットストリームとの間の位相差及び第1の周波数と基準クロック周波数との間の周波数差に基づき更に調整して、第1のクロック信号の第1の周波数及び第1の位相を入力データビットストリームの入力データビット周波数及び入力データビット位相に略固定するステップ(606)とを有する。

(もっと読む)

デューティ補正付き位相調整回路及びシリアライザ

【課題】クロックのばらつきが引き起こすジッタを抑制することが可能なデューティ補正付き位相調整回路及びシリアライザを提供することを目的としている。

【解決手段】正クロック信号及び負クロック信号が入力され前記正クロック信号と前記負クロック信号のデューティ及び位相を調整した正クロック出力信号及び負クロック出力信号を出力する。

(もっと読む)

受信装置

【課題】パターン検出回路の回路規模を削減し、コストダウンすることができる受信装置を提供する。

【解決手段】Mビット長の特定パターンを含むシリアルデータをNビット(N<M)幅のパラレルデータに変換する変換回路と、パラレルデータの、連続するNビットの範囲のそれぞれのビットを先頭とするLビット(N≦L<M)の部分と特定パターンの対応する部分とを比較する比較回路と、比較回路が、連続するNビットの範囲の先頭からKビット目(K=0〜N−1)を先頭とするLビットの部分と特定パターンの先頭からLビットの部分との一致を検出し、さらに、L/Nの商をq、余りをrとして、Nビットの範囲およびK、N、q、rによって決まる特定の周期内に、特定のビットを先頭とするJビット(J≦M−L)の部分と特定パターンのL+1ビット目からJビットの部分との一致を検出する検出回路とを備える。

(もっと読む)

半導体装置、及び情報処理装置

【課題】

安定的な動作を確保できる半導体回路装置、及び情報処理装置を提供することを課題とする。

【解決手段】

半導体装置は、入力信号に遅延を与える遅延部と、前記遅延部から出力される出力信号の位相を検出する位相検出部と、前記位相検出部から出力される位相情報に基づき、前記出力信号の位相の安定動作範囲を設定する設定部と、前記安定動作範囲から位相が外れた前記出力信号の検出回数をカウントするカウンタと、前記遅延部の動作条件又は外的要因に応じて、前記カウンタのカウント数のディスカウント数を表すディスカウント信号を生成するディスカウント制御部と、前記カウンタのカウント数と前記ディスカウント信号が表すディスカウント数とに基づき、前記出力信号の位相のエラーの有無を判定するエラー判定部とを含む。

(もっと読む)

判定帰還型等化器を用いた受信機のためのクロック回復回路

【課題】 本発明は、判定帰還型等化器を用いた受信機のためのクロック回復回路を提供する。

【解決手段】 特定の実施形態では、方法は、判定帰還型等化器(DFE)により、送信データを有する第1の信号を受信し、前記DFEにより、前記送信データを有する等化信号に前記第1の信号を調整し、位相誤り検出器により、前記送信データの4分の1のデータ・レート以下のデータ・レートで位相誤りを検出し、前記位相誤り検出器により、前記検出された位相誤りに基づき位相誤りレベルを生成し、前記DFE及び前記位相誤り検出器のためのクロック回復回路により、前記位相誤りレベルに基づき前記送信データに関連するクロック信号を回復する。

(もっと読む)

CDR回路および受信回路

【課題】参照クロックが不要なインタポレータ方式のCDR回路を小面積で実現することができる技術を提供する。

【解決手段】CDR回路101において、再生クロックのエッジの近傍と遠方にある伝送データのエッジの個数を計測するデータエッジ位置計測回路117と、伝送データのエッジの近傍と遠方にある再生クロックのエッジの個数を計測するクロックエッジ位置計測回路118とを含み、データエッジ位置計測回路117の計測結果とクロックエッジ位置計測回路118の計測結果に応じて、再生クロックの周波数を調整する周波数調整回路116を有する。エッジの近傍と遠方の判定には、CCL回路の最小入力振幅を制御することで実現している。

(もっと読む)

送信装置、送信方法、受信装置、及び受信方法

【課題】マルチパスフェージング環境においても正確な同期タイミングを得ることができる送信装置、送信方法、受信装置、及び受信方法を提供すること。

【解決手段】送信データ列を周波数領域に変換した信号を時間領域信号に変換した信号を送信する送信装置において、第1のプリアンブルパターンの各ビットをn(nは2以上の整数)ビット及びk(kはk≠nである2以上の整数)ビット連続させたビット列を含む第2及び第3のプリアンブルパターンと前記第1のプリアンブルパターンとのうち少なくとも2つのプリアンブルパターンを出力するプリアンブルパターン生成部と、前記プリアンブルパターン生成部から出力された前記少なくとも2つのプリアンブルパターンを含む前記送信信号を送信する送信部とを備える。

(もっと読む)

受信回路、伝送システムおよび受信方法

【課題】多相クロックを使用する伝送システムの受信回路で、受信信号の安定した状態で取り込みを行い、ビットエラーレータを低減する。

【解決手段】所定数の位相の異なる複数のクロックを発生可能で、所定数以下の受信に使用するクロック相数に対応した多相クロックを発生する多相クロック発生回路51と、多相クロックで受信信号を取り込む取込回路25B,25Dと、受信信号と多相クロックの位相差を検出する位相検出回路44A-44Pと、検出した位相差に基づいて、受信信号の取り込みに適した多相クロックの位相調整量を抽出する評価回路56と、抽出した位相調整量に応じて、多相受信クロックの位相を調整する位相調整回路53と、を有する受信回路。

(もっと読む)

光パケットスイッチ装置

【課題】伝送路の帯域利用効率を向上できる光パケットスイッチ装置を提供する。

【解決手段】光パケットスイッチ装置10は、光スイッチ制御部13と、光スイッチ部16とを備える。光スイッチ制御部13は、光電変換部と、CDR部と、シリアル/パラレル変換部と、分周部と、パラレルデータ信号の中からフレーム同期パターンを検出すると共に、パラレルデータ信号の先頭ビットに対して何ビットずれた位置にフレーム同期パターンが格納されているかを示す遅延ビット数を検出する同期パターン検出部と、ヘッダを解析して、光パケット信号の光パケット長および方路情報を検出するヘッダ解析部と、ヘッダ解析部で検出された光パケット長および方路情報と、同期パターン検出部で検出された遅延ビット数情報とに基づいて、競合する光パケット信号の通過/破棄を判定する出力競合判定部34とを備える。

(もっと読む)

同期回路、同期方法、および受信システム

【課題】受信機の個体差や伝送チャネルの時間変動に応じて最適なループゲインを探索できるようにするとともに、伝送フレーム内で複数の変調方式が用いられる場合でも最適なループゲインを探索することができるようにする。

【解決手段】ループゲイン制御部34から初期化フラグを受け取ったPLL制御誤差比較部33は、制御誤差値を算出し、比較器63において、この制御誤差値の大小比較を開始する。制御誤差比較結果に基づいてループフィルタ43−1およびループフィルタ43−2に供給するループゲインを制御する。伝送モード別ゲイン選択部71は、複数の内部のレジスタのうち、伝送モード番号TMに対応するループゲインレジスタG1main[TM]に保持させる値をゲイン制御シーケンサ72から入力される値によって更新する。

(もっと読む)

位相調整回路、受信装置、および通信システム

【課題】回路構成の複雑化、消費電力の増大を抑止しつつ、複数チャネル間の同期化が可能となり、高速シリアル通信に適用することが可能な位相調整回路、受信装置、および通信システムを提供する。

【解決手段】位相調整回路310は、クロックに応答して所定の位置に同期パターンが挿入されているシリアルデータをパラレルデータに変換するシリアルパラレル変換部313と、シリアルパラレル変換部313によるパラレルデータの同期パターンの位置を検出する同期パターン位置検出部316と、同期パターン位置検出部316で検出された同期パターン位置情報により、同期パターン位置に合わせてパラレルデータおよびクロックの位相を調整する調整部315とを有する。

(もっと読む)

受信回路

【課題】 多相クロック信号を用いてデータを受信する受信回路において、多相クロック信号の位相歪みを抑制すること。

【解決手段】 本受信回路30は、位相コードに基づき、多相クロック入力信号から任意の位相の多相クロック出力信号を生成する位相インターポレータ40と、位相コードに変動を与える位相変動回路52と、位相コードの変動に対する多相クロック出力信号の変動を検出する位相検出回路46と、位相検出回路46の検出結果に基づき、位相インターポレータ40の位相歪みを推定する歪み推定回路52と、歪み推定回路52の推定結果に基づき、位相歪みを補正する補正回路52と、を備える。

(もっと読む)

半導体装置

【課題】従来の半導体装置は、送信クロックの周波数が安定するまでに多くの時間を要する問題があった。

【解決手段】本発明の半導体装置は、送信クロックCLKから生成される受信クロックRCLKと入力信号RDと間の位相の進み又は遅れを示す位相差信号を生成し、受信クロックRCLKの位相を入力信号RDの位相に追従させる制御を行う位相追従ループと、受信クロックRCLKの周波数を入力信号RDの周波数に追従させる制御を行う周波数追従ループと、を有し、入力信号RDからデータ信号Sout及びデータ信号に対応する同期クロックSCLKの抽出を行うクロックアンドデータリカバリ回路13と、位相差信号に基づき生成される周波数差信号FPに応じて周波数調整信号Fadjにより示される値を増減させる周波数誤差調整器14と、周波数調整信号Fadjに基づき送信クロックCLKの周波数を増減させる発振器12と、を有する。

(もっと読む)

偏差検出装置及び方法

【課題】伝送フレームのクロックとクライアント信号のクロックとの周波数偏差を高精度かつ高速に検出することが可能な偏差検出装置及び方法を提供すること。

【解決手段】本発明の一態様は、クライアント信号のクロックと伝送フレームのクロックとの周波数偏差を検出する偏差検出装置であって、前記クライアント信号のクロックをカウントする第1カウンタと、前記伝送フレームのクロックに複数の位相差を付与する位相シフタと、前記複数の位相差が付与された伝送フレームの各クロックを並列的にカウントする第2カウンタと、前記第2カウンタから出力される各クロックのカウント値を加算する加算処理部と、前記加算された合計カウント値を前記複数の位相差が付与された伝送フレームの各クロックの個数により平均化し、算出された平均値を前記周波数偏差として出力する平均処理部とを有する偏差検出装置に関する。

(もっと読む)

差動4位相偏移変調の位相補間ベースのクロック及びデータの回復

【課題】方法は、N個の入力ストリームを受け取る工程を含む。

【解決手段】N個の入力ストリームおける入力データ・ビットに基づいて、回復されたクロック信号を生成する工程であって、回復されたクロック信号はクロック周波数及び回復されたクロック位相を有する工程と、回復されたクロック位相に対する個別の位相オフセットにおける個別の位相及びクロック周波数を有する回復されたクロック信号に基づいてN個の入力ストリームのうちの一入力データ・ビットストリームに対するクロック信号を生成する工程と、N個のそれぞれのクロック信号と、N個の入力ビットストリームそれぞれとの間の位相差を検出する工程と、それぞれの位相差をなくすようN個のクロック信号の位相を調節する工程である。

(もっと読む)

データ再生回路、局側光送受信装置及びデータ再生方法

【課題】高速かつ消費電力の低いバーストCDR回路を提供することを目的とする。

【解決手段】複数のクロックを生成する多位相クロック生成手段と、サンプリングデータを出力するサンプリング手段と、データの変化位相を検出する変化位相検出手段と、識別位相を決定する識別位相決定手段と、識別位相のクロックでサンプリングされたデータを選択し再生データを出力するデータ選択手段と、識別位相の変動が収束したかを判定し、収束した場合に収束通知信号を出力する収束判定手段と、その信号に基づいて変化位相検出手段の変化位相検出動作を予め定めた時間の間中止させる検出動作制御手段と、前記時間の間識別位相決定手段に収束位相を保持させる識別位相保持手段とを有し、変化位相検出動作を中止している時間の間は収束位相でサンプリングされたデータを選択して再生データを出力することを特徴とする。

(もっと読む)

ホストコントローラ、情報処理装置、およびサンプリング方法

【課題】 メモリカードからのデータを正しく得ることができ且つデータの転送効率を向上させることができるようにすること。

【解決手段】 実施形態によれば、ライトデータに対して返されるCRCステータスを対象に、位相が異なる複数のクロックに従ってサンプリングを行うことによって複数の値を取得する動作を繰り返す複数のデータ入力手段(25〜27)と、前記複数のデータ入力手段により取得された複数の値の中から、前記CRCステータスの値として正しく取得された値を識別し、データ転送が成功したか否かを示す判定結果を所定のデバイスに通知する制御手段(21)とを具備するホストコントローラが提供される。

(もっと読む)

1 - 20 / 114

[ Back to top ]