Fターム[5M024AA62]の内容

Fターム[5M024AA62]に分類される特許

1 - 20 / 90

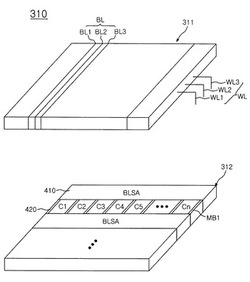

半導体装置

【課題】複数個のメモリチップが積層された構造を有する半導体装置の信頼性を向上させる。

【解決手段】半導体装置は、複数のビットラインと複数のワードラインとの交差点に複数個のメモリセルが配列される複数個のメモリチップが垂直方向に積層され、いずれか一つのメモリチップには複数個のメモリチップの各々に配列された複数のビットラインと連結されアクティブにされるメモリチップのビットラインをイネーブルさせるためのビットラインセンスアンプと、複数個のメモリチップの各々に配列された複数のワードラインと連結されアクティブされるメモリチップのワードラインをイネーブルさせるためのサブワードラインドライバを含み、ビットラインセンスアンプとサブワードラインドライバがいずれか一つのメモリチップに備わる。

(もっと読む)

半導体メモリ装置およびその駆動方法

【課題】容量素子の容量を低減し、また、集積度の高い半導体メモリ装置を提供する。

【解決手段】1つのビット線BL_mに複数個のメモリブロックを接続させる。メモリブロックMB_n_mはサブビット線SBL_n_mと書き込みスイッチと複数のメモリセルを有する。サブビット線SBL_n_mと隣接するサブビット線SBL_n+1_mは2つのインバータと2つの選択スイッチよりなる増幅回路AMP_n/n+1_mに接続し、増幅回路は選択スイッチによりその回路構成を変更できる。また、増幅回路は読み出しスイッチを介してビット線BL_mに接続する。サブビット線SBL_n_mの容量は十分に小さいため、各メモリセルの容量素子の電荷による電位変動を増幅回路AMP_n/n+1_mでエラーなく増幅でき、ビット線BL_mに出力できる。

(もっと読む)

半導体装置

【課題】ダミーマットの占有面積を縮小する。

【解決手段】半導体装置は、ビット線32と、ビット線に接続された複数のメモリセル31と、ダミービット線52と、ダミービット線にソース及びドレインの一方が接続された複数のダミーセルトランジスタ51と、ビット線とダミービット線との間に接続されたセンスアンプ33とを有し、複数のダミーセルトランジスタの各々のソース及びドレインの他方は、フローティング状態にされるか、又はダミービット線に接続されている。

(もっと読む)

半導体記憶装置

【課題】オープンビット線方式における電源ノイズの影響を低減した半導体記憶装置を提供する。

【解決手段】半導体記憶装置は,列方向に両側に延びる一対のビット線に接続するセンスアンプを列方向に直交する行方向に複数配置したセンスアンプ群が列方向に複数配置され,列方向に隣接するセンスアンプ群それぞれに接続される複数のビット線が互いに平行に配置され,列方向の両端に配置されたセンスアンプ群に接続された一対のビット線のうち列方向の両端側の複数のビット線にそれぞれ平行に配置された複数の未使用ビット線を有し,複数のワード線が行方向に配線され,複数のビット線及び複数の未使用ビット線と複数のワード線との交差位置にメモリセルが配置されたメモリセルアレイと,メモリセルアレイの列方向の一端に配置され,複数のセンスアンプ群に内部電源を内部電源線を介して供給する内部電源回路とを有し,未使用ビット線は内部電源配線に接続されている。

(もっと読む)

半導体装置の作製方法

【課題】複数のトランジスタが高集積化された素子の少なくとも一のトランジスタに、作製工程数を増加させることなくバックゲートを設ける半導体装置を提供する。

【解決手段】複数のトランジスタが上下に積層されて設けられた素子において、少なくとも上部のトランジスタ102は、半導体特性を示す金属酸化物により設けられ、下部のトランジスタ100が有するゲート電極層を上部のトランジスタのチャネル形成領域と重畳するように配して、ゲート電極層と同一の層の一部を上部のトランジスタ102のバックゲートBGとして機能させる。下部のトランジスタ100は、絶縁層で覆われた状態で平坦化処理が施され、ゲート電極が露出され、上部のトランジスタ102のソース電極及びドレイン電極となる層に接続されている。

(もっと読む)

半導体装置

【課題】Y方向に隣接する2つの回路ブロックに対しX方向に延在する制御線からタイミング信号を同時に供給する。

【解決手段】例えば、Y方向に配列されたポートPT1,PT2と、ポートPT1,PT2にそれぞれ接続された回路C1,C2と、X方向に延在し回路C1,C2それぞれに含まれるサブ回路SC1,SC2を共通に制御する制御線CTL1を備える。サブ回路SC1,SC2のY方向における中間座標である座標Y1は、ポートPT1,PT2のY方向における中間座標Y0とは異なる。制御線CTL1からサブ回路SC1,SC2へのY方向における距離は互いに等しい。本発明によれば回路C1,C2の動作タイミングを正確に一致させることが可能となる。しかも、複数の制御線を必要とする場合であっても、制御線ごとに対応するサブ回路までの距離を一定とすることが可能となる。

(もっと読む)

半導体記憶装置

【課題】メモリセルアレイと入出力バッファ間の遅延の最大値を抑制し高速に入出力動作が行える半導体記憶装置を提供する。

【解決手段】複数のメモリセルアレイが配置されたメモリセルアレイ部と、外部入出力回路が配置された周辺回路部と、複数のメモリセルアレイと周辺回路部とを接続する内部バス4と、を備え、周辺回路部は、複数の外部入出力バッファ23と、メモリセルアレイとの間で内部バスを並列に入出力するデータと複数の外部入出力バッファを直列に入出力するデータとを相互に変換する複数のバスインターフェース回路24と、を備え、複数のバスインターフェース回路間の距離d1が、複数の外部入出力バッファ間の距離d2及び内部バスの配線幅の最大値d3より狭くなるように、複数のバスインターフェース回路24は、内部バス4と複数の外部入出力バッファとの間にまとめて配置されている。

(もっと読む)

記憶装置及び半導体装置

【課題】データの保持期間を確保しつつ、単位面積あたりの記憶容量を高めることができる記憶装置を提供する。

【解決手段】複数のビット線を幾つかのグループに分割し、複数のワード線も幾つかのグループに分割する。そして、一のグループに属するビット線に接続されたメモリセルには、一のグループに属するワード線が接続されるようにする。さらに、複数のビット線は、複数のビット線駆動回路102a,102b,102cによってグループごとにその駆動が制御されるようにする。加えて、複数のビット線駆動回路102a,102b,102cと、ワード線駆動回路101とを含めた駆動回路上に、セルアレイ103a,103b,103cを形成する。駆動回路とセルアレイ103a,103b,103cが重なるように三次元化することで、ビット線駆動回路が複数設けられていても、記憶装置の占有面積を小さくすることができる。

(もっと読む)

半導体装置

【課題】回路規模が小さい階層型DRAMを提供すること。

【解決手段】それぞれが複数のメモリセルと、前記メモリセルに接続されたビット線と、前記ビット線をプリチャージするプリチャージ回路とを有し、行方向及び列方向にマトリクス状に配置された複数のサブアレイと、前記列方向に沿って延設され、前記サブアレイの列を選択するための列選択信号線と、前記行方向に沿って延設され、前記サブアレイの行を選択するためのメインワード線と、前記プリチャージ回路に対してプリチャージ信号を供給するプリチャージ信号線と、を備え、前記行方向または前記列方向に並べて配置された少なくとも2つの前記サブアレイが前記プリチャージ信号に応じて同一論理で制御される半導体装置。

(もっと読む)

半導体装置

【課題】半導体装置のアンプ領域は、回路素子のサイズよりも各種の配線のための領域が広い状態となっており、半導体装置のチップサイズを削減する際の妨げになっている。そのため、アンプ領域を縮小し、チップサイズの削減を実現する半導体装置が、望まれる。

【解決手段】半導体装置は、其々に対応するデータを保持する複数のメモリセル、及び、複数のメモリセルのデータを第1の電圧に基づいて其々増幅する複数のセンスアンプ、を含む第1の領域と、第1の電圧を第2の電圧に基づいて発生する第1の電源生成回路を含み、第1の領域の一辺に沿って設けられた第2の領域と、を備えている。さらに、第2の電圧は、第1の領域上を、第1の領域の一辺に平行な第1の方向に延在する第1の電源配線を経由して第1の電源生成回路に供給される。

(もっと読む)

半導体集積回路装置

【課題】同じ拡散層に形成されて対照的な動作を行うトランジスタは、拡散層に対して対照的に配置されるのが一般的である。この固定観念を捨てることで、半導体集積回路装置の設計に係る制約の一部を回避し、サイズダウンおよび製造コストの節約を可能とするレイアウトを用いた半導体集積回路装置を提供する。

【解決手段】本発明によれば、同じ拡散層に形成されて対照的な動作を行う2つのトランジスタを、あえて非対称的に配置することで、半導体集積回路装置のさらなるサイズダウンが可能となる。

(もっと読む)

半導体記憶装置

【課題】半導体集積回路の面積を節約するために、複数の拡散層を共有化すると、それらの拡散層に接続された配線に対する寄生容量が変化する。それでも、複数の拡散層に接続された対となる配線のそれぞれにおける容量負荷のバランスが保たれる半導体レイアウトを提供する。

【解決手段】対となる配線のそれぞれが接続される拡散層を交互または互い違いに配置することで、対となる配線のそれぞれにおける容量負荷の総量のバランスを保つ。

(もっと読む)

ローカル列デコーダに関連付けられた互い違いに配置されたセンスアンプを有する半導体メモリ

【課題】本発明は、少ししか列アドレスバスを必要としない半導体メモリを提供する。

【解決手段】本発明は、半導体メモリであって、ビット線と、メモリセルアレイと、少なくとも1組のセンスアンプバンクであって、各センスアンプは、交互の配列により、対応するビット線に接続されていることによって、ビット線と平行な各センスアンプバンクの組で利用可能なスペースに相互接続することを備え、各センスアンプバンクは、センスアンプバンクの少なくとも1つのセンスアンプを選択する、少なくとも1つのローカル列デコーダを備え、前記ローカル列デコーダは、ビット線と平行な利用可能な相互接続スペース内に走っている出力線によってセンスアンプバンクの少なくとも1つのセンスアンプと電気的に結合されたことを特徴とする半導体メモリに関するものである。

(もっと読む)

半導体装置

【課題】配線層の空きスペースを利用して電源補償容量を形成する。

【解決手段】Y方向に配列された複数のメモリマットMATと、Y方向に隣接するメモリマットMAT間にそれぞれ配置されたセンス領域SAと、カラム選択信号を生成するカラムデコーダ13と、複数のメモリマットMAT上をY方向に延在し、カラム選択信号をカラムデコーダ13から複数のセンス領域SAに供給するカラム選択線YSと、カラムデコーダ13からみて最も遠いメモリマットMATa上に設けられた電源補償容量30とを備える。電源補償容量30は、容量電極として機能する電源配線VL1,VL2を含み、その少なくとも一方がカラム選択線YSと同じ配線層に形成されている。本発明によれば、カラム選択線YSを形成する必要のないメモリマットMATa上に電源補償容量30を設けていることから、チップ面積を縮小することが可能となる。

(もっと読む)

半導体メモリ装置

【課題】DRAMに必要なキャパシタの容量を低減し、高度に集積化したDRAMを提供する。

【解決手段】分割ビット線型DRAMにおいて、サブビット線をワード線の下に形成し、ビット線をワード線の上に形成する。分割ビット方式でサブビット線の寄生容量が低減し、かつ、セルトランジスタのオフ抵抗を必要に応じて高いものとすることによって、キャパシタの容量を通常のDRAMの1/10以下とすることができる。このため、スタック型キャパシタであっても、その高さを従来のものの1/10以下とできるので、その上にビット線を設けることも容易となる。また、セルトランジスタの構造を特殊なものとすることでメモリセルあたりの面積を4F2とできる。

(もっと読む)

半導体装置及びその制御方法

【課題】ビット線構成が階層化されたメモリセルアレイのプリチャージ動作時に配線レイアウトに起因するプリチャージ速度の低下を防止可能な半導体装置を提供する。

【解決手段】本発明の半導体装置は、ローカルビット線LBLとグローバルビット線GBLとに階層化され、階層スイッチLSWによりローカルビット線LBLとグローバルビット線GBLとの間の電気的接続が制御され、プリチャージ回路LPCによりプリチャージ電圧がローカルビット線LBLに供給される。プリチャージ動作時には、階層スイッチLSWが導通している状態で、グローバルビット線GBLの側のプリチャージ回路(不図示)によりプリチャージ電圧がグローバルビット線GBLに供給される。所定時間が経過してローカルビット線LBLの電位がプリチャージ電圧に収束すると、プリチャージ回路LPCによりプリチャージ電圧がローカルビット線LBLに供給される。

(もっと読む)

半導体記憶装置

【課題】リフレッシュ時間のマージンを十分に確保しつつ、微細化が可能な半導体記憶装置を提供することを目的とする。

【解決手段】メモリセルを、読み出しトランジスタ、書き込みトランジスタ、キャパシタにより構成する。かかる構成において、キャパシタは読み出しトランジスタのゲートにかかる電位を制御する。書き込みトランジスタは、データの書き込みおよび消去を制御するとともに、キャパシタに蓄積された電荷が、該書き込みトランジスタのリーク電流で消失しないように、オフ時の電流が小さいトランジスタで構成する。書き込みトランジスタを構成する半導体層は、読み出しトランジスタのゲート電極とソース領域の間を架橋するように設ける。キャパシタは、読み出しトランジスタのゲート電極と重畳するように設ける。

(もっと読む)

半導体メモリ装置および半導体メモリ装置の駆動方法

【課題】消費電力の少ない新規の半導体メモリ装置を提供する

【解決手段】書き込みトランジスタWTr_n_mのソースと読み出しトランジスタRTr_n_mのゲートとキャパシタCS_n_mの一方の電極を接続し、書き込みトランジスタWTr_n_mのゲートとドレインを、それぞれ書き込みワード線WWL_nと書き込みビット線WBL_mに、キャパシタCS_n_mの他方の電極を読み出しワード線RWL_nに、読み出しトランジスタRTr_n_mのドレインを読み出しビット線RBL_mに接続した構造とする。ここで、読み出しビット線RBL_mの電位はフリップフロップ回路FF_mのような反転増幅回路に入力され、反転増幅回路によって反転された電位が書き込みビット線WBL_mに出力される構造とする。

(もっと読む)

半導体装置

【課題】センスアンプのセンスマージンを拡大する。

【解決手段】2つの素子分離領域3に隣接して各ウェル1,2にドライバトランジスタ4a,5a,4b,5bをそれぞれ配置し、各ウェル1,2にドライバトランジスタ4a,5a,4b,5bよりも素子分離領域3a,3bから離れた位置にクロスカップルされた2つの一対のセンストランジスタ6a乃至9a、6b乃至9bをそれぞれ配置する。これにより、センストランジスタ6a乃至9a、6b乃至9bと夫々対応する素子分離領域3a,3bと間に一定以上の距離が確保されることから、素子分離領域3a,3bからの距離によってトランジスタのしきい値が変化する現象の影響が低減され、その結果、夫々クロスカップルされた一対のトランジスタの特性を正確に一致させることが可能となる。

(もっと読む)

半導体装置

【課題】 半導体装置のレイアウト面積を大きくすることなく、内部電源回路の電流供給能力の向上を可能にする。

【解決手段】 半導体装置は、主領域12と、第1の方向に沿って主領域に形成された複数の第1の電源配線15と、第1の電源配線と交差しかつ電気的に接続されるように第2の方向に沿って主領域に形成された複数の第2の電源配線16と、第1の方向に関して主領域の一方の側に隣接する第1の隣接領域13に設けられ、第1の電源配線の一端にそれぞれ接続された第1の内部電源回路17と、第2の方向に関して主領域の一方の側に隣接する第2の隣接領域14に設けられ、複数の第2の電源配線のうち最も第1の電源配線の他端に近い電源配線の一端に接続された第2の内部電源回路18と、を備える。

(もっと読む)

1 - 20 / 90

[ Back to top ]