国際特許分類[G02F1/1368]の内容

物理学 (1,541,580) | 光学 (228,178) | 光の強度,色,位相,偏光または方向の制御,例.スイッチング,ゲーテイング,変調または復調のための装置または配置の媒体の光学的性質の変化により,光学的作用が変化する装置または配置;そのための技法または手順;周波数変換;非線形光学;光学的論理素子;光学的アナログ/デジタル変換器 (92,458) | 独立の光源から到達する光の強度,色,位相,偏光または方向の制御のための装置または配置,例.スィッチング,ゲーテイングまたは変調;非線形光学 (92,146) | 強度,位相,偏光または色の制御のためのもの (89,922) | 液晶に基づいたもの,例.単一の液晶表示セル (81,145) | 構造配置;液晶セルの作動;回路配置 (68,793) | 半導体の層または基板と構造上組み合された液晶セル,例.集積回路の一部を構成するセル (6,819) | アクティブマトリックスセル (6,630) | スイッチング素子が三端子の素子であるもの (6,192)

国際特許分類[G02F1/1368]に分類される特許

11 - 20 / 6,192

半導体装置およびその製造方法ならびに表示装置および電子機器

【課題】配線層の膜応力を低減し、製造歩留まりを向上することが可能な半導体装置およびその製造方法並びに表示装置および電子機器を提供する。

【解決手段】本技術の半導体装置は、一方向に延在する複数の第1配線層と、第1配線層の間に設けられた第1配線層よりも膜厚が薄いゲート電極と、第1配線層およびゲート電極上に形成された絶縁膜と、絶縁膜上の前記ゲート電極に対応する位置にチャネル領域を有する半導体層と、半導体層上に設けられた層間膜と、層間膜上に形成されると共に、層間膜に設けられた貫通孔を介して半導体層と接続された第2配線層とを備えている。

(もっと読む)

薄膜トランジスタアレイおよびその製造方法、並びに表示装置

【課題】配線密度を高くしすぎることなく断線を修復することが可能であり、フレキシブル性を持たせる場合に短絡や断線などを抑えることが可能な薄膜トランジスタアレイおよびその製造方法、並びに表示装置を提供する。

【解決手段】第1導電層と、前記第1導電層の少なくとも一部に対向して、前記第1導電層に合わせた平面形状の開口を有する絶縁膜と、前記開口を塞ぐと共に前記開口内で前記第1導電層に接するパッチ部を含む第2導電層とを備えた薄膜トランジスタアレイ。

(もっと読む)

トランジスタ、表示装置および電子機器

【課題】良好な歩留りで製造可能なトランジスタ、表示装置および電子機器を提供する

【解決手段】ゲート電極と、絶縁層を間にして前記ゲート電極に対向する半導体層と、

前記半導体層に電気的に接続された一対のソース・ドレイン電極と、前記一対のソース・ドレイン電極それぞれと前記半導体層との間のキャリア移動経路に設けられ、その端面が前記ソース・ドレイン電極に覆われたコンタクト層と、を備えたトランジスタ。

(もっと読む)

コンタクトホールの形成方法および電気光学装置の製造方法

【課題】シュリンク技術を利用して、コンタクトホールとして利用できる複数の凹部を1回のレジストマスク工程で異なる深さ寸法に形成することのできるコンタクトホールの形成方法、および電気光学装置の製造方法を提供すること。

【解決手段】電気光学装置の素子基板10上にコンタクトホールを形成するにあたって、まず、第1開口部17aおよび第2開口部17bを備えたレジストマスク17を層間絶縁膜42の表面に形成した後、第1開口部17aおよび第2開口部17bから層間絶縁膜42および絶縁膜49をエッチングする。その後、シュリンク工程において、レジストマスク17を変形させて第2開口部17bを塞ぐ一方、第1開口部17aの開口面積を狭める。次に、第1開口部17aから層間絶縁膜41およびゲート絶縁層2をエッチングする。

(もっと読む)

表示装置、電子機器、および、表示装置の製造方法

【課題】応答速度の速い表示装置、電子機器、および、表示装置の製造方法を提供する。

【解決手段】例えばFFSモード等の横電界によって液晶分子を制御する表示装置は、第1電極および第1電極と対向すると共に互いに延在方向が同一の複数の開口を有する第2電極を含む電極層と、電極層上に設けられ、開口の幅方向において対向する一方の側および他方の側の近傍領域の液晶分子が互いに逆方向に回転して配向する液晶層とを備えている。

(もっと読む)

電気光学装置および電子機器

【課題】シリケートガラスによって、シール材と基板との界面からの水分の侵入や、シール材で囲まれた領域内に侵入した水分の影響を低減することのできる電気光学装置、および当該電気光学装置を備えた電子機器を提供すること。

【解決手段】電気光学装置100では、素子基板10および基板本体10w(第1基板)側においてシール材107と接するのは、BSG膜からなるシリケートガラス層18(第1シリケートガラス層)であり、対向基板20および基板本体20w(第2基板)側においてシール材107と接するのは、BSG膜からなるシリケートガラス層28(第2シリケートガラス層)である。シール材107で囲まれた領域で、シリケートガラス層18は、画素電極9aおよびダミー画素電極9bの非形成領域9cで液晶層50に表面を向けており、シリケートガラス層28は、共通電極21の非形成領域21cで液晶層50に表面を向けている。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】信頼性の高い半導体装置、及び該半導体装置の作製方法を提供する。

【解決手段】酸化物半導体膜上にチャネル保護膜として機能する絶縁層が設けられたボトムゲート構造のトランジスタを有する半導体装置において、酸化物半導体膜上に接して設けられる絶縁層、及び/または、ソース電極層及びドレイン電極層の形成後に不純物除去処理を行うことで、エッチングガスに含まれる元素が、酸化物半導体膜表面に不純物として残存することを防止する。酸化物半導体膜の表面における不純物濃度は、5×1018atoms/cm3以下、好ましくは1×1018atoms/cm3以下とする。

(もっと読む)

液晶表示装置

【課題】コストの削減を可能とするとともに表示品位の劣化を抑制することを可能とする。

【解決手段】 第1方向に延出した第1補助容量線及び第2補助容量線と、第1補助容量線と第2補助容量線との間に位置し第1方向にゲート配線と、画素の略中央でゲート配線の上方に位置する半導体層と、半導体層とコンタクトし第2方向にソース配線と、半導体層にコンタクトし第1補助容量線及び第2補助容量線の上方に延出したドレイン電極と、ドレイン電極と電気的に接続され第1補助容量線と対向し第1方向に延出した第1主画素電極及びドレイン電極と電気的に接続され第2補助容量線と対向し第1方向に延出した第2主画素電極を備えた画素電極と、を備えた第1基板と、第1主画素電極を挟んだ両側及び第2主画素電極を挟んだ両側に位置し第1方向に延出した主共通電極を備えた共通電極を備えた第2基板と、を備えた液晶表示装置。

(もっと読む)

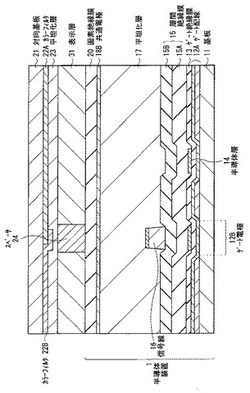

薄膜トランジスタ回路基板、及びその製造方法

【課題】厚いゲート絶縁層を有する薄膜トランジスタと、薄いゲート絶縁層を有する薄膜トランジスタとを備えた回路基板を提供する。

【解決手段】ポリシリコン半導体層の上下に、ボトムゲート型薄膜トランジスタのゲート絶縁層とトップゲート型薄膜トランジスタのゲート絶縁膜とを各々設け、トップゲート型薄膜トランジスタのゲート絶縁膜の厚さをボトムゲート型薄膜トランジスタのゲート絶縁層の厚さと異ならせる。

(もっと読む)

液晶表示装置

【課題】酸化物半導体を用いた薄膜トランジスタを具備する画素において、開口率の向上を図ることのできる液晶表示装置を提供することを課題の一とする。

【解決手段】画素は、トランジスタと、走査線として機能することができる第1の配線と、信号線として機能することができる第2の配線と、画素電極とを有し、画素は、当該第1の配線と同時に形成された容量線を有さない液晶表示装置である。

(もっと読む)

11 - 20 / 6,192

[ Back to top ]