国際特許分類[G06F12/08]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | 電気的デジタルデータ処理 (228,215) | メモリ・システムまたはアーキテクチャ内でのアクセシング,アドレシングまたはアロケーティング (20,382) | アドレシングまたはアロケーション;リロケーション (4,708) | 階層構造のメモリ・システム,例.仮想メモリ・システム,におけるもの (2,277)

国際特許分類[G06F12/08]の下位に属する分類

国際特許分類[G06F12/08]に分類される特許

11 - 20 / 1,680

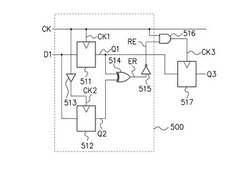

演算処理装置

【課題】キャッシュメモリから高速にデータを読み出すことができる演算処理装置を提供することを課題とする。

【解決手段】演算処理装置は、複数の記憶素子にそれぞれ複数のデータを記憶するキャッシュメモリと、前記キャッシュメモリからデータが読み出されたタイミングが閾値より遅いときにはエラーを検出するエラー検出回路(500)と、前記エラーが検出されないときには前記キャッシュメモリから読み出されたデータをラッチし、前記エラーが検出されたときには待機期間経過後に前記キャッシュメモリから読み出されたデータをラッチするラッチ回路(517)と、前記ラッチ回路によりラッチされたデータの処理を行う演算処理装置コアとを有する。

(もっと読む)

管理装置、管理方法、およびプログラム

【課題】複数のアプリケーションが順次に実行される場合において、効率的なメモリ管理を行うことが可能な、管理装置、管理方法、およびプログラムを提供する。

【解決手段】複数のアプリケーションの実行順序を示す実行制御情報に基づいて、アプリケーションが実行されるときにアプリケーションが一時的に記憶される記録媒体における、実行領域と、キャッシュ領域とを管理する管理部を備える、管理装置が提供される。

(もっと読む)

部分読出と非スヌープアクセスとの間のメモリ順序付け要件の充足

【課題】部分的且つ非コヒーレントなメモリアクセスの観点からキャッシュ・コヒーレンス・リンクに基づく相互接続でメモリ順序付けを保つ方法及び装置を提供する。

【解決手段】例えば部分書込のような部分的なメモリアクセスに関連するコンフリクトが検出される場合に、ライトバックフェーズがコンフリクトフェーズで挿入され、ホームエージェントへ部分的データをライトバックする。コンフリクトフェーズでライトバックフェーズを挿入するメッセージの例には、コンフリクトを認めて、コンフリクトフェーズの開始時にライトバックマーカーを、コンフリクトフェーズ前にライトバックマーカーメッセージを、コンフリクトフェーズ内でライトバックマーカーメッセージを、コンフリクトフェーズ後にライトバックマーカーメッセージ及びポスタブル・メッセージを提供するAcknowledge Conflict Write-backメッセージがある。

(もっと読む)

情報処理装置、ハイブリッド記憶装置、およびキャッシュ方法

【課題】記憶装置をHDDのキャッシュとして利用する場合に、アクセス性能の低下、およびキャッシュヒット率の低下を抑制すること。

【解決手段】実施形態によれば、ホストからのハードディスクドライブへのアクセス要求に対して、前記ハードディスクドライブの設定数以上の連続するセクタのデータにアクセスするかを判定する判定手段と、記憶装置を前記ハードディスクドライブのキャッシュとして用いるキャッシュ手段であって、前記設定数以上の連続するセクタのデータにアクセスすると判定された場合に前記記憶装置をキャッシュとして用いない、キャッシュ手段とを具備する。

(もっと読む)

情報処理装置

【課題】ネットワーク透過な単一レベル記憶を実現すること。

【解決手段】本発明の一つの実施形態によれば、情報処理装置は、第1メモリと、第2メモリと、仮想アドレス空間の少なくとも一部の仮想アドレスと前記第1メモリの物理アドレスとの対応関係を管理する変換情報を参照して、前記第1メモリにアクセスする制御部と、を備える。前記仮想アドレス空間には、他の情報処理装置に格納されたデータも割り当てられる。前記制御部は、アクセス対象データが前記他の情報処理装置に格納され手いる状態でページフォールトが発生した場合、前記他の情報処理装置に格納された前記アクセス対象データを前記第1メモリに格納するとともに、前記アクセス対象データに対応する仮想アドレスと前記第1メモリの物理アドレスの対応関係を前記変換情報に登録する。

(もっと読む)

低電力モード中にキャッシュされた情報を保存する技術

【課題】コンピューティング・システムおよびマイクロプロセッサ内の電力管理分野に関するプロセッサ、システム、および、方法を提供する。

【解決手段】低電力モード中にキャッシュされた情報を保持するための技術である。プロセッサ100のローカル・キャッシュ107,113に格納された情報は、プロセッサが低電力モードに置かれる前に共有キャッシュ115に保存されるので、他のプロセッサは、低電力モードのプロセッサを、そのローカル・キャッシュへのアクセスを提供するように低電力モードから復帰させる代わりに、共有キャッシュからの情報にアクセスする。

(もっと読む)

制御システム、制御方法およびプログラム

【課題】プリフェッチに使用される電力が無駄になることを防止可能な制御システム、制御方法およびプログラムを提供する。

【解決手段】制御システム100は、処理装置と主記憶装置とキャッシュメモリとプリフェッチ部と電源部とを備えた制御システムであって、検出部81と判定部82と電源制御部83とを備える。検出部81は、処理装置が処理を実行していないアイドル状態であるか否かを検出する。判定部82は、アイドル状態であると検出された場合、プリフェッチの状態に応じて、キャッシュメモリに対する電力の供給を停止するか否かを判定する。電源制御部83は、キャッシュメモリに対する電力の供給を停止すると判定された場合は、キャッシュメモリに対する電力の供給を停止するように電源部を制御し、キャッシュメモリに対する電力の供給を停止しないと判定された場合は、キャッシュメモリに対する電力の供給を継続するように電源部を制御する。

(もっと読む)

マルチレベルのキャッシュ階層におけるキャストアウトを低減するための装置および方法

【課題】下位レベルキャッシュから置換されたキャッシュラインの上位レベルキャッシュへの割り当てを低減する方法を提供する。

【解決手段】置換ラインがすでに上位レベルに割り当てられと決定されたとき、置換されたキャッシュラインの割り当ては、次のレベルキャッシュにおいて防がれ、これにより、キャストアウトが低減する。そのような目的に、ラインは、下位レベルキャッシュ204において置換されるように選択される。上位レベルキャッシュ208において選択されたラインが存在するか示す選択されたラインに関連する情報が識別される。上位レベルキャッシュにおける選択されたラインの割り当ては、識別された情報に基づいて防がれる。選択されたラインの割り当てを防ぐことは、割り当てに関連するであろう電力を蓄える。

(もっと読む)

制御システム、制御方法およびプログラム

【課題】消費電力量を低減可能な制御システム、制御方法およびプログラムを提供する。

【解決手段】制御システム100は、検出部51と推定部52と判断部53と制御部54とを備える。検出部51はアイドル状態を検出する。推定部52はアイドル時間を推定する。判断部53は、アイドル状態が検出された場合、主記憶装置への書き戻しが必要なデータの書き戻しを行ってキャッシュメモリに対する電力の供給を停止した場合の第1消費電力量が、当該データの書き戻しを行わずにアイドル時間にわたってキャッシュメモリに対する電力の供給を継続した場合の第2消費電力量よりも大きいか否かを判断する。制御部54は、第1消費電力量が第2消費電力量よりも小さいと判断された場合は、キャッシュメモリに対する電力供給を停止させる一方、第1消費電力量が第2消費電力量よりも大きいと判断された場合は、キャッシュメモリに対する電力供給を継続させる。

(もっと読む)

キャッシュメモリ装置、プロセッサ、および情報処理装置

【課題】十分な消費電力の削減が図ることができるキャッシュメモリ装置を提供する。

【解決手段】キャッシュメモリ装置100aは、記憶装置のデータをキャッシュする。キャッシュメモリ装置100aは、記憶部110aと、制御部120aと、を備える。記憶部110aは、複数のキャッシュラインを有する。制御部120aは、前記複数のキャッシュラインのうち、前記記憶装置に書き込まれていないデータを含むダーティラインの数が予め定めた所定数を超える場合に、前記ダーティラインのデータを前記記憶装置に書き込む。

(もっと読む)

11 - 20 / 1,680

[ Back to top ]