国際特許分類[G06F12/08]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | 電気的デジタルデータ処理 (228,215) | メモリ・システムまたはアーキテクチャ内でのアクセシング,アドレシングまたはアロケーティング (20,382) | アドレシングまたはアロケーション;リロケーション (4,708) | 階層構造のメモリ・システム,例.仮想メモリ・システム,におけるもの (2,277)

国際特許分類[G06F12/08]の下位に属する分類

国際特許分類[G06F12/08]に分類される特許

61 - 70 / 1,680

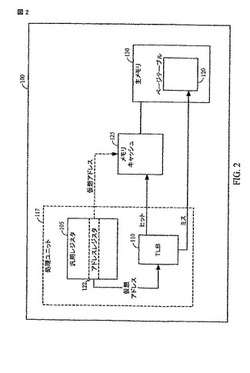

キャッシュされたメモリデータを伴うキャッシュメモリ属性インジケータ

【課題】TLBにおける照合を高速化するとともに消費電力の増加を抑制する。

【解決手段】複数のページにデータを記憶するように構成されたメモリ130と、TLB110と、複数のキャッシュラインを含むメモリキャッシュ125とを含むことができる。メモリの各ページは複数のメモリのラインを有することができる。メモリキャッシュは、仮想アドレスがキャッシュに与えられると、適合キャッシュラインが複数のキャッシュラインから同定できるように構成されることができ、ここで、適合キャッシュラインは、仮想アドレスに適合する適合アドレスを有する。メモリキャッシュは、適合アドレスに配置されたページの1つまたは複数のページ属性を、TLBからではなく、メモリキャッシュから検索できるように構成されることができ、これは、キャッシュラインに記憶されたラインデータのページ属性を、キャッシュラインの夫々に更に記憶することによって行われる。

(もっと読む)

記憶装置およびプログラム

【課題】記憶装置と通信を行う複数のデバイスのキャッシュメモリに記憶されたデータの不整合を解消可能な記憶装置およびプログラムを提供する。

【解決手段】実施形態の記憶装置は、記憶部と、通信部と、書き込み部と、制御部とを備える。記憶部は、複数のデータを記憶する。通信部は、記憶部に記憶された複数のデータのうちの少なくとも一部を記憶する第1キャッシュメモリを有する複数の外部機器と通信する。書き込み部は、複数の外部機器のうちの何れかの外部機器から、データの書き込みを要求する書き込み要求を通信部で受信した場合、その書き込みが要求されたデータを記憶部に書き込む。制御部は、書き込み部により書き込まれたデータを、書き込み要求を送信した外部機器とは異なる外部機器へ送信するように通信部を制御する。

(もっと読む)

命令実行分析装置及び命令実行分析方法及びプログラム

【課題】キャッシュメモリの利用効率を向上させる。

【解決手段】メインメモリ装置へのメモリアクセスが実施されて命令が実行されるシミュレーションを実施し、シミュレーションにおいてメモリアクセスの対象がメモリブロック内の一部のデータに偏っているメモリブロックを非効率ブロックとして抽出する(非効率ブロックの抽出処理2)とともに、非効率ブロックへのメモリアクセスを発生させた命令を非効率命令として抽出する(非効率命令の抽出処理3)。これにより、キャッシュメモリの同一ブロックにアクセス頻度の高いデータと低いデータが混在することを防止し、キャッシュメモリの利用効率を向上させることができる。

(もっと読む)

キャッシュメモリ装置及び制御方法

【課題】キャッシュメモリに記憶されたピクセルデータの利用率向上を可能とするキャッシュメモリ装置を提供する。

【解決手段】本発明は、表示する画像データの幅がWピクセルであり、2次元方形領域の幅がaピクセル及び縦がbピクセルの場合、横方向のエントリ数がW/aである数pであり、縦方向のエントリ数が[a×2(1/2)/b]の整数値に2を加えた数qであるエントリマトリクスのキャッシュメモリと、表示画面の座標系の表示アドレスを、表示メモリの画像データの座標系へ角度θで座標変換が行われた、2次元方形領域のメモリアドレスから、エントリアドレスを生成するエントリアドレス生成部と、表示メモリからメモリアドレスを用いた角度θのラスタースキャンで分割画像データを読み出し、キャッシュメモリに書き込む書込制御部と、表示される画像データの全走査線に対応するピクセルデータを順次読み出す読出制御部とを有する。

(もっと読む)

退避処理装置、及び、退避処理方法

【課題】複雑な処理を行わず、キャッシュメモリに蓄積中のデータの退避処理を可能とする。

【解決手段】キャッシュメモリの退避を行う第1の不揮発性メモリと、第2の不揮発性メモリと、キャッシュメモリ内のデータにおいて、第1の不揮発性メモリの書込が失敗した領域の情報の履歴を記録した管理テーブルを記憶する記憶部と、第1の不揮発性メモリへの退避処理を行う第1の制御部と、第1の制御部から送られてくる情報を、時間情報と共に、第2の不揮発性メモリへ書きこむ第2の制御部とを有し、第1の制御部は、停電発生時に、キャッシュメモリに記憶されているデータを不揮発性メモリに書き込む処理を実行し、前記退避処理に当たり、該書込が正常に行われたかを検証するとともに、該検証にて正常に書きこまれていない場合、前記不揮発性メモリの正常な書込ができなかった領域の情報を、記憶部に記憶する。

(もっと読む)

通信装置、通信方法、およびプログラム

【課題】ディスク記憶媒体のデータを、複数のサーバにインストールさせる作業に、長い時間を要しない通信装置を提供する。

【解決手段】通信装置5は、プロトコルシリアライザ10と、キャッシュコントローラ11とを備える。プロトコルシリアライザ10は、ディスク記憶媒体Kに記憶されたデータの読取要求を、サーバA1〜A3から受信するとともに、該受信した読取要求を、ディスク記憶媒体Kへの一つのアクセス権に係る命令にシリアライズする。キャッシュコントローラ11は、シリアライズされた読取要求の順序に従って、読取要求に係る要求データを、ディスク記憶媒体Kに記憶されたデータの中から取得する。また、プロトコルシリアライザ10は、キャッシュコントローラ11が取得した要求データを、該要求データに対応する読取要求の送信元サーバAに送信する。

(もっと読む)

キャッシュメモリおよびキャッシュシステム

【課題】キャッシュメモリの面積の増大を抑制しつつ、高速化する。

【解決手段】キャッシュメモリ2はタグメモリ103と、第1のダーティビットメモリ106と、有効ビットメモリ107と、データメモリ105と、を含む複数のキャッシュラインを有する複数のウエイを備える。また、キャッシュメモリ2は、前記キャッシュラインを特定するためのラインインデックスメモリ101を備える。また、キャッシュメモリ2は、前記ウエイを特定する第1のビットデータおよび前記ラインインデックスを特定する第2のビットデータを記憶するローメモリ202と、前記データメモリへのバイト単位のライトに対応したビット単位の第2のダーティビットを記憶する第2のダーティビットメモリ203と、登録された順番を規定するFIFO情報を記憶するFIFOメモリ204と、を含む複数のラインを有するDBLBシステム201と、を備える。

(もっと読む)

キャッシュシステムおよび処理装置

【課題】 動作が速い低消費電力なキャッシュシステムを提供する。

【解決手段】 本発明の実施形態によるキャッシュシステムは、揮発性キャッシュメモリーと、不揮発性キャッシュメモリーと、前記揮発性キャッシュメモリーに記憶される各データに対応付けて、その揮発性キャッシュメモリーに記憶されるデータよりも未使用時間の長い(もしくは短い)データが前記不揮発性キャッシュメモリーに記憶されている数に応じたデータを記憶する順序保存部と、前記揮発性キャッシュメモリーに記憶された第1のデータを他のアドレスを有する第2のデータで上書きするときに、前記第1のデータと対応付けて前記順序保存部に記憶されたデータに基づいて、前記第1のデータの未使用時間が前記不揮発性キャッシュメモリーに記憶されているいずれかのデータの未使用時間よりも短いと判断できる場合、前記第1のデータを前記不揮発性キャッシュメモリーに記憶させる制御部を有する。

(もっと読む)

演算処理装置および演算処理装置の制御方法

【課題】キャッシュメモリを実装した演算処理装置およびキャッシュメモリ制御装置において、プロセスIDに対応してキャッシュメモリ領域をブロック単位で任意に分割可能として、プロセッサの実効性能を向上することを可能とする。

【解決手段】各セット103のキャッシュブロック102毎に物理プロセスID(PPID)が記憶されるとともに、#1から#nの各インデックス値毎に、各PPID値に対するMAX WAY数105が記憶される。或るインデックス値における或るPPID値に対応するMAX WAY数105は、そのインデックス値において記憶可能なそのPPID値を有するキャッシュブロック102の最大数を示す。各インデックス値毎に、各PPID値のMAX WAY数105が守られるように、キャッシュミス時のウェイ数の制御が実施される。

(もっと読む)

情報処理装置およびプログラム

【課題】2次ストレージへの書き込み頻度を下げて消費電力を下げる。

【解決手段】実施形態の情報処理装置は、補助記憶部と、主記憶部と、蓄電部と、第1書込部と、第2書込部と、を備える。主記憶部は、補助記憶部に記憶するデータを一時記憶するキャッシュ領域を含む不揮発性の記憶部である。第1書込部は、データをキャッシュ領域に書き込む。第2書込部は、蓄電部の電力量が予め定められた第1閾値より大きい場合に、キャッシュ領域に書き込まれたデータを補助記憶部に書き込む。

(もっと読む)

61 - 70 / 1,680

[ Back to top ]