国際特許分類[G06F12/08]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | 電気的デジタルデータ処理 (228,215) | メモリ・システムまたはアーキテクチャ内でのアクセシング,アドレシングまたはアロケーティング (20,382) | アドレシングまたはアロケーション;リロケーション (4,708) | 階層構造のメモリ・システム,例.仮想メモリ・システム,におけるもの (2,277)

国際特許分類[G06F12/08]の下位に属する分類

国際特許分類[G06F12/08]に分類される特許

71 - 80 / 1,680

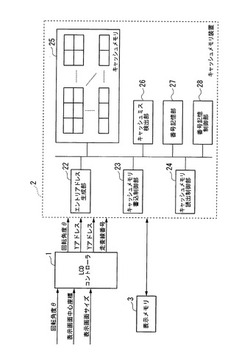

キャッシュメモリ装置及び制御方法

【課題】キャッシュメモリに記憶されたピクセルデータの利用率向上を可能とするキャッシュメモリ装置を提供する。

【解決手段】本発明は、表示する画像データの幅がWピクセルであり、2次元方形領域の幅がaピクセル及び縦がbピクセルの場合、横方向のエントリ数がW/aである数pであり、縦方向のエントリ数が[a×2(1/2)/b]の整数値に2を加えた数qであるエントリマトリクスのキャッシュメモリと、表示画面の座標系の表示アドレスを、表示メモリの画像データの座標系へ角度θで座標変換が行われた、2次元方形領域のメモリアドレスから、エントリアドレスを生成するエントリアドレス生成部と、表示メモリからメモリアドレスを用いた角度θのラスタースキャンで分割画像データを読み出し、キャッシュメモリに書き込む書込制御部と、表示される画像データの全走査線に対応するピクセルデータを順次読み出す読出制御部とを有する。

(もっと読む)

メモリ制御装置、メモリ装置、メモリ制御方法、及びプログラム

【課題】ライトバック処理の実行に起因して他の処理の処理速度が低下することを抑制することが可能な、新規かつ改良されたメモリ制御装置、メモリ装置、メモリ制御方法、及びプログラムを提供する。

【解決手段】主記憶部へのデータの書き込み又は読み出しと、キャッシュブロックを複数有するキャッシュ部へのデータの一時的な書き込み又は読み出しと、を実行するデバイスドライバと、前記主記憶部又は前記キャッシュ部へのファイルシステムのデータの書き込み又は読み出しを、前記デバイスドライバに命令する制御部と、を備え、前記制御部は、前記キャッシュブロックに記憶されているデータを前記デバイスドライバによって前記主記憶部に移動させるデータ移動処理を実行可能なタイミング情報を、前記デバイスドライバに通知する、メモリ制御装置。

(もっと読む)

リプレースメントデータメモリ装置、中央演算装置及びリプレースメントデータ処理方法

【課題】キャッシュ・ミス発生時の主記憶装置へのアクセス回数を低減する。

【解決手段】キャッシュメモリでリプレースメントが発生した時に主記憶装置にストアされるリプレースメントデータのうち前記リプレースメントの起因となったキャッシュミスに係る、前記キャッシュメモリのアドレスに記憶されていたデータのみを記憶し、別のキャッシュミスが発生した時に、該別のキャッシュミスに係るデータが自装置に記憶されているならば、自装置に記憶されている前記別のキャッシュミスに係るデータをロードデータとする。

(もっと読む)

キャッシュコントローラ、キャッシュ制御方法及びデータ記憶装置

【課題】ハードエラーの発生に対する効率的な対処を実現し、キャッシュ動作の性能の劣化を抑制できるキャッシュコントローラを提供することにある。

【解決手段】実施形態によれば、キャッシュコントローラは、エラー検出訂正モジュールと、コントローラとを具備する。エラー検出訂正モジュールは、キャッシュメモリから読み出されたデータからエラーを検出し、当該エラーを訂正する。コントローラは、前記エラー検出訂正手段によるエラー訂正が不可能で前記エラーの種別がハードエラーの場合に、前記キャッシュメモリに対する電源遮断及び電源再投入の電源制御を実行する。

(もっと読む)

キャッシュシステムおよび処理装置

【課題】 消費電力を削減するとともに、動作速度が速いキャッシュシステムおよび処理装置を提供すること。

【解決手段】 本発明の実施形態によるキャッシュシステムは、揮発性キャッシュメモリーと、前記揮発性キャッシュメモリーと同容量の不揮発性キャッシュメモリーと、前記揮発性キャッシュメモリーと前記不揮発性キャッシュメモリーとに対して同じラインを指定するアドレスデコーダと、前記揮発性キャッシュメモリーから入力されるデータを記憶し、記憶したデータを前記揮発性キャッシュメモリーへ出力する退避領域とを有することを特徴とする。

(もっと読む)

メモリシステム、キャッシュメモリ制御方法及びメモリ制御プログラム

【課題】ストアイン方式のメモリシステムにおいて、アクセス頻度が高いアドレスのリプレース頻度を減らし、メモリシステムの性能悪化を軽減することができるメモリシステムを提供すること

【解決手段】本発明のメモリシステムは、1stキャッシュメモリ10と1stキャッシュメモリ10に優先してプロセッサからアクセスされる1stキャッシュメモリ20と、1stキャッシュメモリ10においてキャッシュデータのリプレースを行う場合に、1stキャッシュメモリ10に格納されているキャッシュデータのうち、それぞれのキャッシュデータが過去にリプレース対象となったか否かを示す履歴情報を用いて、リプレース対象キャッシュデータを決定し、1stキャッシュメモリ20に格納されているキャッシュデータのうちリプレース対象のキャッシュデータと同一のキャッシュデータを無効化するリプレース部4と、を備える。

(もっと読む)

アクセラレータ用低コストのキャッシュ一貫性を維持するシステム

【課題】アクセラレータとCPUとの一貫性を維持しながら通信によるノード間の帯域幅の消費を低減する。

【解決手段】CPU210およびアクセラレータ220はマルチプロセッシング環境において個別のノードにクラスターできる。共有メモリ・デバイス212、222を収容する各ノード0、1は、他のノードでキャッシュされたかもしれない共有メモリのブロックを追跡するディレクトリを維持できる。そのため、コマンドとアドレスは、メモリ位置があるノード以外でキャッシュされたときに限り、他のノードのプロセッサおよびアクセラレータに送信できる。加えて、アクセラレータは一般的にCPUと同じデータにはアクセスしないため、最初の読み出し、書き込み、および同期の操作のみを他のノードに送信できる。データへの中間アクセスは一貫性を保たないで行える。その結果、一貫性を維持するために消費するチップ間の帯域幅を低減できる。

(もっと読む)

システムパフォーマンスを改善するための外部メモリデバイスの使用

【課題】回転式ストレージデバイス(例えば、ハードドライブ)のセクタをキャッシュするために外部メモリデバイスを利用して、システムパフォーマンスを改善するためのシステムおよび方法を提供すること。

【解決手段】外部メモリデバイス(EMD)が、コンピューティングデバイス、またはコンピューティングデバイスが接続されたネットワークに接続されたとき、システムは、EMDを認識し、ディスクセクタによってEMDをポピュレートする。システムは、ディスクセクタに対するI/O読取り要求を、実際のディスクセクタの代わりにEMDキャシュに向けて送る。EMDの使用は、コンピューティングデバイスにメモリを追加するコストに対してわずかのコストで、コンピューティングデバイスシステムにおけるパフォーマンスおよび生産性を向上させる。

(もっと読む)

仮想計算機システム、仮想計算機システムのメモリ管理方法およびメモリ管理プログラム

【課題】稼動中のゲストOSの性能を低下させず、かつ、高速でゲストOSを起動させる。

【解決手段】仮想計算機システムは、実計算機で複数のオペレーティングシステムを同時実行可能な仮想計算機システムであって、停止したオペレーティングシステム用の主メモリを、稼働中のオペレーティングシステム用のキャッシュ領域に割り当てるキャッシュ割当手段11と、稼働中のオペレーティングシステム用のキャッシュ領域におけるクリーン領域を、起動するオペレーティングシステムの主メモリに割り当てる主メモリ割当手段12とを備える。

(もっと読む)

情報処理装置及びエラー訂正支援方法

【課題】リプライデータに訂正不能なエラーが生じたことに起因するシステムの稼働率の低下を改善しつつ、回路規模の膨大化を回避する。

【解決手段】キャッシュミスのときに、メインメモリから出力されるリプライデータRD0に対して、訂正不能なエラーの有無を検出すると共に、該検出の結果とメインメモリとを示す付加情報を付加する。上記付加情報を含むリプライデータRD1でブロックロードする際に、該リプライデータRD1に含まれる付加情報を記憶しておく。キャッシュヒットのときにキャッシュメモリから出力されるリプライデータRD2に対して、ブロックロード時に記憶しておいた付加情報が「エラーがある」を示す場合に上記付加情報を付加する。上記付加情報が「エラーが無い」を示す場合に、訂正不能なエラーの有無を検出すると共に、該検出の結果とキャッシュメモリとを示す付加情報を付加する。

(もっと読む)

71 - 80 / 1,680

[ Back to top ]