国際特許分類[G06F12/08]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | 電気的デジタルデータ処理 (228,215) | メモリ・システムまたはアーキテクチャ内でのアクセシング,アドレシングまたはアロケーティング (20,382) | アドレシングまたはアロケーション;リロケーション (4,708) | 階層構造のメモリ・システム,例.仮想メモリ・システム,におけるもの (2,277)

国際特許分類[G06F12/08]の下位に属する分類

国際特許分類[G06F12/08]に分類される特許

81 - 90 / 1,680

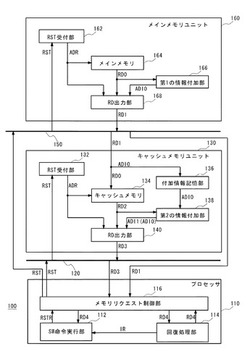

情報処理装置及びエラー訂正支援方法

【課題】リプライデータに訂正不能なエラーが生じたことに起因するシステムの稼働率の低下を改善しつつ、回路規模の膨大化を回避する。

【解決手段】キャッシュミスのときに、メインメモリから出力されるリプライデータRD0に対して、訂正不能なエラーの有無を検出すると共に、該検出の結果とメインメモリとを示す付加情報を付加する。上記付加情報を含むリプライデータRD1でブロックロードする際に、該リプライデータRD1に含まれる付加情報を記憶しておく。キャッシュヒットのときにキャッシュメモリから出力されるリプライデータRD2に対して、ブロックロード時に記憶しておいた付加情報が「エラーがある」を示す場合に上記付加情報を付加する。上記付加情報が「エラーが無い」を示す場合に、訂正不能なエラーの有無を検出すると共に、該検出の結果とキャッシュメモリとを示す付加情報を付加する。

(もっと読む)

光ディスク装置

【課題】

ディスクチェンジ機構を備えるアーカイブ装置において、高速なファイルアクセスを実現する。

【解決手段】

CPU301、メモリ302、外部IF303、HDD304、ディスク情報管理部305、ディスク入替制御部306、アクセス頻度判定部307、光ディスク制御部308、光ディスクドライブ202を備え、ディスクを新規作成時に、あらかじめ予備領域を設け、アクセス頻度に応じて高頻度と判定されたデータは光ディスクドライブ202にセットされたときに前記予備領域にデータを書き込む。ディスク情報管理部305は予備領域に書き込まれた同一の複数ファイルを管理し、外部IF303への応答としては一つのファイルとして通知する。

また、上記に加え暗号処理部509を設け、予備領域記録時には暗号化して記録し、削除時にはディスク情報管理部305の管理する管理情報のみ削除する。

(もっと読む)

メモリ装置の診断方法及びメモリ装置の診断装置並びに情報処理装置

【課題】メモリ装置を備えた情報処理装置の、処理上のスループットを低下させることなく、かつ高い信頼性を維持して該メモリ装置の故障診断を行うこと。

【解決手段】

アドレス予測部11は、情報処理装置3を構成するCPU付属のメモリ装置に対し、メモリアクセスの状況(より具体的には、キャッシュラインが保持するキャッシュライン管理情報など)から判断して、近々に書き込みアクセスが発生することになると予測されるメモリのアドレス情報の特定を行う。次に、通達部12は、アドレス予測部11が特定した前記アドレス情報を、メモリ診断部に送出する。これにより、メモリ診断部は、CPU付属のメモリ装置(図示は省略)の、該特定されたアドレス情報が示す記憶領域のみを目下の診断対象とすることができる。

(もっと読む)

記憶装置及びその制御方法

【課題】バックアップ電源の疲弊に応じて機器の動作を変える技術を提供する。

【解決手段】記憶用メモリと、この記憶用メモリへのキャッシュを担うキャッシュメモリ

と、このキャッシュメモリへのキャッシュサイズを制御する制御手段と、電源断時のバッ

クアップを行うバックアップ手段とを備え、このバックアップ手段の疲弊に応じて前記制

御手段は前記キャッシュサイズを変える記憶装置。また、記憶用メモリと、この記憶用メ

モリのキャッシュを担うキャッシュメモリとを備え、電源断時のバックアップを行う記憶

装置の制御方法であって、この記憶装置にバックアップを行うバックアップ電源の疲弊を

予め測定し、この疲弊に応じて前記キャッシュメモリへのキャッシュサイズを調整する制

御方法。

(もっと読む)

記憶装置およびそれを搭載した計算機

【課題】記憶装置に搭載するメモリ容量を削減しながら、情報を書き込む際の処理速度の低下を最低限に抑える。

【解決手段】不揮発性メモリ内に、論理/物理アドレス変換テーブルをページ単位に分割した複数の分割変換テーブルを保存し、RAM内には、分割変換テーブルの少なくとも1つ以上を保存する論理/物理アドレス変換テーブルキャッシュと、分割変換テーブルを管理する変換テーブル管理テーブルと、論理/物理アドレス変換テーブルキャッシュの管理を行うキャッシュ管理テーブルを保存し、変換テーブル管理テーブルは、分割変換テーブルが前記論理/物理アドレス変換テーブルキャッシュに保存されていることを示すキャッシュ有無フラグと、前記論理/物理アドレス変換テーブルキャッシュ内での保存先を示すキャッシュエントリ番号を有し、不揮発性メモリと前記RAMの間における前記論理/物理アドレス変換テーブルの情報の読み出し及び書き込みは、ページ単位で行う。

(もっと読む)

並列コンピュータ・システムの性能を改良するための装置、方法及びコンピュータ・プログラム

【課題】並列コンピュータ・システムの性能を改良するための装置、方法及びコンピュータ・プログラムを提供する。

【解決手段】第1プロセッサの第1ローカル・キャッシュに関連する第1ローカル・キャッシュ・コントローラは、プログラム・コードを実行中の第2プロセッサによる第1キャッシュ・ラインの偽共有(false sharing)の発生を検出し且つ第2プロセッサによる第1キャッシュ・ラインの偽共有を許可する。第1キャッシュ・ラインの偽共有が発生するのは、第1ローカル・キャッシュ・コントローラによって第1ローカル・キャッシュ内の第1キャッシュ・ラインの第1部分を更新し、その後に、第2ローカル・キャッシュ・コントローラによって第2ローカル・キャッシュ内の第1キャッシュ・ラインの第2部分を更新する場合である。

(もっと読む)

キャッシュ制御方法、キャッシュ制御装置およびキャッシュ制御用プログラム

【課題】受信したデータをキャッシュメモリに書き込んで処理を行う場合に、大量のデータを受信する状況であっても、処理性能が低下することを抑制できるキャッシュ制御方法を提供する。

【解決手段】領域設定手段81は、予め定められた量の受信データを書き込み可能な領域である書き込み領域をキャッシュメモリに設定する。領域削除手段82は、書き込み領域に書き込まれた一部または全部の受信データに対する処理ごとに、その処理の対象になった受信データが書き込まれた領域を削除する。また、領域設定手段81は、受信データに対する処理ごとに、予め定められた量の受信データを受信した後に受信する受信データを書き込む位置に、受信データを書き込み可能な領域として、削除された領域に相当する量の領域を新たに設定する。

(もっと読む)

キャッシュメモリの制御装置、キャッシュメモリシステム、キャッシュメモリの制御装置の製造方法

【課題】メインメモリのアドレス配置が変更された前後においてキャッシュメモリの使用態様がなるべく変動しないように制御すること。

【解決手段】キャッシュメモリの制御装置であって、メインメモリにおける特定のアドレス以降に格納されたプログラム又はデータについては、所定の対応関係に基づき特定されるキャッシュメモリのアドレスから所定アドレス分オフセットしたキャッシュメモリのアドレスに書き込まれるようにキャッシュメモリを制御し、メインメモリにおける特定のアドレス以降に格納されたプログラム又はデータを読み出そうとする際に、所定の対応関係に基づき特定されるキャッシュメモリのアドレスから所定アドレス分オフセットしたキャッシュメモリのアドレスに書き込まれたプログラム又はデータを対象としてキャッシュヒットを判定するキャッシュヒット判定手段を備えることを特徴とする、キャッシュメモリの制御装置。

(もっと読む)

プロセッサ、情報処理装置、情報処理方法及びシステム起動プログラム

【課題】ハーバードアーキテクチャを採用している処理プロセッサにおいて、命令フェッチを行わなければ命令キャッシュに命令を格納しておくことができなかった。

【解決手段】本発明にかかるプロセッサは、命令を一時記憶する第1の記憶手段と、命令及びデータを一時記憶する第2の記憶手段と、前記第2の記憶手段に一時記憶されている命令を前記第1の記憶手段に転送する転送手段と、第3の記憶手段に格納されている命令を前記第2の記憶手段に読み込む第1の制御と前記転送手段に対して前記第2の記録手段へ読み込まれた命令を前記第1の記憶手段に対して転送させる第2の制御とを行う制御手段と、を具備する。本発明の構成によれば、命令フェッチを行うことなく、命令を一旦データキャッシュに読み込んだ後に転送することで命令キャッシュに格納することができる。

(もっと読む)

ルータ及びメニーコアシステム

【課題】ルータ又は共有メモリの構造を複雑にすることなく、リードアクセスレイテンシを低減する。

【解決手段】ルータ14は、複数のコアと、複数のコアからアクセス可能なキャッシュメモリとの間で転送されるパケットの経路を管理する。ルータ14は、解析部144と、パケットメモリ145と、制御部143と、を備え,解析部144は、パケットがリードパケット及びライトパケットの何れかを解析し、パケットメモリ145は、発行されたライトパケットの一部を格納可能である。制御部143は、解析部144の解析結果に基づいて、ライトパケットの場合に、パケットのキャッシュデータと、格納されるべきキャッシュアドレスとを格納し、リードパケットであり、且つ、キャッシュデータがパケットメモリ145に格納されている場合に、キャッシュデータをリードパケットに対するレスポンスデータとして、コアへ出力する。

(もっと読む)

81 - 90 / 1,680

[ Back to top ]