国際特許分類[G06F17/50]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | 電気的デジタルデータ処理 (228,215) | 特定の機能に特に適合したデジタル計算またはデータ処理の装置または方法 (34,028) | 計算機利用設計 (7,589)

国際特許分類[G06F17/50]に分類される特許

31 - 40 / 7,589

動作合成方法、動作合成プログラム及び動作合成装置

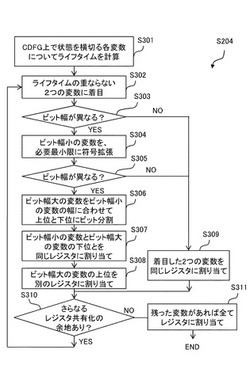

【課題】動作合成により共有化するレジスタのビット幅を小さくすることが可能な動作合成方法、動作合成プログラム及び動作合成装置を提供する。

【解決手段】動作合成方法は、動作記述情報に基づいてスケジューリングしたCDFGを生成し、スケジューリングされたCDFGに基づいてライフタイムを変数毎に生成し(S301)、ライフタイム情報が時間軸上で重ならないm個の変数を選択し(S302)、第1のビット幅の第1の変数と、その他の変数内の第1のビット幅のビットとに、第1のレジスタを割り当て(S307)、その他の変数内の第1のビット幅のビット以外のビットに、第2のレジスタを割り当て(S308)、第1及び第2のレジスタを有する合成回路の回路情報を出力する。

(もっと読む)

メッシュ生成装置、メッシュ生成方法、及びコンピュータプログラム

【課題】可能な限り少ない要素数で有限要素解析が可能な三次元メッシュを生成することができるメッシュ生成装置、メッシュ生成方法、及びコンピュータプログラムを提供する。

【解決手段】三次元ソリッドモデルに関する情報を取得し、取得した三次元ソリッドモデルに関する情報を記憶部に記憶する。三次元要素を積み上げる積み上げ方向を検出し、記憶してある三次元ソリッドモデルに関する情報に基づいて、検出した積み上げ方向と直交する面に三次元ソリッドモデルを投影した二次元投影形状を算出する。算出した二次元投影形状を一又は複数の領域に分割する。分割した領域について、三次元ソリッドモデルの積み上げ方向の構成に関する情報である積み上げ情報を生成し、分割した領域ごとに二次元メッシュを生成する。生成した二次元メッシュ及び生成した積み上げ情報に基づいて、三次元メッシュを生成する。

(もっと読む)

レイアウト検証装置、方法及びプログラム

【課題】LVS検証においてチップの一部にレイアウトの変更が発生した場合にレイアウト検証処理の負担を軽減すること。

【解決手段】レイアウト検証装置は、半導体集積回路のレイアウトを検証するものであり、論理回路の素子及び当該素子間の接続関係を定義した複数の素子情報を含む回路情報と、当該回路情報に基づき複数層のレイアウト領域が設計された第1のレイアウトデータと、を記憶する記憶部と、回路情報と第1のレイアウトデータとの比較検証においてエラーとなったことに起因して、当該第1のレイアウトデータのレイアウト領域が修正された第2のレイアウトデータを記憶部に格納する格納部と、記憶部を参照し、第1のレイアウトデータと第2のレイアウトデータとに基づいて、修正されたレイアウト領域である修正レイアウト領域を抽出する修正領域抽出部と、修正レイアウト領域と回路情報とを用いて再度の比較検証を行う比較検証部と、を備える。

(もっと読む)

回路部品移行装置、回路部品移行プログラムおよび回路部品移行方法

【課題】シンボルを引継いで回路部品を移行できる回路部品移行装置、回路部品移行プログラムおよび回路部品移行方法を提供する。

【解決手段】回路部品移行装置10は、特定部13aと、比較部13bと、登録部13cとを有する。特定部13aは移行元の回路部品に対応する移行先の回路部品を示す対応情報11aに基づき、移行対象の回路部品に対応する移行先の回路部品を特定する。比較部13bは特定された移行先の回路部品を表すシンボルと前記移行対象の回路部品を表すシンボルとの形状を比較する。登録部13cは比較の結果、同一の形状でない場合、移行先の回路部品を記憶する移行先部品情報11bに前記移行対象の回路部品を表すシンボルを特定された移行先の回路部品に関連付けて登録する。

(もっと読む)

半導体集積回路、半導体集積回路の設計方法及び設計装置並びにプログラム

【課題】セルベースの半導体集積回路において、異なるセル高さを有するセルを効率良く配置するための技術を提供する。

【解決手段】半導体集積回路が、基準ハイトセル30、マルチハイトセル40、VDD電源配線、VSS電源配線を備え、マルチハイトセルは、Y軸方向に延伸するVDD側電源供給配線5B、VSS側電源供給配線6Bを備え、基準ハイトセルの高さをa、マルチハイトセルの高さをb、VDD、VSS電源配線の幅をwとしたときに、VSS側電源供給配線は、少なくとも、マルチハイトセルの下端からw/2高さ方向に離れた位置とマルチハイトセルの下端からb−a−w/2高さ方向に離れた位置の間の高さ範囲をカバーするように設けられ、VDD側電源供給配線は、少なくとも、マルチハイトセルの下端からa+w/2高さ方向に離れた位置とマルチハイトセルの下端からb−w/2高さ方向に離れた位置の間の高さ範囲をカバーするように設けられる。

(もっと読む)

粘弾性体構造物の断面形状の設計装置、その方法及びそのプログラム

【課題】空気入りタイヤ等の粘弾性体構造物の断面形状を効率的に設計することができる設計装置を提供する。

【解決手段】タイヤの初期断面形状についてヒステリシス損失に基づく温度分布を求め(S2)、高温領域を変更対象領域として特定する(S3)。初期断面形状に対するレベルセット関数の分布を求め(S4)、初期断面形状の境界線上に仮想点列を設定する(S5)。レベルセット関数の分布に基づき、変更対象領域におけるレベルセット関数の値の高い領域が減るように仮想点列を移動させて(S6,S7,S8)、断面形状を更新し、更新した断面形状について温度分布を求め(S9)、求めた温度分布から高温領域の面積を求めて(S10)、その収束性を判定する(S11)。

(もっと読む)

半導体集積回路のレイアウト設計方法

【課題】SETUP時間とHOLD時間のどちらも満足させるタイミングの調整が可能な技術を提供する。

【解決手段】半導体集積回路の配置配線レイアウトを決定した後に、所定の信号線を伝搬するデータのタイミング情報に基づいて、タイミング違反を有する違反データの遅延情報を抽出する。その抽出された遅延情報に基づいて、タイミング違反を解消するための追加すべき容量値を算出する。また、違反データを伝搬する配線のレイアウト配置情報に基づいて、違反データを伝搬する配線の近傍の電源容量セルを検出する。また、算出された容量値に基づいて、検出された電源容量セルを、電源容量セルとレイアウト外形・電源/GND配線配置位置が同じ調整容量セルに置き換える。そして、置き換えた調整用容量セルのゲートと違反データを伝搬する配線とを接続して再配線を実行する。

(もっと読む)

半導体装置の開発支援装置、開発支援方法及び開発支援プログラム

【課題】半導体装置を容易に開発することが可能な半導体装置の開発支援装置、開発支援方法及びプログラムを提供する。

【解決手段】

設計評価装置3は、センサ2の測定信号を入力するアナログフロントエンド部100とMCU部200とを有する設計評価装置3であって、アナログフロントエンド部100の回路構成に対応したGUIを表示するGUI処理部301と、ユーザによるGUIの操作に基づいて、アナログフロントエンド部100の回路構成及び回路特性を設定する設定情報を生成し、MCU部200を介してアナログフロントエンド部100へ生成された設定情報を設定するレジスタ設定部302と、を備えるものである。

(もっと読む)

配線設計支援装置,配線設計支援プログラムおよび配線設計支援方法

【課題】配線設計に際し配線や配線容量の検討を高速かつ厳密に行なえるようにする。

【解決手段】配線経路生成部11が、2つの部品の各部品端子から各部品外部へ引出線を配線する処理に先立ち、2つの部品間で複数の信号線が配線される配線領域を概略的に示す配線経路を生成し表示部40に表示させる。配線経路生成部11によって配線経路が生成されると、詳細配線生成部12が、配線経路と配線規則とに基づき、各信号線を配線経路に沿って配線した詳細配線を生成し配線経路とともに表示部40に表示させる。

(もっと読む)

加入者ユニット密度を考慮したネットワーク設備配置用のプログラム、装置及びシステム

【課題】加入者エリアの密集度を考慮して収容効率を向上させた、ネットワーク設備配置の準最適解を得ることができるネットワーク設備配置用のプログラムを提供する。

【解決手段】本プログラムは、複数の加入者ユニットの位置をクラスタに分類し、これらクラスタの各セントロイドを、ネットワーク設備の設置候補位置として決定するクラスタリング処理手段と、クラスタに所属する加入者ユニット数とクラスタ面積とから算出された加入者ユニット密度に応じて、複数の最大許容線路長のうちの1つを選択する線路長設定手段と、決定されたセントロイドとクラスタに所属する加入者ユニットとを接続する線路長の全てが、選択された最大許容線路長以下であるか否かを判定する線路長判定手段と、線路長判定手段が真の判定を行った際、決定されたセントロイドをネットワーク設備の設置位置として確定するネットワーク設備配置手段として、コンピュータを機能させる。

(もっと読む)

31 - 40 / 7,589

[ Back to top ]