国際特許分類[G06F17/50]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | 電気的デジタルデータ処理 (228,215) | 特定の機能に特に適合したデジタル計算またはデータ処理の装置または方法 (34,028) | 計算機利用設計 (7,589)

国際特許分類[G06F17/50]に分類される特許

21 - 30 / 7,589

テスト設計手段選択装置及びテスト設計手段選択方法

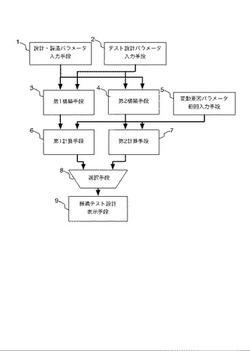

【課題】LSIの設計製造を通じて得られる利益を最大化するためのテスト設計を、適切に選択するためのテスト設計手段選択装置及びテスト設計手段選択方法を提供する。

【解決手段】テスト設計は、LSIのチップ面積、テスト実行時間、テストパターン生成時間、故障検出率の4つの項目に影響を与えるため、フルスキャン(FS)設計、組込み自己テスト(BIST)設計、テストデータ圧縮・展開(EDT)設計の3つのテスト設計についてこの 4つの関係をモデル化する。このモデルにより各テスト設計のトレードオフを捉え、設計製造環境に応じた設計製造コストを示し、その結果LSI 設計フローの早い段階で適切なテスト設計(DFT手法とそのパラメータ)を容易に選択できる。このテストモデルを用いることで、いくつかの設計製造環境に応じて適切にテスト設計を選択することができる。

(もっと読む)

部品カタログ作成支援装置、部品カタログ閲覧装置、プログラム、および部品カタログ作成支援方法

【課題】3次元の部品形状データを含むデータから、部品データのグループ化を自動的に行い、データを活用しやすくする。

【解決手段】3次元の部品形状データの組み合わせを含むアセンブリデータから、所定の形状を有する部品データを抽出する。抽出された各形状データについて、その形状データと共通の軸による形状部分をもつ部品を3次元の部品形状データから選択する。そして、抽出された各形状データについて、上記選択された部品をグループとして登録し、登録されたグループデータを部品カタログデータの一部として出力する。

(もっと読む)

チップ電源モデル生成装置および方法

【課題】低周波成分を有する電流波形データを容易に生成することのできるチップ電源モデル生成装置および方法を提供する。

【解決手段】実施形態のチップ電源モデル生成装置1は、簡易モデル生成部11が、チップを格子状に分割した矩形領域ごとに、レイアウトデータ1000から抽出した電源RCネットワークの簡略化および電流源の配置を行い、チップの電源系の簡易モデルを生成する。単周期分電流波形生成部12が、チップに集積された回路の動作モードごとに、上述の矩形領域ごとの1クロック周期分の電流波形を単周期分電流波形IWVとして生成する。パッド波形生成部13が、単周期分電流波形IWVを各電源パッドに分散させ、電源パッドごとのパッド波形PWVを生成する。波形結合部14が、指定されたモード変化およびクロック数の分、パッド波形PWVを結合する。

(もっと読む)

回路設計プログラム、回路設計方法、および回路設計装置

【課題】部品データの移動前後で、1対の回路基板の基板データでの論理的な接続関係を維持する。

【解決手段】回路設計装置が、移動対象である部品データIC1bの接続先ネット名NET5,6,9,10を、第1のコネクタ部品データCN1の第1の空き端子5〜8の接続先ネット名に設定する。回路設計装置が、部品データIC1bを第1の基板データC1から第2の基板データC2に移動させた場合、部品データIC1bの接続先ネット名NET5,6を第2の基板データC2内のネット名と異なるネット名に変換する。回路設計装置が、変換後の部品データIC1bの接続先ネット名A_NET5,6,NET9,10を、第1のコネクタ部品データCN1の第1の空き端子5〜8に対応する第2のコネクタ部品データCN2の第2の空き端子5〜8の接続先ネット名に設定する。

(もっと読む)

シミュレーション装置、シミュレーション方法、およびシミュレーションプログラム

【課題】ハードウェアとソフトウェアの協調動作のデバッグを効率的に行うこと。

【解決手段】シミュレーション装置100は、ソフトウェア101の実行中に、ハードウェアモデル102にアクセスする特定の関数が実行される場合、論理シミュレータ103側となるC−SVインターフェース104にて特定の関数の関数名を取得する。次に、C−SVインターフェース104は、関数名を記憶領域に格納する。また、論理シミュレータ103も、ハードウェアモデル102のシミュレーションの結果を記憶領域に格納する。波形ビューワ111は、記憶領域に格納されたシミュレーションの結果と関数名とを、時系列で対応付けて表示する。

(もっと読む)

動作合成方法、動作合成プログラム及び動作合成装置

【課題】動作合成により共有化するレジスタのビット幅を小さくすることが可能な動作合成方法、動作合成プログラム及び動作合成装置を提供する。

【解決手段】動作合成方法は、動作記述情報に基づいてスケジューリングしたCDFGを生成し、スケジューリングされたCDFGに基づいてライフタイムを変数毎に生成し(S301)、ライフタイム情報が時間軸上で重ならないm個の変数を選択し(S302)、第1のビット幅の第1の変数と、その他の変数内の第1のビット幅のビットとに、第1のレジスタを割り当て(S307)、その他の変数内の第1のビット幅のビット以外のビットに、第2のレジスタを割り当て(S308)、第1及び第2のレジスタを有する合成回路の回路情報を出力する。

(もっと読む)

メッシュ生成装置、メッシュ生成方法、及びコンピュータプログラム

【課題】可能な限り少ない要素数で有限要素解析が可能な三次元メッシュを生成することができるメッシュ生成装置、メッシュ生成方法、及びコンピュータプログラムを提供する。

【解決手段】三次元ソリッドモデルに関する情報を取得し、取得した三次元ソリッドモデルに関する情報を記憶部に記憶する。三次元要素を積み上げる積み上げ方向を検出し、記憶してある三次元ソリッドモデルに関する情報に基づいて、検出した積み上げ方向と直交する面に三次元ソリッドモデルを投影した二次元投影形状を算出する。算出した二次元投影形状を一又は複数の領域に分割する。分割した領域について、三次元ソリッドモデルの積み上げ方向の構成に関する情報である積み上げ情報を生成し、分割した領域ごとに二次元メッシュを生成する。生成した二次元メッシュ及び生成した積み上げ情報に基づいて、三次元メッシュを生成する。

(もっと読む)

レイアウト検証装置、方法及びプログラム

【課題】LVS検証においてチップの一部にレイアウトの変更が発生した場合にレイアウト検証処理の負担を軽減すること。

【解決手段】レイアウト検証装置は、半導体集積回路のレイアウトを検証するものであり、論理回路の素子及び当該素子間の接続関係を定義した複数の素子情報を含む回路情報と、当該回路情報に基づき複数層のレイアウト領域が設計された第1のレイアウトデータと、を記憶する記憶部と、回路情報と第1のレイアウトデータとの比較検証においてエラーとなったことに起因して、当該第1のレイアウトデータのレイアウト領域が修正された第2のレイアウトデータを記憶部に格納する格納部と、記憶部を参照し、第1のレイアウトデータと第2のレイアウトデータとに基づいて、修正されたレイアウト領域である修正レイアウト領域を抽出する修正領域抽出部と、修正レイアウト領域と回路情報とを用いて再度の比較検証を行う比較検証部と、を備える。

(もっと読む)

ノイズ解析モデル及びノイズ解析方法

【課題】解析対象回路内に設けられた素子のそれぞれに対する基板ノイズの影響を解析することができるノイズ解析モデル及びノイズ解析方法を提供すること。

【解決手段】本発明の一態様にかかるノイズ解析モデル100は、抵抗RS1〜RS4、抵抗RGB1〜RGB4及び接地抵抗RGNDを有する。抵抗RS1〜RS4は、ノイズ発生源から半導体基板を介して基板ノイズが伝搬する接続点1と、バックゲート直下の半導体基板中の点BG1〜BG4の間にそれぞれ接続される。抵抗RGB1〜RGB4は、バックゲート直下の半導体基板中の点BG1〜BG4とガードバンド4との間に接続される。接地抵抗RGNDは、ガードバンド4と接地電位との間に接続される。

(もっと読む)

設計支援装置

【課題】配線レイアウトのパターン形状に依存した効果をLPEに容易に取込む。

【解決手段】半導体集積回路の設計支援装置は、図形演算機能を有する第1の情報処理部110と、第2の情報処理部120とを備える。第1の情報処理部110は、レイアウト情報に含まれる各配線層のレイアウトパターンに対して図形演算を施すことによって、予め定める特定形状の配線パターンを抽出する。第2の情報処理部120は、製造プロセスに依存した配線または配線層間の絶縁層の厚みの設計値からのずれの大きさを、レイアウト情報から抽出した配線幅および配線密度の情報と、抽出された特定形状の配線パターンに関する情報とに基づいて予測する。そして、第2の情報処理部120は、予測した設計値からのずれの大きさを取り入れた配線および配線層間の絶縁層の厚みに基づいて、配線の寄生パラメータを抽出する。

(もっと読む)

21 - 30 / 7,589

[ Back to top ]