国際特許分類[G06F9/30]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | 電気的デジタルデータ処理 (228,215) | プログラム制御のための装置,例.制御装置 (15,360) | プログラム記憶方式を用いるもの,すなわちプログラムを受取りそして保持するために処理装置の内部記憶装置を用いるもの (15,354) | 機械語命令を実行するための装置,例.命令デコーダ (1,710)

国際特許分類[G06F9/30]の下位に属する分類

算術演算の実行を制御するもの

論理演算の実行を制御するもの (41)

単一ビット演算を制御するもの (4)

ロード,ストアまたはクリアの演算を制御するもの

移動,桁送りまたは回転の演算を制御するもの (20)

演算の拡張または修飾を伴うもの (38)

次位命令のアドレス指定,例.命令カウンタ値の増加,ジャンプ (110)

命令オペランドまたは演算結果のアドレシングまたはアクセシング (184)

命令の同時実行,例.パイプライン,ルック・アヘッド (952)

国際特許分類[G06F9/30]に分類される特許

101 - 110 / 361

処理装置、そのプログラムおよびコンピュータシステム

【課題】メモリの一部を一時的にゲストハードウエアのレジスタによって代行させる際に、ソースコード上での区別を不要にし、設計や検証の効率化を図る。

【解決手段】プロセッサとメモリとゲストハードウエアからなるシステムに組み込む転送機構と、プロセッサの実行する命令列を再構成するリアセンブラとを備える。リアセンブラは、ソースコードおよび該ソースコードからコンパイルされた第1のバイナリコードを取り込んで、転送機構の動作の手がかりとなり且つプロセッサの処理に影響を与えない標識命令を書き込んだ第2のバイナリコードを再構成してメモリにロードする。転送機構は、プロセッサが実行するメモリとの間の読み書き処理のうち、ゲストハードウエアが実行すべき処理で参照/代入される変数の読み書き処理を検出し、当該検出した読み書き処理について、ゲストハードウエアと所定のレジスタとの間で読み書きを実行させる。

(もっと読む)

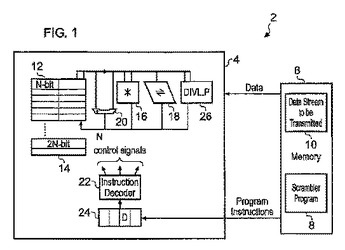

多項式データ処理演算

データ処理システム(2)は、多項式除算演算を実行するために処理回路構成(26)を制御する制御信号を生成する多項式除算命令DI−VL.PNに応答する命令復号器(22)を含んでいる。分母多項式は、多項式の最高次数項が、常に「1」の係数を有しているので、この係数は、分母値を格納するレジスタ内に格納される必要がないと見なして、レジスタ内に格納された分母値によって表わされる。従って、分母多項式は、分母値だけを格納するレジスタ内のビット空間で起こり得る次数より1つ高い次数を有することができる。多項式除算命令は、商の多項式及び剰余多項式をそれぞれ表わす商の値及び剰余値を戻す。  (もっと読む)

(もっと読む)

RISCアーキテクチャを有する8ビットマイクロコントローラ

【課題】完全かつ効率的な命令セットを提供するマイクロコントローラ設計を提供する。

【解決手段】8ビットRISCベースのマイクロコントローラは、汎用8ビット専用算術論理演算装置(ALU)22に加えて算術論理演算装置(ALU)を有する8ビットレジスタファイル20を含む。レジスタファイルはさらに、間接アドレス指定のため論理16ビットレジスタを提供するためレジスタの対を組合せるための手段を含む。専用ALUは、レジスタ対に対して所定の算術機能を加え、それによって、これがなければ汎用8ビットALUに課せられることとなる計算処理を緩和する、16ビットALUである。

(もっと読む)

情報処理装置

【課題】レジスタの特定ビットに対して不要に書き換えられないようにすること。

【解決手段】本発明の情報処理装置は、複数ビットを有するレジスタ24−4を備える周辺回路20−3と、データバス12と、データバス12を介してレジスタ24−4の複数ビットのうちの特定ビットに対してアクセスするCPU11と、を具備している。周辺回路20−3は、レジスタ24−4の特定ビットに対してアクセスする内部回路21と、CPU11と内部回路21とでレジスタ24−4の特定ビットに対するアクセスが競合しないように、CPU11又は内部回路21を優先する制御回路22と、を更に備えている。

(もっと読む)

X86の仮想機をサポートするRISCプロセッサ装置及び方法

X86の仮想機をサポートするRISCプロセッサ装置及び方法は開示される。RISCプロセッサは命令モジュール、デコーダ、固定小数点演算部分と浮動小数点演算部分を含んでいる。命令モジュールはX86の仮想機をサポートする命令セットを保存することに使われる;デコーダは仮想機の命令セットの命令をデコーディングするとき、命令の仮想機命令セットのモードを区別し、命令を区別された仮想機命令セットのモードに基づいて、デコーディングした後固定小数点演算部分または浮動小数点演算部分に出力することに使われる;固定小数点演算部分はデコーダの出力に基づき、仮想機命令セットの固定小数点命令について処理し、実行した結果を出力することに使われる;浮動小数点演算部分はデコーダの出力に基づき、仮想機命令セットの浮動小数点命令について処理し、実行した結果を出力することに使われる。  (もっと読む)

(もっと読む)

プロセッサ、メモリ装置、処理装置及び命令の処理方法

【課題】ゲストの命令をプロセッサで直接実行する場合、命令のトラップと特権モードの切り替えが頻繁に生じ、切り替えに伴うオーバーヘッドの増加によって、プロセッサの性能が低下する。

【解決手段】本発明の処理装置は、ゲストからの命令であるゲスト命令を取得し、トラップの判定処理及びVM環境の退出処理を行うVMトラップロジック122と、ゲスト命令を取得し、バッファリングの判定処理と命令保存処理を行うバッファリングロジック123とを備えるプロセッサ120と、構造体に、バッファリングロジック123が用いる、ゲスト命令のバッファリングを判定する条件であるバッファリング条件を記憶するメモリ130とを備えることとした。

(もっと読む)

縮小命令セット・コンピュータ・マイクロプロセッサーの構造

【課題】本発明は、改良された形態の、単純化された縮小命令セット・コンピューター(RISC)マイクロプロセッサーに関する。特に、スタック構造をとるマイクロプロセッサーに関する。

【解決手段】本発明のある態様では、マイクロプロセッサーシステムはマイクロプロセッシングユニットと入出力プロセッサー(IOP)とを含んでいる。大域メモリーユニットは中央処理装置及びIOPと連結されている。ある手段が、中央処理装置及びIOPの大域メモリーユニットへのアクセスを裁定する。ある形態では大域メモリーユニットは複数の大域レジスタを含んでいる。

(もっと読む)

データプロセッサ

【課題】命令コード空間に余裕のないRISC型のデータプロセッサにおける命令コード空間を縮小する。

【解決手段】フラグ生成命令数が多い場合に1命令が生成するフラグ数を増やすことによって、フラグ生成命令数の減少がフラグ使用命令数の増加を上回るようにすることにより命令数の削減を実現するという観点を基に、オペランドのデータサイズに応じた複数フラグを生成する命令を定義する。例えば、縮小命令セットコンピュータ型のデータプロセッサにおいて、複数データサイズのオペランドに対して演算処理が可能であって小さいデータサイズのオペランドに対する演算処理と等しい処理を大きいデータサイズのオペランドの下位側に対して行い演算処理されるオペランドのデータサイズに拘わらず夫々のデータサイズに対応するフラグ(newU,newT)を生成する命令を命令セットに加える。

(もっと読む)

プロセッサ

【課題】本発明は、多数の命令の実装と、コード効率向上を両立したプロセッサを提供しようとするものである。

【解決手段】デコーダ12bは、同一の命令コードで異なる命令を含む少なくとも第1、第2のデコードテーブル20を有し、前記第1、第2のデコードテーブルの一方に含まれる命令コードに基づき、フェッチされた命令コードをデコードする。選択手段21は、デコーダによりデコードされた命令コードが、第1、2のデコードテーブルを切り替える切り替え命令である場合、前記第1、第2のデコードテーブルの他方を選択する。

(もっと読む)

複数の命令セットの命令プリデコード

【課題】複数の命令セットの命令プリデコードを提供すること。

【解決手段】データ処理装置は、プリデコード命令を生成する機能を有すプリデコード回路10を備える。プリデコード命令は、命令キャッシュ20内に格納される。命令キャッシュ20からのプリデコード命令は、デコード回路45,50,46により読み出され、対応する処理動作を制御する制御信号を形成するために使用される。最初にフェッチされたプログラム命令は、複数の命令セットのうちのそれぞれ1つの命令セットに属すことができる。1つの命令セットからの命令は、プリデコード回路10により、複数の命令セットのうちの他の命令セットから取り出した対応する命令に共有される機能を表す共有フォーマットを有するプリデコード命令にプリデコードされる。このようにして、デコード回路の共有部分は、それらの異なる命令セット両方からの命令の共有機能に関して制御信号を生成できる。

(もっと読む)

101 - 110 / 361

[ Back to top ]