国際特許分類[H01L21/28]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 半導体装置またはその部品の製造または処理 (125,986) | 少なくとも一つの電位障壁または表面障壁,例.PN接合,空乏層,キャリア集中層,を有する装置 (97,574) | 不純物,例.ドーピング材料,を含むまたは含まない周期律表第IV族の元素またはA↓I↓I↓IB↓V化合物から成る半導体本体を有する装置 (83,040) | 21/20〜21/268に分類されない方法または装置を用いる半導体本体上への電極の製造 (9,571)

国際特許分類[H01L21/28]の下位に属する分類

電極用の導電または絶縁材料の析出 (3,372)

国際特許分類[H01L21/28]に分類される特許

4,121 - 4,130 / 6,199

銅配線用洗浄剤

【課題】銅配線の腐食抑制効果(銅腐食抑制効果)が優れ、かつ接触抵抗に影響を及ぼさない銅配線用洗浄剤を提供することを目的とする。

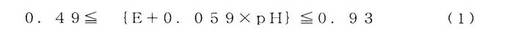

【解決手段】銅腐食抑制剤(RE)及び水(W)を含有してなり、25℃でのpHが3〜14であり、かつ式(1)を満たしてなることを特徴とする銅配線用洗浄剤を用いる。

【数1】

{式中、Eは25℃での酸化還元電位(V、vsSHE)、pHは25℃でのpHを表す。}

また、上記の銅配線用洗浄剤を半導体基板又は半導体素子に連続的又は断続的に供給して、銅配線を有する半導体基板又は半導体素子を洗浄することを特徴とする半導体基板又は半導体素子の洗浄方法を用いる。

なし

(もっと読む)

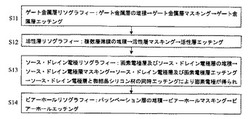

TFT−LCDアレー基板及びその製造方法

【課題】TFT−LCDアレー基板及びその製造方法を提供する。

【解決手段】TFT−LCDアレー基板の製造方法は、基板にゲートライン及びそのゲートラインと接続するゲート電極を形成し、前記ゲート電極にゲート絶縁層と半導体層とを形成し、前記半導体層にオーム接触層を形成することにより、基板にトランジスタ部を形成する工程と、前記工程で作製された基板に、ゲートラインとゲート電極と電気的に絶縁し、オーム接触層を介して前記半導体層の両側にオーム接触する透明画素電極層とソース・ドレイン電極金属層と順次堆積する工程と、作製された基板に、グレートーンマスクでマスキング及びエッチングを行うことにより、透明画素電極及びソース・ドレイン電極が同時に形成する工程とを含む。

(もっと読む)

半導体素子、半導体装置及びそれらの製造方法

【課題】チャネル領域の電位に対するゲート電極の制御性を向上させ、且つ電流駆動力が高くすることを可能にする。

【解決手段】半導体基板1に形成された、特定の導電型の不純物を含む半導体領域3と、半導体領域中に相互に向かい合う様に形成され、金属または金属と半導体領域をなす半導体との化合物を含むソースおよびドレイン領域4a、4bと、ソースおよびドレイン領域と、ソース領域とドレイン領域との間の半導体領域を覆うとともにソースおよびドレイン領域のそれぞれの一部を覆うように形成された絶縁膜5と、絶縁膜上に形成されたゲート電極6と、を有し、ソースおよびドレイン領域間の半導体領域の少なくとも一部の領域上に於ける絶縁膜とゲート電極との界面は、ソースおよびドレイン領域と半導体領域との接合部の上に於ける絶縁膜とゲート電極との界面よりも半導体領域側に存在する。

(もっと読む)

半導体素子

【課題】III族窒化物半導体を用いて形成され、優れた特性を有する半導体素子を提供する。

【解決手段】半導体素子10を、導電層1内において水平方向に主導通経路を有し、かつ、単位アノード部5uと単位カソード電極2uとを互いに隣接する形で横方向に集積化してなる、ショットキー型もしくはP−N接合型の、あるいはこれらが複合された横型ダイオード構造とする。導電層1は、好ましくは、III族窒化物層を積層し、積層面に二次元電子ガス層を形成させる態様によって構成される。導電層1を絶縁破壊電界が大きなIII族窒化物で構成することにより、電極間距離を小さくても高い絶縁破壊電圧を維持できるので、チップ面積あたりの出力電流が高い半導体素子が実現される。また、絶縁保護層6の設けた電極パッド層3が単位アノード部5uと単位カソード電極2uとの接合部における電界集中を緩和するので、より高い絶縁破壊電圧が実現される。

(もっと読む)

配線基板、表示装置及びそれらの製造方法

【課題】

導電層の損傷を防ぐことができる配線基板とその製造方法並びに表示装置を提供すること。

【解決手段】

本発明の一態様にかかる配線基板の製造方法は、Alを含む下層31、及びMoを含む上層32とをサイドエッチングするよう、レジストパターン33を介して下層31、及び上層32をエッチングする第1のエッチング工程と、第1のエッチング工程の後、上層32の側端部の表面を露出させるよう、レジストパターン33を後退させるアッシング工程と、アッシング工程の後、上層32の断面が順テーパ形状となるよう、後退されたレジストパターン33を介してエッチングする第2のエッチング工程とを備えるものである。

(もっと読む)

電界効果型トランジスタにおけるコンタクト抵抗を減少させるエピタキシャルシリコンゲルマニウム

凹んだエピタキシャルSiGeソース及びドレイン領域を有するnチャネルトランジスタのチャネル応力を選択的緩和する方法が記載されている。これにより、pチャネルトランジスタ内の歪みに影響を及ぼすことなくnチャネルトランジスタの電子移動度が増大する。SiGeは、シリサイドが形成されるときに抵抗が低くなる。  (もっと読む)

(もっと読む)

半導体装置及びその作製方法

【課題】良好な電気的接続を有する半導体装置を得ることを課題とする。

【解決手段】基板上に、下地膜と、島状半導体膜と、島状半導体膜中にチャネル形成領域と、ソース領域またはドレイン領域と、一導電型を付与する元素が添加されない接続領域と、ソース領域またはドレイン領域の一部の表面近傍と接続領域の表面近傍に形成されたシリサイド領域と、島状半導体膜上にゲート絶縁膜と、ゲート電極と、ゲート絶縁膜とゲート電極の側面に形成されたサイドウォールと、島状半導体膜、ゲート絶縁膜、ゲート電極及びサイドウォールを覆う層間絶縁膜と、層間絶縁膜中に形成されたコンタクトホールを介して、接続領域の表面近傍のシリサイド領域に電気的に接続されるソース電極またはドレイン電極とを有する半導体装置及びその作製方法に関する。

(もっと読む)

半導体装置の製造方法

【課題】簡略な工程で生産性良く半導体装置を製造することが可能な半導体装置の製造方法を得ること。

【解決手段】半導体基板上にゲート絶縁膜を介して複数のゲート電極を形成する工程と、ゲート電極を覆う絶縁膜を形成する工程と、ゲート電極の表面を露出させる工程と、半導体基板上に絶縁膜とのエッチング選択比が大きい金属膜を形成し、該金属膜をエッチングして少なくともゲート電極のうちシリサイド化を行わないゲート電極上に該ゲート電極のシリサイド化を防止するシリサイド化防止膜を形成する工程と、シリサイド化防止膜で覆われていないゲート電極上に、シリサイド膜形成用の金属膜を形成する工程と、ゲート電極と金属膜とを反応させ、該ゲート電極をシリサイド化する工程と、シリサイド膜形成用の金属膜のうち未反応の金属膜とシリサイド化防止膜とを除去する工程と、半導体基板上に層間絶縁膜を形成する工程と、を含む。

(もっと読む)

半導体装置の製造方法および半導体装置の設計支援システム

【課題】CMP後の金属膜を容易に平坦化できる技術を提供することができる。

【解決手段】半導体デバイス(被加工物)表面上に電気的に機能する溝状または孔状の配線パターン3(第1パターン)と、電気的に機能しない複数の溝状または孔状のダミーパターン4(第2パターン)を形成する工程と、配線パターン3上をメッキ法により、金属膜で被覆する工程と、被覆された金属膜をCMP法により研磨する工程とを有する半導体装置の製造方法であって、ダミーパターン4を形成する工程では、配線パターン3の溝幅に応じて、ダミーパターン4の溝幅および配置領域を決定し、選択的に形成させる。

(もっと読む)

半導体装置及びその製造方法

【課題】ニッケルシリサイド(NiSi)領域でのニッケルシリサイド凝集反応を抑制し、耐熱性を向上させた半導体装置及びその製造方法を実現する。

【解決手段】NチャネルMISトランジスタのニッケルシリサイド領域に、窒素(N2)イオンを注入し、PチャネルMISトランジスタのニッケルシリサイド領域に、二フッ化ホウ素(BF2)イオンを注入する。各トランジスタにおいて、窒素イオン及びホウ素イオンがそれぞれ注入されておれば、ニッケルシリサイド凝集反応が抑制される。よって、耐熱性を向上させた半導体装置が得られる。

(もっと読む)

4,121 - 4,130 / 6,199

[ Back to top ]