国際特許分類[H01L21/285]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 半導体装置またはその部品の製造または処理 (125,986) | 少なくとも一つの電位障壁または表面障壁,例.PN接合,空乏層,キャリア集中層,を有する装置 (97,574) | 不純物,例.ドーピング材料,を含むまたは含まない周期律表第IV族の元素またはA↓I↓I↓IB↓V化合物から成る半導体本体を有する装置 (83,040) | 21/20〜21/268に分類されない方法または装置を用いる半導体本体上への電極の製造 (9,571) | 電極用の導電または絶縁材料の析出 (3,372) | 気体または蒸気からの析出,例.凝結 (1,528)

国際特許分類[H01L21/285]に分類される特許

161 - 170 / 1,528

半導体装置の製造方法

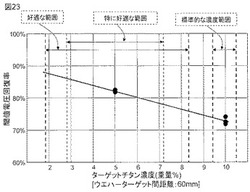

【課題】IGBT等においては、ドリフト領域やフィールドストップ領域における少数キャリアのライフタイムを制御して、スイッチング特性を改善するため、ウエハへの電子線照射が行われている。この電子線照射によって、デバイスの閾値電圧がシフトするため、電子線照射後に水素アニールを施すことにより、閾値電圧の回復を図っている。しかし、ボンディングダメージ等を低減するため、デバイス表面のモリブデン系バリアメタルをTiW系バリアメタルに変更すると、水素アニールによる閾値電圧の回復率が低下する問題が発生した。

【解決手段】本願発明はシリコン系半導体ウエハのデバイス主面側にパワー系絶縁ゲート型トランジスタの主要部を形成する半導体装置の製造方法において、デバイス主面上にTiW系のバリアメタルをスパッタリングにより形成するに際して、TiWターゲットのチタン濃度を、8重量%以下で、且つ、2重量%以上とするものである。

(もっと読む)

配線の形成方法及びその配線を有する表示装置の形成方法

【課題】従来のCMPを伴うダマシン法を用いた配線や電極の形成は、製造工程が煩雑であり高コスト化している。表示装置等の大型基板に配線形成を行うには平坦性等の高精度が要求されて好適せず、また研磨による配線材料の除去・廃棄量が多いという課題がある。

【解決手段】配線の形成方法及び配線を有する表示装置の形成方法は、基板上若しくは回路素子上に設けられた第1の金属拡散防止膜上に、金属シード層をCVD法により形成し、フォトレジストマスクを用いて選択的に無電解メッキ法、又は電解メッキ法により、金属配線層を形成し、金属シード層及び第1の金属拡散防止膜の不要領域除去と、金属シード層及び金属配線層及び第1の金属拡散防止膜の側面を含む表面を覆うように無電解メッキ法による第2の金属拡散防止膜の選択的な形成とにより配線及び電極を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】ダイオードと電極材料とのコンタクト抵抗を低減した半導体装置及びその製造方法を提供する。

【解決手段】実施形態によれば、半導体装置は、シリコンを含むダイオードと、前記ダイオードに対して積層された金属層及び可変抵抗膜と、前記ダイオードと前記金属層との間に設けられた、チタンとシリコンと窒素とを含む層と、を備えた。前記チタンと前記シリコンと前記窒素とを含む前記層は、前記窒素よりも前記チタンまたはチタンシリサイドを多く含む。

(もっと読む)

電子デバイス配線用Cu合金スパッタリングターゲット材、及び素子構造

【課題】酸化物反応層の寄生抵抗の低減を図り、動作特性の向上を図った電子デバイス配線用Cu合金スパッタリングターゲット材、及び素子構造を提供する。

【解決手段】TFT素子1は、a−Si膜5上に形成されたPドープn+a−Si膜6と、Pドープn+a−Si膜6上に形成された1nm以下のSi酸化膜7を有している。電極配線膜となるCu合金膜8が、Si酸化膜7上にスパッタリングにより形成されている。Cu合金膜8は、0.3〜2.0原子%のSn、In、Gaの金属のうち1種以上を含有する。

(もっと読む)

導電材埋め込み方法及び半導体装置の製造方法

【課題】 従来の方法と比較して、短時間で凹部の全体に導電材を埋め込むことができる技術を提供する。

【解決手段】 本願に係る導電材の埋め込み方法は、半導体装置の製造過程において表面に形成される凹部22に導電材を埋め込む方法に関する。この方法は、凹部22の少なくとも底面に露出する下地層10の表面に不純物24aを定着させる不純物定着工程と、不純物24aが定着した下地層10を利用して導電材をVLS成長させて、凹部の全体に導電材を埋め込むVLS成長工程とを有する。この方法では、VLS成長によって凹部22に導電材を埋め込むため、短時間で導電材を埋め込むことができる。

(もっと読む)

表示装置及びその作製方法

【課題】デジタル階調と時間階調とを組み合わせた駆動方法において、アドレス期間よりも短いサステイン期間を有する場合にも正常に画像(映像)の表示が可能であり、EL駆動用トランジスタが、劣化によりノーマリーオンとなった場合にも、信号線の電位を変えて動作を補償することの出来る画素を提供することを課題とする。

【解決手段】消去用TFT105のソース領域とドレイン領域とは、一方は電流供給線108に接続され、残る一方はゲート信号線106に接続されている。この構造により、EL駆動用TFT102のしきい値のシフトにより、ノーマリーオンとなった場合にも、ゲート信号線106の電位を変えることで、EL駆動用TFT102が確実に非導通状態となるように、EL駆動用TFT102のゲート・ソース間電圧を変えることを可能とする。

(もっと読む)

半導体装置の製造方法及び基板処理装置

【課題】低温での成膜において基板の侵食を抑制する半導体装置の製造方法及び基板処理装置を提供する。

【解決手段】ウエハ14を処理室92に搬入する第1の工程と、第1の原料としての固体金属66を収容する生成室62に、第2の原料としての塩素含有物と第3の原料としての励起ガスを供給し、プラズマ励起して金属塩化物を生成する第2の工程と、前記第2の工程により生成した金属塩化物を前記処理室92に供給する第3の工程と、第4の原料としての還元性ガスを前記処理室92に供給する第4の工程と、ウエハ14を前記処理室92から搬出する第5の工程と、を有する。

(もっと読む)

セルストリングの製造方法及びこれを含む不揮発性メモリ装置の製造方法

【課題】低抵抗特性を有するセルストリングの製造方法及びこれを含む不揮発性メモリ装置の製造方法を提供する。

【解決手段】本発明の不揮発性メモリ装置の製造方法は、半導体基板上に多数の層間絶縁膜、犠牲膜、及び半導体パターンを形成し、多数の層間絶縁膜及び犠牲膜は半導体基板と平行な第1方向に形成し、多数の半導体パターンは半導体基板に垂直である第2方向に形成し、多数の層間絶縁膜及び犠牲膜をパターニングして多数の開口部を形成し、多数の開口部を金属で満たし、多数の開口部に金属が満たされた半導体基板をアニーリングする。

(もっと読む)

スパッタリング装置、磁石部材移送装置、及びスパッタリング方法

【課題】スパッタリングターゲットの効率を向上させる。

【解決手段】一面が基板に対向するスパッタリングターゲットと、前記スパッタリングターゲットの他面に対向するように配置された磁石部材と、前記スパッタリングターゲットの中心部に対応する部分が前記スパッタリングターゲットの前記他面に平行な第1方向に沿って形成された直線部を備え、前記スパッタリングターゲットのエッジ部に対応する部分が前記スパッタリングターゲットに対して、前記第1方向と垂直な第2方向に遠くなるように形成された傾斜部を備えるガイドレールと、前記ガイドレールに対向し、前記第1方向に沿って形成されたスクリューラインと、前記磁石部材と弾性部材により連結されて、前記スクリューラインに沿って前記磁石部材を前記第1方向に運動させる連結ブロックと、を備える、スパッタリング装置。

(もっと読む)

シリコンデバイス構造、及びその形成に用いるスパッタリングターゲット材

【課題】シリコンデバイスの飽和移動度特性を向上する。

【解決手段】シリコン半導体膜上に、Pドープn+型アモルファスシリコン膜と、該Pドープn+型アモルファスシリコン膜上に形成された配線とを有するシリコンデバイス構造において、前記配線が、前記Pドープn+型アモルファスシリコン膜の表面に形成されたシリコン酸化膜と、銅合金膜とからなり、前記銅合金膜は、1原子%以上5原子%以下のMn及び0.05原子%以上1.0原子%以下のPを含む銅合金をスパッタリングにより形成した膜である。

(もっと読む)

161 - 170 / 1,528

[ Back to top ]