国際特許分類[H01L21/3205]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 半導体装置またはその部品の製造または処理 (125,986) | 少なくとも一つの電位障壁または表面障壁,例.PN接合,空乏層,キャリア集中層,を有する装置 (97,574) | 不純物,例.ドーピング材料,を含むまたは含まない周期律表第IV族の元素またはA↓I↓I↓IB↓V化合物から成る半導体本体を有する装置 (83,040) | 21/20〜21/26に分類されない方法または装置を用いる半導体本体の処理 (43,387) | 半導体本体上への絶縁層の形成,例.マスキング用またはフォトリソグラフィック技術の使用によるもの;これらの層の後処理;これらの層のための材料の選択 (16,787) | 絶縁層へ非絶縁層,例.導電層または抵抗層,の付着;これらの層の後処理 (7,286)

国際特許分類[H01L21/3205]の下位に属する分類

後処理 (649)

国際特許分類[H01L21/3205]に分類される特許

901 - 910 / 6,637

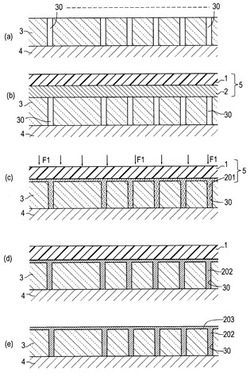

充填用基材及びそれを用いた充填方法

【課題】充填時の溶融温度が低く、凝固後は高い融点を確保することができ、しかも、作業操作性に優れた充填用基材及びそれを用いた充填方法を提供すること。

【解決手段】充填用基材5は、第1金属層21と第2金属層22とを含む金属層2を支持基体1の一面上に設けた構造になっている。第1金属層21は、その融点よりも低い温度で溶融可能なナノ金属粒子の集合したものでなり、第2金属層22は、その融点が第1金属層21の融点よりも低い金属粒子の集合したものでなる。充填用基材5の一面側を、微細空間30の開口する基板3の一面上に重ねる。そして、充填用基材5を加熱し、かつ、加圧F1して、金属層2の溶融物を微細空間30内に充填する。

(もっと読む)

積層構造体及びその製造方法、並びに多層配線基板、アクティブマトリクス基板及び画像表示装置

【課題】インクジェット法を用いた場合でも高いスループットで微細な導電層を有する積層構造体を製造可能な積層構造体の製造方法、並びに積層構造体、多層配線基板、アクティブマトリクス基板及び画像表示装置を提供する。

【解決手段】基板上に、同一パターンの高表面エネルギー部40を一定の間隔で周期的に配列しておき、インクジェット装置の主走査方向(X軸方向)における吐出ノズル1,2の間隔を、高表面エネルギー部40のパターン間隔と一致させて選択的に機能液の液滴dを滴下してソース電極230、ソース電極線290、ドレイン電極240となる導電層を形成する。

(もっと読む)

半導体集積回路装置および半導体集積回路装置の製造方法

【課題】TSVを形成した後の工程においては、Cuの拡散防止膜である絶縁膜形成後に、当該絶縁膜に割れが発生し、その後のエッチングやアッシングなどのパターン加工を行う工程において、露出したCuが変色する問題が発生する場合がある。これは、拡散防止膜の成膜工程における熱履歴によりCuが体積膨張したことが問題の要因と考えられる。このような、膜割れが発生した場合には、Cu拡散防止膜の機能破壊、TSV上部のCuの酸化による上部配線との導通不良等の種々の問題を誘発する。

【解決手段】本願の一つの発明は、貫通電極を有する半導体集積回路装置において、プリメタル配線層形成よりも後に貫通ビアを形成する場合において、貫通電極の上端に当たる層間絶縁膜の界面に、メタル拡散防止絶縁膜として、窒化シリコン系絶縁膜を使用し、それ以外の層間絶縁膜の界面に、メタル拡散防止絶縁膜として、炭化シリコン系の絶縁膜を使用するものである。

(もっと読む)

半導体集積回路装置

【課題】回路ブロックの面積を増大しないで容量セルを構成すること。

【解決手段】一対の拡散領域15、14を有する基板構造層10と、一対の電源配線41、42を有する配線層40と、第1電極21、誘電体22、第2電極23が積層するとともに、基板構造層10と配線層40との間にて、スタンダードセルが配置されるスタンダードセル領域1の外枠に沿って枠状に形成される容量20と、スタンダードセル領域1外において一方の電源配線41と一方の拡散領域15とを電気的に接続する第1基板コンタクト31と、スタンダードセル領域1外において他方の電源配線42と他方の拡散領域14とを電気的に接続する第2基板コンタクト32と、スタンダードセル領域1内において第1電極21と他方の拡散領域14とを電気的に接続する第1容量コンタクト34と、スタンダードセル領域1内において第2電極23と一方の電源配線41とを電気的に接続する第2容量コンタクト33と、を備える。

(もっと読む)

半導体装置の製造方法

【課題】新規な半導体装置の製造方法を提供する。

【解決手段】本実施形態に係る半導体装置の製造方法は、下層配線としてCu配線を含む多層配線と、前記Cu配線を形成するために用いられるCuアクセサリとが形成された半導体基板を、ポリイミド膜で覆う工程と、前記多層配線の最上層配線の表面および前記Cuアクセサリの表面を露出させる工程と、前記半導体基板をCu腐食防止剤の蒸気にさらして、前記最上層配線の表面および前記Cuアクセサリの表面にCu腐食防止膜を形成する工程と、前記最上層配線の表面に形成されたCu腐食防止膜を選択的に除去する工程と、前記Cuアクセサリの表面にCu腐食防止膜が形成された状態で、前記ポリイミド膜をベーク処理する工程とを有する。

(もっと読む)

半導体装置の製造方法

【課題】応力緩和機能を有するウェハレベルCSPと称される半導体装置において、外部電極の配置自由度が高い半導体装置の製造方法を提供する。

【解決手段】絶縁樹脂層を第1電極が形成された半導体ウェハ表面10に形成する工程、前記絶縁樹脂層の一部を除去して、開口径(D1)の開口部32を形成し、前記半導体ウェハ表面10の第1電極を露出させる工程、外部電極と前記第1電極を接続するための再配線層を前記絶縁樹脂層表面に形成する工程、前記再配線層の表面に再配線保護層を形成する工程、前記再配線保護層の一部を除去して、D2>D1となるような開口径(D2)の開口部32を形成し、前記第1電極と、前記外部電極を形成するための第2電極を露出させる工程、前記第1電極及び前記第2電極の表面にめっき層を形成する工程、前記めっき層を溶融することによって前記外部電極を形成する工程を含む、半導体装置の製造方法。

(もっと読む)

反射型液晶表示装置及びその製造方法

【課題】反射型液晶表示装置において、回路素子へ到達する入射光の量を低減するための技術を提供する。

【解決手段】回路素子に電気的に接続された、第1金属層112の上に、開口部127及び第1スルーホール126を有するようにパターニングされた第1絶縁層113を形成し、第1絶縁層に、開口部127に埋め込まれた金属部114及び第1スルーホール126に埋め込まれた第1プラグ115を形成した後、第2絶縁層116を形成する。第2絶縁層116の上に、開口部を有するようにパターニングされた第2金属層117を形成し、第2金属層の上に第3絶縁層119を形成した後、第2金属層117の開口部を通り且つ第1プラグ115の上面を露出させる第2スルーホール120を、第2絶縁層116及び第3絶縁層119に形成し、第2スルーホール120に埋め込まれた第2プラグ121と、第2プラグに接続された反射電極122とを形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】各半導体チップの電気接続を確実に行う。製造工程を簡略化することにより、製造コストを低減する。

【解決手段】半導体装置は、積層された3層以上の半導体チップと、各半導体チップ内を厚み方向に貫通するように設けられた貫通電極と、ランド部を有する。ランド部は、各半導体チップ内に貫通電極を囲むと共に貫通電極に接触するように設けられる。半導体装置の製造方法は、積層させた各ウェハを厚み方向に貫通すると共にランド部で周囲を囲まれるように、各ウェハ内にスルーホールを形成する工程と、スルーホール内に貫通電極を形成する工程を有する。

(もっと読む)

半導体装置の製造方法

【課題】製造工程数及び製造コストを削減しつつ、信頼性の高い半導体装置を製造することができる半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、下地層1上にTiを主成分とする密着層2を形成する工程と、密着層2上にWを主成分とする導電層3を形成する工程と、導電層3上にSiONを主成分とするハードマスク層4を形成する工程と、ハードマスク層4上にレジストパターン5を形成する工程と、レジストパターン5を保護膜とするエッチング処理により導電層3の一部3aを露出させる工程と、レジストパターン5及びハードマスク層4の残部4aを保護膜とするエッチング処理により密着層2の一部2aを露出させる工程と、その後、エッチング処理により下地層1の一部1aを露出させると共に、導電層3の残部3bを露出させる工程とを有する。

(もっと読む)

半導体デバイス及びマスク設計方法

【課題】アクティブフィーチャの容量カップリングを低減する。

【解決手段】本発明は、研磨ダミーフィーチャパターンの無差別な配置ではなく、研磨ダミーフィーチャパターンの選択的な配置を使用する。トポグラフィ変化の低周波数(数百ミクロン以上)及び高周波数(10ミクロン以下)の両方が検討された。研磨ダミーフィーチャパターンは半導体デバイス及び半導体デバイスの作製に使用される研磨条件に特に適合されている。集積回路をデザインする場合にはアクティブフィーチャの研磨効果が予測可能である。研磨ダミーフィーチャパターンが例図とに配置された後、局部的な(デバイスの全てではなく一部)レベルにおいて、及びさらに広域的なレベル(全デバイス、デバイスとは、レチクルフィールド、或いはさらにはウェハ全体に対応する)平坦性が検査される。

(もっと読む)

901 - 910 / 6,637

[ Back to top ]