国際特許分類[H01L21/3205]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 半導体装置またはその部品の製造または処理 (125,986) | 少なくとも一つの電位障壁または表面障壁,例.PN接合,空乏層,キャリア集中層,を有する装置 (97,574) | 不純物,例.ドーピング材料,を含むまたは含まない周期律表第IV族の元素またはA↓I↓I↓IB↓V化合物から成る半導体本体を有する装置 (83,040) | 21/20〜21/26に分類されない方法または装置を用いる半導体本体の処理 (43,387) | 半導体本体上への絶縁層の形成,例.マスキング用またはフォトリソグラフィック技術の使用によるもの;これらの層の後処理;これらの層のための材料の選択 (16,787) | 絶縁層へ非絶縁層,例.導電層または抵抗層,の付着;これらの層の後処理 (7,286)

国際特許分類[H01L21/3205]の下位に属する分類

後処理 (649)

国際特許分類[H01L21/3205]に分類される特許

961 - 970 / 6,637

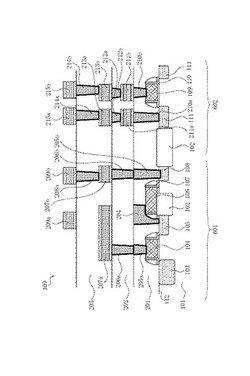

光電変換装置及びその製造方法

【課題】 層間絶縁膜の厚膜化を抑制しつつ、周辺回路領域の配線層数を増加させることのできる光電変換装置を提供する。

【解決手段】 画素領域と、画素領域よりも多くの配線層を有する周辺回路領域とが配された半導体基板と、半導体基板の上部に配された配線部とを有する光電変換装置において、配線部は、第1の配線層と接続する第1の層間絶縁膜に配されたプラグを周辺回路領域に有し、第1の配線層よりも上部に配された第2の配線層と接続する第1の層間絶縁膜に配されたプラグと第2の層間絶縁膜に配されたプラグとを画素領域に有し、

半導体基板に最も近接して配された配線層は、周辺回路領域において第1の配線層であり、画素領域において第2の配線層である。

(もっと読む)

半導体装置およびその製造方法

【課題】ストレスライナー膜によるチャネル領域の効果的な歪みによりキャリア移動度が向上した半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置100は、素子分離パターンを有する溝12を有する半導体基板2と、溝2の側面上に形成された側壁10と、半導体基板2の溝12に囲まれた領域に形成された、半導体基板2中にチャネル領域8を有するMOSFET3と、MOSFET3上および溝12内の側壁10上に連続して形成された、チャネル領域8に歪みを発生させるストレスライナー膜11とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体装置及びその製造方法に関し、バリアメタルの絶縁膜及びCuに対する密着性と、Cu拡散防止とを両立する。

【解決手段】 第1絶縁膜に設けた凹部の側壁に第2絶縁膜を形成し、第2絶縁膜の内側に順に第2絶縁膜との密着性が優れている第1の導電性バリア層、炭素を含有する第2の導電性バリア層、及び、Cu系埋込電極との密着性が優れている第3の導電性バリア層の3層構造のバリア層を介してCu系埋込電極を設けるとともに、前記第1の導電性バリア層と前記第2の導電性バリア層との界面と、前記第2の導電性バリア層と前記第3の導電性バリア層との界面に炭素混合領域を設ける。

(もっと読む)

表示装置、電子機器

【課題】アクティブマトリクス型の液晶表示装置の画面の大面積化を可能とするゲート電

極とゲート配線を提供することを第1の課題とする。

【解決手段】同一基板上に表示領域と、表示領域の周辺に設けられた駆動回路と、を有し

、表示領域は、第1の薄膜トランジスタを有し、駆動回路は、第2の薄膜トランジスタを

有し、第1の薄膜トランジスタと第2の薄膜トランジスタは、リンがドープされたシリコ

ンでなるゲート電極を有し、ゲート電極は、チャネル形成領域の外側に設けられた接続部

でアルミニウムまたは銅を主成分とする層とタンタル、タングステン、チタン、モリブデ

ンから選ばれた少なくとも1種を主成分とする層とを有する配線と電気的に接続する。

(もっと読む)

半導体装置及びその製造方法

【課題】信頼性の高い半導体装置を効率良く製造できるようにする。

【解決手段】半導体装置31は、回路基板1の所定位置に形成された電極パッド10を有し、電極パッド10には、半導体装置21のハンダバンプ26が接合されている。ハンダバンプ26は、半導体装置21の電極25上に形成され、そのハンダ材料には鉛フリーハンダが用いられている。回路基板1の電極パッド10は、複数の凸部10Aと溝10Bが形成されており、ハンダバンプ26は、その一部が電極パッド10の溝10Bを埋めるように入り込んでいる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】半導体装置の広幅の配線におけるディッシングの抑制と、抵抗の抑制と、を両立させる。

【解決手段】半導体装置100は、半導体基板1と、半導体基板1上に形成された配線層絶縁膜9と、を有している。配線層絶縁膜9には、第1配線用配線溝11と、第1配線用配線溝11よりも広幅の第2配線用配線溝12と、が形成されている。第1配線用配線溝11内には第1配線21が、第2配線用配線溝12内には第2配線22が、それぞれ形成されている。第2配線用配線溝12の底面の少なくとも一部分は、絶縁膜(例えば、絶縁膜4及びエッチングストッパー膜5)によって、第2配線用配線溝12の上端に達しない高さで第1配線用配線溝11の底面よりもかさ上げされた、かさ上げ部15となっている。

(もっと読む)

半導体装置およびその製造方法

【課題】 銅からなる柱状電極上に半田ボールが設けられた半導体装置において、半田ボール中の錫が柱状電極への拡散をより一層抑制することができるようにする。

【解決手段】 下地金属層8をメッキ電流路とした銅、ニッケルおよび半田の電解メッキをこの順で連続して行なうことにより、メッキレジスト膜25の開口部26内の上部金属層9のランド上面に柱状電極10、錫拡散抑制層11および酸化抑制層12をこの順で形成する。この結果、この半導体装置が大きな電流を扱う電源IC等であっても、酸化抑制層12を含む半田ボール14中の錫が柱状電極10に拡散するのをより一層抑制することができる。

(もっと読む)

半導体装置とその製造方法

【課題】半導体装置とその製造方法において、半導体装置の信頼性を高めること。

【解決手段】シリコン基板20と、シリコン基板20の上方に形成された層間絶縁膜38と、層間絶縁膜38の上に互いに間隔をおいて複数形成されたヒューズ41a、41bと、層間絶縁膜38の上であって、隣接するヒューズ41a、41bの間に形成されたダミーパターン41xと、ヒューズ41a、41bのうちの少なくとも一部とダミーパターン41xとを覆うと共に、下から順に塗布型絶縁膜46と窒化シリコン膜47とを備えたパシベーション膜48と有する半導体装置による。

(もっと読む)

半導体集積回路及びその製造方法

【課題】検査時におけるプロービングの機械的な力学的ストレスや、組立のワイヤ・ボンディングによる機械的な力学的ストレスによって発生する応力を緩和できる構成を有する半導体集積回路を提供する。

【解決手段】半導体集積回路は、半導体基板上(100)に形成されたパワー・トランジスタ(100A)と、パワー・トランジスタ(100A)の直上に形成され、パワー・トランジスタの第1の電極及び第2の電極として機能する複数の第1の金属パターン及び複数の第2の金属パターンと、複数の第1の金属パターンと電気的に接続する第1のバス(140)と、第2の金属パターンと電気的に接続する第2のバス(150)と、第1のバス(140)及び第2のバス(150)に1つづつ設けられたコンタクト・パッド(304)とを備え、第1のバス(140)及び第2のバス(150)の各々には、少なくとも1つのスリット(10a)が形成されている。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、スパッタ装置の処理能力を損なうことなく、スパッタに異常がないときは金属薄膜の反射率を面内で均一にすることができる半導体装置を提供することを目的とする。

【解決手段】本願の発明にかかる半導体装置の製造方法は、シリコン基板にスパッタ成長により金属膜を形成する第1スパッタ工程と、該第1スパッタ工程の後に該第1スパッタ工程よりも高いDCパワーでさらに金属膜をスパッタ成長させる第2スパッタ工程と、該第1スパッタ工程と該第2スパッタ工程の後に、該第1スパッタ工程および該第2スパッタ工程で形成された金属膜の反射率の均一性を測定する検査工程とを備えたことを特徴とする。

(もっと読む)

961 - 970 / 6,637

[ Back to top ]