国際特許分類[H01L21/8246]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 1つの共通基板内または上に形成された複数の固体構成部品または集積回路からなる装置またはその特定部品の製造または処理;集積回路装置またはその特定部品の製造 (40,275) | 1つの共通基板内または上に形成される複数の固体構成部品または集積回路からなる装置の製造または処理 (31,691) | 複数の別個の装置に基板を分割することによるもの (31,691) | それぞれが複数の構成部品からなる装置,例.集積回路の製造 (31,684) | 基板がシリコン技術を用いる半導体であるもの (27,844) | 電界効果技術 (17,660) | MIS技術 (17,448) | メモリ構造 (10,964) | リードオンリーメモリ構造 (7,638)

国際特許分類[H01L21/8246]の下位に属する分類

電気的にプログラムできるもの (4,399)

国際特許分類[H01L21/8246]に分類される特許

1,061 - 1,070 / 3,239

半導体記憶装置

【課題】レイアウト面積が小さな半導体記憶装置を提供する。

【解決手段】このMRAMでは、メモリブロックMB1用のDLドライバ10をトランジスタ20,21で構成し、メモリブロックMB2内のアクセストランジスタ19のサイズを適正化し、空いた領域にドライバトランジスタ21を配置する。また、メモリブロックMB2用のDLドライバ14をトランジスタ22,23で構成し、メモリブロックMB1内のアクセストランジスタ19のサイズを適正化し、空いた領域にドライバトランジスタ23を配置する。したがって、レイアウト面積が小さくなる。

(もっと読む)

磁性細線ユニット及び記憶装置

【課題】磁性細線の磁壁移動に要する電流を低減し、且つ磁壁保持時の状態を安定にする。

【解決手段】磁性細線の材料として、遷移温度を境に磁化容易軸が面内方向と垂直方向とで遷移する材料を用いる。この場合、磁性細線12の磁化容易軸が面内方向である第1の状態にあるときには、磁壁48を移動させるための電流供給が行われず、磁壁の移動に要する電流が小さい磁化容易軸が垂直方向である第2の状態にあるときにのみ、磁壁を移動させるための電流供給が行われるようなシーケンスを実行することにより、磁壁移動時に必要とする電流を低減することが可能である。また磁壁48を移動しない状態は第1の状態であり、磁壁の保持を安定化させることが可能である。

(もっと読む)

磁気ランダムアクセスメモリ

【課題】MRAMに効果の高い磁気シールド手段を提供する。

【解決手段】磁気ランダムアクセスメモリは、基板と、その基板の上方に形成された下部配線層と、その下部配線層の上方に形成された上部配線層と、下部配線層と上部配線層との間の第1高さに配置され、複数の孔が形成された磁気シールド層と、前記下部配線層と上部配線層との間に配置された磁気ランダムアクセスメモリ素子部とを備える。磁気ランダムアクセスメモリ素子部は、磁化が固定された磁化固定層と磁化が反転可能な磁化自由層とを備える複数の磁気ランダムアクセスメモリ素子と、複数の磁気ランダムアクセスメモリ素子の各々と下部配線層とを接続する下部接続部と、複数のランダムアクセスメモリ素子の各々と上部配線層とを接続する上部接続部とを備える。第1高さにおいて、複数の磁気ランダムアクセスメモリ素子はそれぞれ複数の孔の内部に配置される。磁気シールド層がメモリ素子の近くに配置されるため、高い磁気シールド効果が得られる。

(もっと読む)

強誘電体ゲート電界効果トランジスタ、それを用いたメモリ素子及び強誘電体ゲート電界効果トランジスタの製造方法

【課題】ゲート構造にIFI構造が含まれるMFS型メモリの強誘電体ゲート電界効果トランジスタにおいて、強誘電体膜の強誘電体特性及びトランジスタの電気特性の劣化を防止する。

【解決手段】Si基板1と、Si基板1上に少なくともHfSiON膜2、強誘電体膜3及びHfSiON膜4が、この順で積層されたゲート構造を有しており、HfSiON膜2及びHfSiON膜4は、強誘電体膜3を加熱処理によって形成する焼成温度で非晶質である。

(もっと読む)

磁気抵抗効果素子、磁気ヘッド、情報記憶装置、および磁気メモリ

【課題】更なる高記録密度化が実現可能な磁気抵抗効果素子を得る。

【解決手段】CoFeAlにSi又はGeが添加された磁性材料で形成され、内部の磁化の向きが固定されているリファレンス層143cと、リファレンス層143c上に非磁性材料で形成された非磁性層144と、この非磁性層144上に、CoFeAlにSi又はGeが添加された磁性材料で形成され、磁化の向きが、外部の磁界の向きに応じた向きに変化する自由磁化層145とを備えた。

(もっと読む)

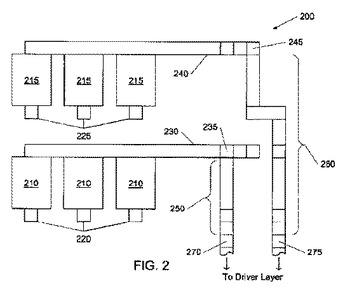

3Dメモリアレイの製造のためのX線用の共用マスクとY線用の共用マスク

デバイス層の数より少ない数のビット線マスクを用いて3次元メモリを製造する構造および方法を開示する。第1のビット線層を第1のデバイスレベルに形成するために第1のビット線マスクが使用される。第1のビット線層は複数の第1のビット線を含む。第1のビット線マスクは、第2のビット線層を第2のデバイスレベルに形成するためにも使用される。第2のビット線層は複数の第2のビット線を含む。第1のビット線および第2のビット線は、同じマスクパターンを使用するにもかかわらず、ビット線接続レベルへの異なる電気的接続を有する。  (もっと読む)

(もっと読む)

磁気抵抗効果素子

【課題】トップ型の積層構造で外部磁場耐性を向上させることができる磁気抵抗効果素子を提供する。

【解決手段】磁気抵抗効果素子42ではフリー層53上に絶縁層57が積層される。絶縁層57上にはリファレンス層61、結晶層62、非磁性層63およびピンド層64の積層体が積層される。こうした磁気抵抗効果素子42ではいわゆるトップ型の積層構造が確立される。この積層構造では、絶縁層57はフリー層53に受け止められることから、絶縁層57で凹凸の発生は回避される。しかも、リファレンス層61および非磁性層63の間には結晶層62が挟み込まれる。非磁性層63の結晶粒は結晶層62の結晶粒から成長する。非磁性層63では十分な結晶成長が確立される。その結果、リファレンス層61およびピンド層64の間で十分な磁気的結合力が確保される。この磁気的結合力の働きで、トップ型の積層構造にも拘わらず外部磁場耐性の低下は回避される。

(もっと読む)

不揮発性記憶装置およびその製造方法

【課題】強誘電体キャパシタの上部電極とセルトランジスタの拡散層を接続するための配線が、自己整合的に形成された不揮発性記憶装置およびその製造方法を提供する。

【解決手段】半導体基板の主面に、セルトランジスタ14と、強誘電体膜29を第1電極30および第2電極31で挟持し、第1電極30が第1コンタクトプラグ27の上面と接触した強誘電体キャパシタ13と、第2コンタクトプラグ28の上面に接触し、第1電極30と同じ材質の第1導電層32と、第1電極30、強誘電体膜29および第1導電層32の側面を覆うように第2絶縁膜26上に形成され、第1導電層32の上面を露出する第1開口を有する第3絶縁膜33と、第3絶縁膜33上に、一方34aが第2電極31と連続的に繋がり、他方34bが第1開口を通して第1導電層32に接続されるように形成され、第2電極31と同じ材質の第1配線34と、を具備する。

(もっと読む)

強誘電体ゲート有機電界効果トランジスタ、それを用いたメモリ素子及び強誘電体ゲート有機電界効果トランジスタの製造方法

【課題】強誘電体膜及びゲート電極間のリーク電流値を低減させると共に耐絶縁性を向上させる。

【解決手段】Si基板1と、Si基板1上に少なくともHfSiON膜2、強誘電体膜3HfSiON膜4及びC60膜6が、この順で積層されたゲート構造を有しており、強誘電体膜3の、HfSiON膜4と接する側の表面におけるRa値とRms値との和の第1絶対値が、HfSiON膜4の膜厚以下であり、かつ、HfSiON膜4の、C60膜6と接している側の表面におけるRa値とRms値との和の第2絶対値が3.0nm以下である。

(もっと読む)

液晶性有機半導体素子

【課題】電極材料/液晶性有機半導体(液晶物質)/電極材料の構成において、低電界で電荷注入を促進する。

【解決手段】2つの平板状電極1及び3と、液晶性有機半導体に強誘電性を付与した強誘電性液晶物質2とを備え、前記平板状電極は前記強誘電体液晶物質を挟み、前記平板状電極間に電圧を加えることにより前記強誘電性液晶物質を分極させ、電荷注入を促進させる液晶性有機半導体素子。

(もっと読む)

1,061 - 1,070 / 3,239

[ Back to top ]