国際特許分類[H01L21/8246]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 1つの共通基板内または上に形成された複数の固体構成部品または集積回路からなる装置またはその特定部品の製造または処理;集積回路装置またはその特定部品の製造 (40,275) | 1つの共通基板内または上に形成される複数の固体構成部品または集積回路からなる装置の製造または処理 (31,691) | 複数の別個の装置に基板を分割することによるもの (31,691) | それぞれが複数の構成部品からなる装置,例.集積回路の製造 (31,684) | 基板がシリコン技術を用いる半導体であるもの (27,844) | 電界効果技術 (17,660) | MIS技術 (17,448) | メモリ構造 (10,964) | リードオンリーメモリ構造 (7,638)

国際特許分類[H01L21/8246]の下位に属する分類

電気的にプログラムできるもの (4,399)

国際特許分類[H01L21/8246]に分類される特許

1,081 - 1,090 / 3,239

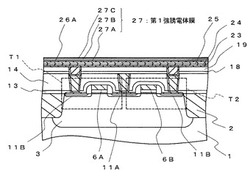

半導体装置の製造方法

【課題】信頼性の高い半導体装置を効率良く製造できるようにする。

【解決手段】シリコン基板1上に強誘電体キャパシタ37を形成する際、下部電極膜25の上に、アモルファス又は微結晶の酸化導電膜26を形成する。酸化導電膜26を熱処理により結晶化した後、強誘電体膜27の初期層27Aの形成時に酸化導電膜26を還元することにより、結晶粒が小さく且つ配向が整った第2の導電膜26Aを形成する。強誘電体膜27は、MOCVD法により形成し、その初期層27Aは第2の導電膜26Aの結晶配向に倣って成長する。これにより、強誘電体膜27の表面モフォロジが良好になる。

(もっと読む)

半導体記憶装置

【課題】フローティングボディ型のNMOSトランジスタを用い、そのボディに安定な電位を供給して正孔の蓄積に起因する特性劣化を防止可能な半導体記憶装置を提供する。

【解決手段】本発明の半導体記憶装置において、メモリセルMCに含まれるNMOSトランジスタQ0は、ゲート電極がワード線WLに接続され、一方のソース・ドレイン領域がビット線BLに接続されている。センスアンプ回路10に含まれるNMOSトランジスタQ10は、ゲート電極がビット線BLに接続され、一方のソース・ドレイン領域が所定の電位(グランド電位)に接続されている。NMOSトランジスタQ0、Q10は、フローティングボディ型のNMOSトランジスタであって、少なくともプリチャージ動作時に、ビット線BLに所定の電位(グランド電位)が供給されるので、ボディへの電位が安定化し、正孔の蓄積に起因する特性劣化を抑えることができる。

(もっと読む)

半導体記憶装置の製造方法および半導体記憶装置

【課題】ROMを形成する強誘電体メモリのダイナミック/スタティック・インプリント現象に対するデータ読み出しマージンを改善することのできる半導体記憶装置の製造方法および半導体記憶装置を提供する。

【解決手段】ROMを形成する強誘電体メモリに対し、ROMデータと逆極性のデータを書き込みを行って(工程S01)、所定時間のベーク処理を実行し(工程S02)、その後、ROMデータを書き込む(工程S03)。

(もっと読む)

矩形のボトム電極プレートを有するSTT−MRAMビットセル

スピントランスファトルク磁気抵抗ランダムアクセスメモリ(STT−MRAM)ビットセルが提供される。STT−MRAMは、矩形のボトム電極(BE)プレートおよび矩形のボトム電極(BE)プレート上の記憶素子を含んでいる。矩形のボトム電極(BE)プレートの幅と記憶素子の幅との間の差は、所定の最小間隔条件以上ある。ボトム電極(BE)プレートの幅は、活性層の幅または複数の金属層の幅と実質的に等しい。 (もっと読む)

半導体装置とその製造方法

【課題】基板からの高さが異なる導電層に、コンタクト窓を形成するDRAM等の半導体装置を提供する。

【解決手段】半導体基板16上に、第1導電パターン19、20と第1絶縁膜26、エッチング特性の異なる第2絶縁膜30、第3絶縁膜52、蓄積電極39、キャパシタ絶縁膜、対向電極40、エッチング特性の異なる第4絶縁膜41を形成し、第1導電パターン19,20上方に第1開口、対向電極40上方に第2開口を有するマスクを形成し、第1絶縁膜26をストッパとして、第1開口下方の第4絶縁膜41、第2絶縁膜30をエッチングし、第3絶縁膜52をストッパとして、第2開口下方の第4絶縁膜41、対向電極40をエッチングし、第1開口下方の第1絶縁膜26をエッチングして第1コンタクトホール44を形成し、第2絶縁膜30をストッパとして、第2開口下方の第3絶縁膜52をエッチングして第2コンタクトホール42を形成し、導電材を埋め込む。

(もっと読む)

対称なSTT−MRAMビットセルデザイン

対称なスピントランスファトルク磁気抵抗ランダムアクセスメモリ(STT−MRAM)ビットセルおよびSTT−MRAMビットセルアレイが示される。STT−MRAMビットセルは、ポリシリコン層、磁気トンネル接合(MTJ)記憶素子およびボトム電極(BE)プレートを含んでいる。 (もっと読む)

磁性材料の加工方法及び磁気ヘッドの製造方法

【課題】主磁極を従来よりも微細にすることができる磁性材料の加工方法を提供する。

【解決手段】基板1の上方に、磁性材料を有する磁性体層31を形成し、磁性体層31の上に、塩化された状態での沸点が磁性材料の塩化物の沸点に比べて高い金属を含むマスク35を形成し、塩素系ガスとの化学反応を含むドライエッチング法によりマスク35から露出している領域の磁性体層31をエッチングする工程により、磁気ヘッドの磁極を形成する工程を含む。

(もっと読む)

強誘電体メモリ

【課題】 製造工程および製造後において特性が劣化しにくく、かつ信頼性の高い強誘電体メモリおよびその製造方法を提供する。

【解決手段】 本発明にかかる強誘電体メモリ1000の製造方法は、(a)基体10の上方に下部電極層20、強誘電体層30、および上部電極層40を順次積層することにより強誘電体積層体を形成する工程と、(b)前記強誘電体積層体をパターニングすることにより、強誘電体キャパシタ100を形成する工程と、(c)前記強誘電体キャパシタ100を被覆する第1のバリア膜50を、物理的気相成長法により形成する工程と、(d)前記第1のバリア膜50を被覆する第2のバリア膜60を、化学的気相成長法により形成する工程と、を含む。

(もっと読む)

スピンメモリ

【課題】スピン注入書き込み時の電流値が低い磁気抵抗効果素子を提案する。

【解決手段】本発明の例に関わるスピンメモリは、磁化方向が不変の第1強磁性層、磁化方向が可変の第2強磁性層、及び、これらの間の第1非磁性層を有する磁気抵抗効果素子17と、第2強磁性層の磁化困難軸に対して、θ(45°≦θ≦90°)の方向に延び、長手方向の一端で磁気抵抗効果素子17を挟み込む下部電極16及び上部電極18と、下部電極16の長手方向の他端に接続されるスイッチ素子14と、上部電極18の長手方向の他端に接続されるビット線20とを備える。第2強磁性層の磁化反転は、第2強磁性層にスピン偏極した電子を与える書き込み電流を下部電極16と上部電極18との間に流すと共に、下部電極16及び上部電極18に流れるその書き込み電流により発生する磁界を用いて実行する。

(もっと読む)

共鳴トンネル磁気抵抗効果素子、磁気メモリセル及び磁気ランダムアクセスメモリ

【課題】共鳴トンネル磁気抵抗効果素子を用いた高速・低消費電力不揮発性メモリを提供する。

【解決手段】不揮発性磁気メモリに、共鳴トンネル磁気抵抗効果素子を装備し、共鳴準位に相当する電圧によりスピントランスファートルクによる書込み方式を適用する。共鳴トンネル磁気抵抗効果素子における障壁層は少なくとも2層3021,3022,3023で構成される。また、強磁性層に量子井戸形成層を隣接した構成を有する。

(もっと読む)

1,081 - 1,090 / 3,239

[ Back to top ]