国際特許分類[H01L23/12]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体または他の固体装置の細部 (40,832) | マウント,例.分離できない絶縁基板 (9,861)

国際特許分類[H01L23/12]の下位に属する分類

形状に特徴のあるもの (436)

材料またはその電気特性に特徴のあるもの (925)

国際特許分類[H01L23/12]に分類される特許

201 - 210 / 8,500

配線基板、及び半導体パッケージ

【課題】電源インピーダンスを低くすることや、インピーダンスマッチングをとることが容易な無機材料を用いた配線基板、及び前記配線基板上に半導体チップを搭載した半導体パッケージを提供すること。

【解決手段】本配線基板は、無機材料からなる基板本体と、前記基板本体を厚さ方向に貫通する平板状の第1電極と、前記基板本体を厚さ方向に貫通する平板状の第2電極と、を有し、前記第1電極と前記第2電極とは所定の間隔を隔てて対向し、前記第1電極と前記第2電極との間には、前記基板本体を前記厚さ方向に貫通する信号電極が設けられ、前記第1電極と前記第2電極の何れか一方はグランド電極であり、他方は電源電極である。

(もっと読む)

半導体装置の製造方法

【課題】より簡便に樹脂突起に形成された凹部の深さ(樹脂の除去量)を検査することができる半導体基板の製造方法を提供する。

【解決手段】本発明に係る半導体装置の製造方法は、第1の面を有する半導体基板と、前記第1の面に位置する第1電極及び第2電極と、前記第1の面に位置する第1樹脂突起及び第2樹脂突起と、前記第1樹脂突起の第1の部分を覆い、前記第1電極に接続された第1配線と、前記第1樹脂突起の第2の部分を覆い、前記第2電極に接続された第2配線と、を有する構造体を用意する第1工程と、前記第1樹脂突起の前記第1の部分と前記第2の部分の間の第3の部分の一部と、前記第2樹脂突起の少なくとも一部と、を同時にエッチングする第2工程と、前記第2工程後の前記第2樹脂突起の形状から、前記第2工程のエッチングにおける前記第3の部分の除去量が適正であるかを判断する第3工程と、を含む。

(もっと読む)

半導体装置用の中間部品および半導体装置用の中間部品の製造方法

【課題】小型,薄型タイプの半導体装置において、実装時の電極導通の信頼性向上を図るとともに、合わせて量産性にも配慮した半導体装置並びにその製造方法を提供することを目的とする。

【解決手段】半導体素子Sが搭載されるアイランド部2aと、1以上の電極部2bとを有し、上記アイランド部2a上に搭載した半導体素子Sと上記電極部2bとの間を電気的に接続した後樹脂封止して、アイランド部2aと電極部2bのそれぞれ裏面が樹脂層4の底面と同一平面で露出して構成される半導体装置において、上記アイランド部2aおよび電極部2bはそれぞれ電鋳により、裏面側の実装用金属薄膜11とこの上面に一体に積層されるリード層12の少なくとも二層構造とすることで、後工程で別途実装用のメッキを電極部露出面に形成する必要も無く、実装時の電極導通性,信頼性の向上を図ったものである。

(もっと読む)

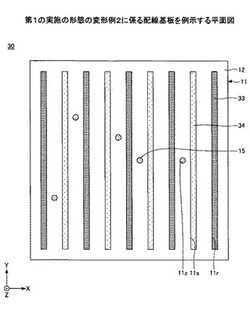

配線基板及びその製造方法、半導体パッケージ

【課題】接続信頼性が高く、狭ピッチの接続端子を形成可能な配線基板を提供する。

【解決手段】配線基板1は、無機材料からなる基板本体11に形成された配線パターン12と、前記配線パターンと電気的に接続され、半導体チップが搭載される外部接続端子15と、を備えた無機基板10と、絶縁層31、33、35と配線層32、34、36が積層された有機基板30と、熱膨張係数が前記無機基板よりも大きく前記有機基板よりも小さい材料からなる応力緩和層21と、前記応力緩和層を貫通する貫通配線22と、を備えた接合層20と、を有し、前記無機基板は、前記有機基板上に前記接合層を介して積層され、前記無機基板の配線パターンと前記有機基板の配線層とは、前記貫通配線を介して電気的に接続されている。

(もっと読む)

配線基板及びその製造方法、及び半導体装置

【課題】接続端子の狭ピッチ化を図ることのできる配線基板及びその製造方法、及び半導体装置を提供する。

【解決手段】配線基板11の表面となる第1の主面と、前記第1の主面とは反対側に位置する第2の主面とを備えた第1の絶縁層14と、前記第1の絶縁層を前記第1の主面側から前記第2の主面側に貫通して設けられた開口部14Aと、前記開口部内から前記開口部の壁面を経由して前記第2の主面上に延出して設けられ、一体に形成された導体層と、前記導体層を被覆して前記第2の主面に設けられた第2の絶縁層21と、前記第2の絶縁層に設けられたビア24と、を有し、前記開口部内に設けられた前記導体層の、前記第1の主面に露出する部分が、接続端子15となり、前記導体層の、前記開口部の壁面を経由して前記第2の主面上に延出して設けられた部分が、配線パターン16となり、前記ビアが、前記第2の主面上に延出した前記配線パターンに接続されている。

(もっと読む)

半導体装置、及びその製造方法

【課題】絶縁破壊が発生しにくい半導体装置及びその製造方法を提供する。

【解決手段】集積回路13と電気的に接続する電極14が位置する半導体基板10を用意する。半導体基板の前記第1の面11とは反対側の第2の面12において等方性エッチングを行い、第1内壁面を有する第1凹部を形成する。第1凹部内から前記半導体基板を貫通して電極に至り、第2内壁面22aを有する第2凹部を形成する。第2の面と第1内壁面によって形成された第1の角部、及び第1内壁面と第2内壁面によって形成された第2の角部を除去するエッチバック処理を行い、第2の面と第2内壁面とを連続する第1内壁面を形成する。角部を除去した後、少なくとも第1内壁面、及び第2内壁面を覆うように、電極とオーバーラップする位置に開口部65を有する絶縁層30を形成する。絶縁層を介して第2凹部内に充填され、電極と接続し、かつ第2の面から突出する導電部40を形成する。

(もっと読む)

実装基板および実装基板を用いた回路装置

【課題】大電流用および小電流用の導電パターンを形成しても、工程を複雑にせず、かつファインパターン化が可能な実装基板および実装基板を用いた回路装置を提供する。

【解決手段】絶縁樹脂から成るコア層52と、コア層52の表側に設けられた第1の導電パターン53と、コア層52の裏側に設けられた第2の導電パターン54と、第1の導電パターン53の中の大電流用の第1の電極64と第1の電極64と対応して設けられた第2の導電パターン54の外部電極73との間に設けられたVia72とを有し、第1の導電パターン53と第2の導電パターン54は、同じ膜厚で、大電流がVia72を介して外部電極73に流れるように、Via72の抵抗値を低くした。

(もっと読む)

半導体装置

【課題】従来の半導体装置では、良好な高周波特性を得ることができない問題があった。

【解決手段】本発明の半導体装置は、半導体チップ10と、半導体チップ10を搭載するリードフレームと、半導体チップ10とリードフレームとを接続するボンディングワイヤ11と、リードフレームのうち半導体チップ10が搭載される面の裏面側に設けられ、比誘電率が5以上の高誘電体層16と、を有し、リードフレームは、半導体チップに形成される半導体素子のソースと接続されるソース電極リード12と、ソース電極リード12とボンディングワイヤ11とが接続されるソースワイヤ接続点と、を含み、高誘電体層16は、リードフレームのうちソースワイヤ接続点の裏面を少なくとも含む領域に設けられる。

(もっと読む)

高周波部品及び通信装置

【課題】小型化を図った高周波部品および通信装置を提供する。

【解決手段】複数の誘電体層を積層してなる積層基板に高周波信号処理回路を備えた高周波部品であって、高周波信号の入力、出力端子および高周波信号処理回路の複数の電源端子を含む端子群が積層基板の一方の主面に形成されており、積層基板を構成する誘電体層には、インダクタンス素子用等のパターン電極が構成され、一端がそれぞれ電源端子に接続された複数の電源ラインは、誘電体層1に形成されたビア電極を介して高周波信号処理回路が有する少なくとも一つの半導体素子に接続され、複数の電源ラインのうち少なくとも二つの電源ラインは、それぞれ、隣接する二以上の誘電体層1にわたって積層方向から見て重なるように形成されたビア電極列2を有し、少なくとも二つの電源ラインのビア電極列2は、隣接する誘電体層間において、他の導体パターンを介さずに近接している。

(もっと読む)

半導体装置

【課題】半導体パッケージを実装基板から取り外すリペアが容易であって、半導体パッケージと実装基板との接続部の耐衝撃性を向上させることができる半導体装置を提供する。

【解決手段】半導体装置100は、半導体素子4が接続された半導体パッケージ1と、実装基板2とがはんだバンプ3を介して電気的及び機械的に接続されてなり、半導体パッケージ1は、半導体素子4が接続されるとともに実装基板2と接続される半導体パッケージ用配線板5を有し、半導体パッケージ用配線板5に形成された電極パッド22のコア層11側には第1応力緩和層21が配置されており、実装基板2に形成された電極パッド33の層間絶縁層31側には第2応力緩和層34が配置されており、第1応力緩和層21の25℃の弾性率が2.5GPa以下であり、第2応力緩和層34の25℃の弾性率が3GPa以下かつ第2応力緩和層34の平面方向の25℃の熱膨張係数が8×10-6/℃以下である。

(もっと読む)

201 - 210 / 8,500

[ Back to top ]