国際特許分類[H01L23/522]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体または他の固体装置の細部 (40,832) | 動作中の装置内の1つの構成部品から他の構成部品へ電流を導く装置 (7,814) | 半導体本体上に分離できないように形成された導電層及び絶縁層の多層構造からなる外部の相互接続を含むもの (2,851)

国際特許分類[H01L23/522]の下位に属する分類

適用できる相互接続を有するもの

相互接続構造のレイアウト

材料に特徴のあるもの (313)

国際特許分類[H01L23/522]に分類される特許

101 - 110 / 2,538

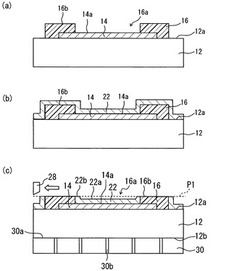

半導体装置の製造方法

【課題】切削又は研削加工を用いつつ、低コストで金属電極を形成することができる半導体装置の製造方法を提供する。

【解決手段】半導体基板12の主面12aに下地電極14を形成する工程と、下地電極を覆う保護膜16を形成するとともに、該保護膜に下地電極を露出させる開口部16aを形成する工程と、保護膜及び開口部から臨む下地電極の表面を覆うように第1金属膜22を形成する工程と、第1金属膜が形成された半導体基板を、裏面12bを搭載面として吸着ステージ30に吸着固定した状態で、吸着ステージと平行に設定された基準面上P1に位置する保護膜の部分及び第1金属膜の部分を、切削により除去して、第1金属膜をパターニングする工程と、パターニング工程後、裏面から半導体基板を研削し、半導体基板の厚さを所定厚さまで薄くする工程とを備える。

(もっと読む)

半導体装置の製造方法

【課題】貫通電極を有する半導体装置の製造方法において、埋設導電部間のショートが起き難くすること。

【解決手段】半導体素子を有する素子領域と貫通電極が形成される貫通電極領域とを有する基板の上に第1絶縁膜を形成し、前記素子領域上の前記第1絶縁膜に凹部を形成し、前記貫通電極領域上の前記第1絶縁膜にダミー凹部を形成し、前記第1絶縁膜上、前記凹部内、および前記ダミー凹部内に第1導電材を形成し、前記第1導電材および前記第1絶縁膜の上部を研磨して、前記凹部内に導電部を形成すると共に前記ダミー凹部内にダミー導電部を形成し、前記貫通電極領域上の前記第1絶縁膜および前記貫通電極領域をエッチングして前記基板内に至る貫通電極ホールを形成した後、前記貫通電極ホール内に第2導電材を形成し、前記貫通電極ホール内に形成された第2導電材が露出するまで前記基板の裏面を研磨して、前記貫通電極を形成すること。

(もっと読む)

半導体ウエハ及び半導体装置並びに半導体装置の製造方法

【課題】ダイシング工程におけるチッピング不良を低減させる。

【解決手段】一面側に複数の回路素子3が形成され、この回路素子が形成された領域間に第一スクライブライン領域R1が設けられたウエハ状の半導体基板2と、この半導体基板の他面2bから半導体基板の一面2aまで貫通する貫通孔7と、この貫通孔の内面及び半導体基板の他面側に形成された絶縁膜5と、この絶縁膜上に形成された配線6とを備えた半導体ウエハにおいて、半導体基板の他面側に形成された絶縁膜に、第一スクライブライン領域に沿って絶縁膜が離間した領域である第二スクライブライン領域R2が設けられている半導体ウエハを提供する。

(もっと読む)

半導体装置

【課題】Low−k膜を層間絶縁膜として用いた半導体装置であっても、ダイシング時に発生するクラックがシールリング部へ伝播するのを抑制し、半導体装置の信頼性を向上する技術を提供する。

【解決手段】ダイシング領域側の各層にダミービア125,135,145,155,165を形成する。ダミービア125,135,145,155,165は上面からみて、縦横に等間隔に配置、あるいは千鳥配置されるように形成する。ダイシング時にクラックが発生しても、ダミービア125,135,145,155,165によって、クラックがシールリング部190にまで伝播するのを抑制することができる。その結果、回路形成領域の吸湿耐性を向上させ、信頼性の劣化を防止することができる。

(もっと読む)

半導体磁気記憶装置

【課題】磁気記憶素子を構成する層を、周辺回路部内で有効に活用する。

【解決手段】実施形態によれば、半導体磁気記憶装置は、セルトランジスタを含むセル部と、周辺トランジスタを含む周辺回路部とが形成された半導体基板を備える。さらに、前記装置は、前記セル部内に配置され、下部電極と、前記下部電極上に形成された電極間層と、前記電極間層上に形成された上部電極とを含む磁気記憶素子を備える。さらに、前記装置は、前記周辺回路部内に配置され、前記下部電極を形成している第1の層と、前記電極間層を形成している第2の層と、前記上部電極を形成している第3の層とを含む構造体を備える。さらに、前記装置は、前記第1の層に電気的に接続された第1及び第2のプラグを備える。さらに、前記第1の層は、前記第1のプラグと前記第2のプラグを電気的に接続する配線として機能する。

(もっと読む)

半導体装置の製造方法

【課題】アライメント光によるアライメントマークの検出感度を向上させて、低コストで貫通孔の位置合わせを行う。アライメントマークの誤検出を防ぐ。また、アライメントマーク検出時のアライメント光の露光マージンを大きくして、微細化に対応可能な半導体装置の製造方法を提供する。

【解決手段】半導体基板の非有効ショット領域において、半導体基板の主面又は主面よりも上方にアライメントマークを形成する。半導体基板の裏面の方から、アライメントマークが形成された位置に対応する開口を形成する。半導体基板内に形成されている半導体装置の構成パターンと露光用マスクパターンとの位置合わせをして、有効ショット領域の半導体基板内に貫通孔を形成する。

(もっと読む)

不揮発性記憶素子及び不揮発性記憶装置並びにそれらの製造方法

【課題】良好な電気的特性が得られる不揮発性記憶素子及びその製造方法を提供する。

【解決手段】第1の配線103と、第1の配線103上に形成され、第1の配線103に接続される第1のプラグ107及び第2のプラグ108と、第1電極109、第2電極113、及び抵抗変化層112を有し、第1のプラグ107上に形成され、第1電極109が第1のプラグ107と電気的に接続されている抵抗変化素子114と、抵抗変化素子114上に形成され、第2電極113と電気的に接続されている第2の配線119と、第2のプラグ108上に形成され、第2のプラグ108と電気的に接続されている第3の配線121とを備え、第1のプラグ107の上面と第2のプラグ108の上面とが略同一平面内に形成され、かつ第2の配線119の上面と第3の配線121の上面とが略同一平面内に形成されている。

(もっと読む)

配線レイアウトの設計方法、半導体装置及び配線レイアウトの設計を支援するプログラム

【課題】高集積化を図ることができる配線レイアウトの設計方法、半導体装置及び配線レイアウトの設計を支援するプログラムを提供する。

【解決手段】実施形態に係る配線レイアウトの設計方法は、側壁法によって形成されるレイアウトの設計方法であって、第1の方向に延び、前記第1の方向と交差する第2の方向に第1の周期で配置された複数本の第1のパターン、及び、前記第1の方向に延び、前記第1のパターン間の中央にそれぞれ配置された複数本の第2のパターンが設けられたベースパターンを用意する工程と、1本の前記第2のパターンを挟んで隣り合う2本の前記第1のパターン間に、前記第2の方向に延び、前記2本の第1のパターン同士を接続すると共に、前記1本の第2のパターンを前記2本の第1のパターンと接しない2つのパターンに置き換える工程と、を備える。

(もっと読む)

半導体装置の製造方法

【課題】基板を貫通する電極の形成に適用できる新規な半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板上に半導体素子を形成する工程と、半導体基板に孔を形成する工程と、半導体素子の上方と孔の内壁および底を覆うように絶縁膜を形成する工程と、異方性エッチングにより、半導体素子の上方と孔の底の絶縁膜を除去する工程と、孔の底に金属拡散防止膜を形成する工程と、孔に導電膜を埋める工程とを有する。

(もっと読む)

半導体集積回路、半導体集積回路の設計方法、および半導体集積回路の設計装置

【課題】配線層に形成される信号配線をなるべく迂回させずに配線できるように電源スタックビアが配置された半導体集積回路を提供すること。

【解決手段】半導体集積回路は、第1の方向に延伸された第1,第2の下層電源配線11A,11Bと、第2の方向に延伸された第1,第2の上層電源配線12A,12Bと、上層,下層電源配線を接続させる第1,第2接続部3A,3Bと、を備え、第1,第2接続部は、第1,第2の接続用配線26A,26Bと、第1,第2の位置変換用配線27A,27Bと、第1,第2の上側ビア28A,28Bと、を有して構成され、第1,第2の接続用配線は、第2の方向に沿った同一ライン上に配置され、第1,第2の位置変換用配線は、第1,第2の接続用配線を第2の方向に沿って延長した領域内に形成され、第1,第2の上側ビアは、第1の方向に沿った同一ライン上となる位置に配置される。

(もっと読む)

101 - 110 / 2,538

[ Back to top ]