国際特許分類[H01L23/532]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体または他の固体装置の細部 (40,832) | 動作中の装置内の1つの構成部品から他の構成部品へ電流を導く装置 (7,814) | 半導体本体上に分離できないように形成された導電層及び絶縁層の多層構造からなる外部の相互接続を含むもの (2,851) | 材料に特徴のあるもの (313)

国際特許分類[H01L23/532]に分類される特許

41 - 50 / 313

半導体装置

【課題】微細化が可能な半導体装置を提供する。

【解決手段】実施形態に係る半導体装置は、上面に、一方向に延び上方に突出した複数本のアクティブエリアが形成された半導体基板と、前記アクティブエリア間のトレンチの下部に埋め込まれた素子分離絶縁体と、第1の絶縁材料からなり、前記素子分離絶縁体の直上域に配置され、下部が前記トレンチ内に配置され、上部が前記アクティブエリアの上端よりも上方に突出した絶縁ブロックと、前記第1の絶縁材料とは異なる第2の絶縁材料からなり、前記半導体基板及び前記絶縁ブロックの上方に設けられた層間絶縁膜と、前記層間絶縁膜内に形成され、下端が前記アクティブエリアの上面に接続されたコンタクトと、を備える。前記コンタクトにおける前記絶縁ブロックの直上域に位置する部分の下面は、前記コンタクトにおける前記アクティブエリアの直上域に位置する部分の下面よりも上方に位置している。

(もっと読む)

トップゲート型アクティブマトリックス基板、およびその製造方法

【課題】データ配線が銀や銀合金により形成されており、またデータ配線に、ゲート絶縁層によって被覆されておらずむき出しとなっている部分があった場合でも、当該むき出しとなっている部分でマイグレーション現象が生じることがないトップゲート型アクティブマトリックスを提供する。

【解決手段】基材と、前記基材上に直接または間接的に形成された、ソース電極、ドレイン電極、半導体層、ゲート絶縁層、ゲート電極、層間絶縁層、画素電極、および前記ソース電極と接続したデータ配線と、を有するトップゲート型アクティブマトリックス基板において、前記ソース電極と前記データ配線をともに銀または銀合金で形成し、前記ゲート電極を銀または銀合金以外で形成し、前記データ配線においてむき出しとなっている部分をゲート電極と同じ材質からなる被覆層によって被覆する。

(もっと読む)

半導体装置及びその製造方法

【課題】柱状半導体層の幅を広く維持することができる半導体装置を提供すること。

【解決手段】半導体装置は、一つの直線上に順に形成された、第1、第2及び第3の柱状半導体層と、第2及び第3の柱状半導体層の間の空間であって第2及び第3の柱状半導体層の側面に夫々設けられた第1及び第2のゲート電極と、第1及び第2の柱状半導体層の間の空間及び第2及び第3の柱状半導体層の空間に埋め込まれた層間絶縁膜とを有する。層間絶縁膜は、第1及び第2の柱状半導体層の間の空間内であってゲート電極を介することなく第1及び第2の柱状半導体層の側面に形成され、第2及び第3の柱状半導体層の間の空間内であって第1及び第2のゲート電極を介して第2及び第3の柱状半導体層の側面に形成されている。

(もっと読む)

半導体装置の製造方法、半導体装置

【課題】微細な溝部の内部に隙間無く導電材料を埋め込み、導電性に優れた配線を得ることが可能な半導体装置の製造方法および半導体装置を提供する。

【解決手段】溝部12を除いた基体11の一面11a、即ち溝部12の頂面にエッチングカバー層14を形成する。エッチングカバー層14は、例えば、Ta,Tiまたはこれらを含む合金から構成される。エッチングカバー層14の形成は、例えば、スパッタリング法を用いることが好ましい。

(もっと読む)

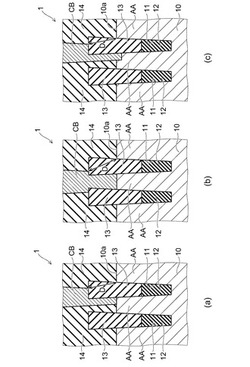

半導体装置の製造方法

【課題】 エアギャップ形状を容易に制御することが可能な半導体装置の製造方法を提供する

【解決手段】 本発明では、半導体基板1上に所定の間隔でライン2とスペース3が交互に配置されたライン・アンド・スペース構造体を形成する工程と、前記ラインの上面及び前記スペースの上面を連続して覆う第1の絶縁膜5を形成する工程と、前記スペース上方の前記第1の絶縁膜の一部をエッチングし、開口部6を形成する工程と、前記第1の絶縁膜及び前記開口部を連続して覆う第2の絶縁膜7を形成し、前記スペースと前記開口部による中空部を形成する工程とを有していることを特徴とする半導体装置の製造方法が得られる。

(もっと読む)

半導体装置の製造方法

【課題】電気めっき装置のハードウェアトラブルを低減しながら、銅めっき膜の均一性を保つ。

【解決手段】自動分析器14は、電極16,17間に印加されている電圧を検出し、その電圧値が設定電圧範囲内であるか否かを判断する。検出した電圧値が、設定電圧範囲の下限値よりも低い場合、自動分析器14は、検出した電圧値に基づいて、基本液の不足量を算出し、バルブ11を制御して不足分の基本液を補充した後、めっき液タンク6内のめっき液が規定量を保つようにバルブ13の動作制御を行い、めっき液を廃液する。また、検出した電圧値が設定電圧範囲の上限値よりも高い場合、検出した電圧値に基づいて基本液の超過量を算出し、バルブ12を制御して基本液の濃度が規定範囲内となるように純水をめっき液タンク6に補充してめっき液を薄めた後、バルブ13を制御して規定量を保つようめっき液を廃液する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】半導体装置の反りを抑制し、且つ、その反りの経時変化を抑制する。

【解決手段】半導体装置は、基板と、基板上に形成された多層配線層と、を有し、多層配線層は、配線と、配線を覆う層間絶縁膜と、をそれぞれ有する複数層の配線層を有する。少なくとも何れか1つの層間絶縁膜(例えば、層間絶縁膜27、30)は、第1絶縁膜41と第2絶縁膜42とを有する。第1絶縁膜41は、基板を第1方向(例えば下に凸)に反らせる応力を基板に与える。第2絶縁膜42は、第1絶縁膜41よりも表層側に形成され、第1絶縁膜41よりも吸湿性が低く、基板を第1方向に対する反対方向(例えば上に凸)に反らせる応力を基板に与える。

(もっと読む)

半導体装置の製造方法、半導体装置

【課題】微細な溝部の内部に隙間無く導電材料を埋め込み、導電性に優れた配線を得ることが可能な半導体装置の製造方法および半導体装置を提供する。

【解決手段】バリア層(バリアメタル)13を覆うようにライナー層14が形成されている。ライナー層14は、Ni(ニッケル)から構成される。ライナー層14は、このライナー層14の内側に形成されるCu(銅)からなる導電体15に対する濡れ性を高め、かつ、溝部12の内側の平滑性を高める。

(もっと読む)

半導体装置及びその製造方法

【課題】 エレクトロマイグレーション耐性及び信頼性に優れた半導体装置及びその製造方法を提供する。

【解決手段】 基板上に絶縁膜を形成する工程と、前記絶縁膜をエッチングして配線溝を形成する工程と、前記配線溝内に銅膜を形成し、銅配線を形成する工程と、前記銅配線及び前記絶縁膜の表面を平坦化する工程と、平坦化された前記銅配線及び絶縁膜上に金属膜を形成する工程と、酸素を含んだ雰囲気中で加熱を行うことにより前記銅配線上の前記金属膜と前記銅配線とを選択的に反応させて合金膜を形成するとともに前記絶縁膜上の前記金属膜を酸化して絶縁性の膜に変化させる工程と、前記合金膜及び前記絶縁性の膜上にブロック膜を形成する工程とを備えた半導体装置の製造方法。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】メモリセル積層構造間に空隙を有する不揮発性半導体記憶装置において、隣接するメモリセル積層構造間、及び、メモリセル積層構造−選択ゲート積層構造間のショートを防ぐことができる不揮発性半導体記憶装置およびその製造方法を提供する。

【解決手段】実施形態に係る不揮発性半導体記憶装置は、シリコン基板上にゲート絶縁膜、浮遊ゲート電極、電極間絶縁膜および制御ゲート電極が順に積層されたメモリセル積層構造が複数隣接して配置され、隣接する前記メモリセル積層構造間に空隙を有する不揮発性半導体記憶装置であって、前記メモリセル積層構造間のシリコン基板上に、前記メモリセル積層構造の側壁に形成されたシリコン酸化膜より厚いシリコン酸化膜が形成されている。

(もっと読む)

41 - 50 / 313

[ Back to top ]