国際特許分類[H01L23/532]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体または他の固体装置の細部 (40,832) | 動作中の装置内の1つの構成部品から他の構成部品へ電流を導く装置 (7,814) | 半導体本体上に分離できないように形成された導電層及び絶縁層の多層構造からなる外部の相互接続を含むもの (2,851) | 材料に特徴のあるもの (313)

国際特許分類[H01L23/532]に分類される特許

81 - 90 / 313

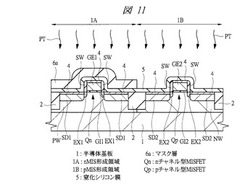

半導体装置およびその製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】半導体基板1のnMIS形成領域1Aにnチャネル型MISFETQnを、半導体基板1のpMIS形成領域1Bにpチャネル型MISFETQpを、それぞれ形成してから、nチャネル型MISFETQnおよびpチャネル型MISFETQpを覆うように引張応力の窒化シリコン膜5を形成し、nMIS形成領域1AおよびpMIS形成領域1Bの窒化シリコン膜5に紫外線照射処理を施す。その後、nMIS形成領域1Aの窒化シリコン膜5を覆いかつpMIS形成領域1Bの窒化シリコン膜5を露出するマスク層6aを形成してから、pMIS形成領域1Bの窒化シリコン膜5をプラズマ処理することで、pMIS形成領域1Bの窒化シリコン膜5の引張応力を緩和させる。

(もっと読む)

金属付着物の除去方法、基板処理装置、および記録媒体

【課題】有機化合物ガスによる基板処理を清浄に行うことが可能となる金属付着物の除去方法および基板処理装置を提供する。

【解決手段】金属付着物の除去方法は、金属層が形成された被処理基板を処理する処理空間を内部に有する処理容器の内部に付着した金属付着物を昇華させるように、前記処理容器内部の温度と、前記処理空間の圧力とを、制御する。

(もっと読む)

半導体発光素子

【課題】メタル電極に設けられた延伸部の表面を覆う絶縁膜の剥離が抑制された半導体素子を提供する。

【解決手段】半導体からなる活性層に積層されたn型またはp型の半導体層と、該半導体層の上に配置され接続部および延伸部を有するメタル電極と、該メタル電極の該延伸部の上面および側面を少なくとも覆う絶縁膜と、を備え、該延伸部はメタル多層膜で形成され、該メタル多層膜は少なくとも2層の第1メタル層と、該第1メタル層と交互に積層された第2メタル層とを含み、かつ、その最上層は該第2メタル層のひとつであり、該メタル多層膜に含まれる該最上層の第2メタル層以外の第2メタル層の各々の端面が該延伸部の側面に露出して該絶縁膜と接しており、該第2メタル層を構成する第2メタル材料は該第1メタル層を構成する第1メタル材料よりも導電率は低いが該第1メタル材料よりも該絶縁膜との密着強度に優れている。

(もっと読む)

金属パターンの製造方法

【課題】簡易なプロセスでパターン欠陥を抑制することが可能な金属パターンの製造方法を提供する。

【解決手段】アルミニウムを含む金属パターン20を製造する際に、真空雰囲気下にて、気相法により、基板上にアルミニウムを含む金属膜21を成膜する工程(1)と、金属膜21の表面に酸化処理により酸化膜22を形成する工程(2)と、酸化膜22上に金属パターンに対応したレジストパターン30を形成する工程(3)と、レジストパターン30をマスクとして、金属膜21をエッチングする工程(4)とを順次実施する。工程(1)と工程(2)との間において、少なくとも工程(2)の実施直前には、基板の雰囲気を真空雰囲気とする。

(もっと読む)

半導体装置

【課題】アンダーバリアメタルに起因する応力集中を緩和し、トランジスタの特性の変動を抑制することができるパッド電極構造を備える半導体装置を得られるようにする。

【解決手段】半導体装置は、半導体基板1の上に形成された電極パッド6と、電極パッド6の上に形成され、且つ、電極パッド6の一部が露出するような第1開口部を有する第1絶縁膜7と、第1絶縁膜の上に形成され、且つ、第1開口部における少なくとも一部が露出するような第2開口部を有する第2絶縁膜8と、第2絶縁膜8及び電極パッド6の上に形成されたアンダーバリアメタル10とを備えている。アンダーバリアメタル10は、第2絶縁膜8の表面における第2開口部の外側である第1領域と電極パッド6の表面における第2開口部の内側である第2領域とにより挟まれる第3領域により分離されている。

(もっと読む)

成膜装置および成膜方法

【課題】銅めっき工程の電極に用いるCu堆積膜による貫通孔開口の閉塞状態を適切に制御できる成膜装置を提供する。

【解決手段】成膜装置100は、貫通孔が形成された基板34Bおよび銅放出源35Bを格納する真空チャンバ30と、真空チャンバ30内を所定の真空度に減圧する真空ポンプ36と、基板34Bに印加する電力を発生する電源80と、基板34Bおよび銅放出源35B間の距離の設定に用いる駆動機構と、を備える。銅放出源35Bから放出された銅材料を基板34Bの一方の主面に堆積させ、主面における貫通孔の開口を銅材料からなる堆積膜によって閉塞させるとき、堆積膜による開口の閉塞状態が、上記距離および上記電力に基づいて調整される。

(もっと読む)

半導体装置及びその製造方法

【課題】 対象セルのワード線に隣接するワード線の電位の影響に伴う対象セルのビット線への電界を緩和する。

【解決手段】 半導体基板100に形成され、半導体素子101を形成するための活性領域と、半導体基板100内に形成され、活性領域を分離するための素子分離領域(STI102、NF104)と、素子分離領域(STI102、NF104)内に設けられた空洞部105を有する半導体装置。

(もっと読む)

半導体装置およびその製造方法

【課題】良好なエアギャップを有する半導体装置およびその製造方法を提供する。

【解決手段】実施形態の半導体装置の製造方法は、基体上にライン・アンド・スペース構造を形成する工程と、前記ライン・アンド・スペース構造のラインの側壁および上面に絶縁膜材料で第1の膜を成膜する工程と、前記第1の膜を選択的に除去して前記ライン構造の頂面を露出させる工程と、前記ライン・アンド・スペース構造を跨ぐ第2の膜を塗布成膜法により成膜する工程と、前記第2の膜を熱処理により硬化させる工程と、を持つ。前記第1の膜の厚さは前記スペースの幅の1/2未満であり、前記第2の膜は、前記第1の膜に対する濡れ性が悪い材料で前記ライン・アンド・スペース構造を覆うことにより成膜される。

(もっと読む)

成膜装置及び成膜方法

【課題】 タングステン膜を成膜する際に半導体ウェーハがエッチングされることを抑制する成膜装置及び成膜方法を提供することである。

【解決手段】 実施形態に係る成膜装置は、半導体ウェーハを載置するためのステージと、前記ステージ上に載置される半導体ウェーハの周縁部を覆うように配置されるエッジカット部を備え、前記半導体ウェーハ上にタングステン膜を成膜する。前記エッジカット部は、前記半導体ウェーハの周縁部と接触可能に設けられた第1のエッジカット部と、前記第1のエッジカット部に接続され、前記半導体ウェーハと実質的に垂直な方向に上下動可能な接続部と、前記接続部に接続され、前記接続部の上下動により前記半導体ウェーハの内側面に当接するように配置された第2のエッジカット部と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】絶縁膜上に下地金属層と上部金属層からなる配線を備えた半導体装置において、下地金属層のサイドエッチングによる絶縁膜と上部金属層との密着性の劣化を抑制することができる半導体装置、及び、その製造方法を提供する。

【解決手段】配線本体16が形成される絶縁膜14の上面には、配線本体16のパターンに対応し、かつ、絶縁膜14の上面から所定の深さの凹部14aが設けられ、当該凹部14aを含む絶縁膜14上面に、配線の一部であり、かつ、密着層であるチタン薄膜15を介して配線本体16が設けられている。凹部14aの幅は、配線本体16の幅よりも狭くなるように設定される。チタン薄膜15は配線本体16の配線幅よりも狭く形成されている。

(もっと読む)

81 - 90 / 313

[ Back to top ]